# Εθνικό Μετσόβιο Πολυτεχνείο Σχολή Ηλεκτρολόγων Μηχανικών και Μηχανικών Υπολογιστών Τομέας Τεχνολογίας Πληροφορικής και Υπολογιστών

# A Test Suite for Model Checking Persistent Memory Programs

$\Delta I\Pi \Lambda \Omega MATIKH EP\Gamma A\Sigma IA$

ΣΠΥΡΙΔΩΝ ΠΑΥΛΑΤΟΣ

Επιβλέπων: Κωνσταντίνος Σαγώνας

Αν. Καθηγητής Ε.Μ.Π.

# Εθνικό Μετσόβιο Πολυτεχνείο Σχολή Ηλεκτρολόγων Μηχανικών και Μηχανικών Υπολογιστών Τομέας Τεχνολογίας Πληροφορικής και Υπολογιστών

# A Test Suite for Model Checking Persistent Memory Programs

#### ΔΙΠΛΩΜΑΤΙΚΉ ΕΡΓΑΣΙΑ

#### ΣΠΥΡΙΔΩΝ ΠΑΥΛΑΤΟΣ

Επιβλέπων : Κωνσταντίνος Σαγώνας Αν. Καθηγητής Ε.Μ.Π.

Εγκρίθηκε από την τριμελή εξεταστική επιτροπή την 25η Ιουλίου 2022.

Κωνσταντίνος Σαγώνας Νικόλαος Παπασπύρου Γεώργιος Γκούμας Αν. Καθηγητής Ε.Μ.Π. Καθηγητής Ε.Μ.Π. Αν. Καθηγητής Ε.Μ.Π.

| Σπυρίδων Παυλάτος<br>Διπλωματούχος Ηλεκτρολόγος Μηχανικός και Μηχανικός Υπολογιστών Ε.Μ.Π.                                                                                                                                                                                                                                                                                                                                                    |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ·                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| ·                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Διπλωματούχος Ηλεχτρολόγος Μηχανικός και Μηχανικός Υπολογιστών Ε.Μ.Π.                                                                                                                                                                                                                                                                                                                                                                         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Commission (a) Same (Sam Ham) (and 2002)                                                                                                                                                                                                                                                                                                                                                                                                      |

| Copyright © Σπυρίδων Παυλάτος, 2022.<br>Με επιφύλαξη παντός δικαιώματος. All rights reserved.                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Απαγορεύεται η αντιγραφή, αποθήκευση και διανομή της παρούσας εργασίας, εξ ολοκλήρου ή τμήματος αυτής, για εμπορικό σκοπό. Επιτρέπεται η ανατύπωση, αποθήκευση και διανομή για σκοπό μη κερδοσκοπικό, εκπαιδευτικής ή ερευνητικής φύσης, υπό την προϋπόθεση να αναφέρεται η πηγή προέλευσης και να διατηρείται το παρόν μήνυμα. Ερωτήματα που αφορούν τη χρήση της εργασίας για κερδοσκοπικό σκοπό πρέπει να απευθύνονται προς τον συγγραφέα. |

Οι απόψεις και τα συμπεράσματα που περιέχονται σε αυτό το έγγραφο εκφράζουν τον συγγραφέα και δεν πρέπει να ερμηνευθεί ότι αντιπροσωπεύουν τις επίσημες θέσεις του Εθνικού Μετσόβιου

Πολυτεχνείου.

## Περίληψη

Οι τελευταίες εξελίξεις στις τεχνολογίες μνήμης έχουν φέρει στο επίχεντρο την Επίμονη Μνήμη (ΕΜ), η οποία προσφέρει επιδόσεις συγκρίσιμες με τις DRAM και πρόσβαση σε επίπεδο byte, ενώ παράλληλα είναι μη πτητική, δηλαδή τα δεδομένα της παραμένουν και μετά τη διακοπή παροχής ηλεκτρικού ρεύματος. Για να εξασφαλίσει κανείς την ορθότητα προγραμμάτων σε ΕΜ, οι σύγχρονες αρχιτεκτονικές, όπως η Intel x86, προσφέρουν ειδικές εντολές που γράφουν (flush) τα δεδομένα των πτητικών cache στην κύρια μνήμη. Αυτές οι εντολές δημιουργούν συγκεκριμένες σειρές εγγραφής στην ΕΜ. Ο φορμαλισμός αυτών των σειρών δίνεται από τα μοντέλα επίμονης μνήμης και καθορίζει τις επιτρεπτές καταστάσεις του συστήματος μετά από κάποια αποτυχία του.

Αυτή η εργασία αναπτύσσει μία σουίτα ελέγχου για προγράμματα ΕΜ. Η σουίτα αυτή περιλαμβάνει litmus tests και tests σε δομές δεδομένων. Τα litmus tests στοχεύουν στον έλεγχο της ορθότητας του εργαλείου που χρησιμοποιείται για την επαλήθευση ορθότητας του προγράμματος. Στην εργασία αυτή χρησιμοποιούμε το εργαλείο PerSeVerE, το οποίο υλοποιεί τεχνική ελέγχου μοντέλου για ΕΜ και βρίσκεται σε διαρκή ανάπτυξη. Μέσω των litmus tests καταφέραμε να βρούμε μία εσωτερική αστοχία του PERSEVERE, εξαιτίας της οποίας δεν μπορούσε να μοντελοποιηθεί σωστά το Px86 μοντέλο επίμονης μνήμης. Το γεγονός αυτό αναφέρθηκε στους δημιουργούς του PerSeVerE, οι οποίοι πρόσθεσαν επιπλέον υποστηρίξη στον πυρήνα του εργαλείου. Τα tests σε δομές δεδομένων στοχεύουν στον έλεγχο ορισμένων υλοποιήσεων δομών δεδομένων χωρίς κλειδώματα, καθώς και σε συγκεκριμενούς μετασχηματισμούς αυτών από την πρόσφατη βιβλιογραφία που μετατρέπουν αυτές τις δομές σε ανθεκτικώς γραμμικοποιήσιμες (durably linearizable). Μέσω της σουίτας μας μπορέσαμε να ελέγξουμε ότι οι βασικές εκδοχές των δομών αυτών δεν ήταν ανθεκτικές σε συγκρούσεις, ενώ οι μετασχηματισμοί τους περνάνε επιτυχώς τους ελέγχους μας. Επίσης, πειραματιστήκαμε με εξάλειψη ορισμένων flush εντολών των μετασχηματισμών, το οποίο οδήγησε σε παραβάσεις ορθότητας. Αυτό σημαίνει ότι οι εντολές αυτές είναι απαραίτητες για να εξασφαλίσουν την ορθότητα των δομών ως προς τις αποτυχίες συστήματος. Θεωρούμε ότι η σουίτα ελέγχου μας μπορεί να χρησιμοποιηθεί ως οδηγός για το πως να χρησιμοποιηθούν εργαλεία ελέγχου μοντέλου σε ΕΜ για την επαλήθευση ορθότητας ανθεκτικών δομών δεδομένων και βιβλιοθηκών, καθώς και ως σημεία αναφοράς για την επίδοση αυτών των εργαλείων.

## Λέξεις κλειδιά

Επίμονη μνήμη, Μοντέλα μνήμης, Συνέπεια μνήμης, Τεχνικές ελέγχου μοντέλου, Επαλήθευση ορθότητας λογισμικού, Δομές δεδομένων χωρίς κλειδώματα

### Abstract

The latest advances in memory technologies have brought Persistent Memory to the spotlight. Persistent Memory (PM) provides DRAM-like performance and byte-addressability, while preserving its content in case of a crash (non-volatility). To ensure correctness of programs targeting PM, memory architectures, like Intel's x86, have introduced new instructions that flush the contents of the volatile caches to the persistent domain. These instructions induce certain persist orderings, which are formalized by persistency memory models and define the allowed behaviours of the system after a crash.

This thesis develops a test suite for PM programs, consisting of both litmus and data structure tests. Litmus tests aim to check the sanity of the tool used for verification. In our case, we used Persevere, which is a persistency model checking tool under current development. Through our tests, we were able to pinpoint an internal inability of Persevere to support the Px86 memory model, which led its developers to provide additional support in the tool's core. The data structure tests try to test various implementations of lock-free data structures, as well as some adaptations and transformations found in recent literature that turn these implementations into durable linearizable ones. With our test suite, we were able to check that the original implementations of these data structures were not durably linearizable. On the other hand, the durable versions of the data structures pass our checks. Furthermore, we experimented with eliminating explicit flush instructions in these versions, which led to durably linearizability violations and therefore proving the necessity of these instructions to ensure durable linearizability. Our test suite can be used as a guideline for how to use model checking to verify durable data structures and persistent libraries, and can serve as a benchmark for persistency model checking tools.

## Key words

Persistent Memory, Memory models, Memory consistency, Model checking, Software verification, Lock-free data structures

## Ευχαριστίες

Ευχαριστώ θερμά τον επιβλέποντα καθηγητή αυτής της διπλωματικής, κ. Κωστή Σαγώνα, για τη συνεχή καθοδήγηση κατά τη διάρκεια της εκπόνησής της. Οι συμβουλές και οι κατευθύνσεις, που μου έδωσε, αποδείχθηκαν καίριες για την πορεία της έρευνας. Καθοριστική υπήρξε επίσης η συνεισφορά του Μιχάλη Κοκολογιαννάκη, υποψήφιου διδάκτορα στο Max Planck Institute for Software Systems, όπως και του επιβλέποντα καθηγητή του κ. Βίκτωρα Βαφειάδη. Φυσικά ευχαριστώ και τα υπόλοιπα μέλη της εξεταστικής επιτροπής, κ. Νίκο Παπασπύρου και κ. Γιώργο Γκούμα, όχι μόνο γιατί αποτέλεσαν μέλη αυτής, αλλά και γιατί μου κίνησαν το ενδιαφέρον να ασχοληθώ με τις Γλώσσες Προγραμματισμού και τα Υπολογιστικά Συστήματα μέσω της διδασκαλίας των μαθημάτων τους.

Ευχαριστώ, επίσης, τους κοντινούς μου φίλους που συνείσφεραν, ώστε να περάσουν τα χρόνια των σπουδών μου στο Ε.Μ.Π. ευχάριστα και επικοδομητικά. Ιδιαίτερη μνεία θα ήθελα να δώσω στους συμφοιτητές μου Αλέξανδρο Γ., Κωνσταντίνο Μ., Νικολέτα Η., Ιάσονα Ν., Χαρίτωνα Χ., Μαριλένα Ν.Π., Νίκο Υ., αλλά και τον παιδικό μου φίλο Νίκο Π., ο οποίος ήταν πάντα δίπλα μου και με στήριζε σε όσες δυσκολίες αντιμετώπισα.

Τέλος, ο,τίδηποτε έχω καταφέρει μέχρι στιγμής δε θα ήταν δυνατό χωρίς τη διαρκή υποστήριξη που μου παρείχε η μητέρα μου. Ήταν πάντα εκεί, όταν την χρειαζόμουν, και την ευχαριστώ μέσα από την καρδιά μου για αυτό.

Σπυρίδων Παυλάτος, Αθήνα, 25η Ιουλίου 2022

# Περιεχόμενα

| П  | ερίλη            | ηψη .   |           |           |        |       |       |      |      |      |      |     | <br>• | <br>• | <br> | • | <br>Ę  |

|----|------------------|---------|-----------|-----------|--------|-------|-------|------|------|------|------|-----|-------|-------|------|---|--------|

| Al | ostra            | ict     |           |           |        |       |       |      |      |      |      |     |       |       | <br> |   | <br>7  |

| Ει | νχαρ             | ιστίες  |           |           |        |       |       |      |      |      |      |     |       |       | <br> |   | <br>(  |

| П  | εριες            | χόμεν   | α         |           |        |       |       |      |      |      |      |     |       |       | <br> |   | <br>11 |

| K  | ατάλ             | ιογος   | πινάκων   | ٠         |        |       |       |      |      |      |      |     |       |       | <br> |   | <br>13 |

| K  | ατάλ             | ιογος   | σχημάτ    | ων        |        |       |       |      |      |      |      |     |       |       | <br> |   | <br>15 |

| Ex | κτετ             | αμένη   | Ελληνι    | ιχή Πε    | ρίληψ  | þη    |       |      |      |      |      |     |       |       | <br> |   | <br>17 |

|    | Εισο             | αγωγή   |           |           |        |       |       |      |      |      |      |     |       |       | <br> |   | <br>17 |

|    | $\Sigma$ uv      | έπεια Μ | [νήμης .  |           |        |       |       |      |      |      |      |     |       |       | <br> |   | <br>18 |

|    | Έλε              | γχος Μ  | Ιοντέλου  |           |        |       |       |      |      |      |      |     |       |       | <br> |   | <br>18 |

|    | Επίμ             | ιονη Μν | νήμη      |           |        |       |       |      |      |      |      |     |       |       | <br> |   | <br>19 |

|    | $\Delta$ o $\mu$ | ιές Δεδ | ομένων    |           |        |       |       |      |      |      |      |     |       |       | <br> |   | <br>21 |

|    | Σου              | ίτα Ελέ | γχου για  | Επίμονη   | η Μνήμ | μη    |       |      |      |      |      |     |       |       | <br> |   | <br>24 |

|    | Απο              | τελέσμο | ατα       |           |        |       |       |      |      |      |      |     |       |       | <br> |   | <br>28 |

|    | Επίλ             | ιογος   |           |           |        |       |       |      |      |      |      |     |       |       | <br> | ٠ | <br>30 |

| K  | είμε             | νο στο  | α αγγλι:  | κά        |        |       |       |      |      |      |      |     |       |       |      |   | 35     |

| 1. | Intr             | coduct  | ion       |           |        |       |       |      |      |      |      |     |       |       | <br> |   | <br>35 |

|    | 1.1              | Overv   | riew      |           |        |       |       |      |      |      |      |     |       |       | <br> |   | <br>35 |

|    | 1.2              | Contr   | ibutions  |           |        |       |       |      |      |      |      |     |       |       | <br> |   | <br>35 |

|    | 1.3              | Organ   | nization  |           |        |       |       |      |      |      |      |     |       |       | <br> |   | <br>36 |

| 2. | Mei              | mory (  | Consiste  | ency an   | d Mo   | del   | Che   | ecki | ng   |      |      |     |       |       | <br> |   | <br>37 |

|    | 2.1              | Memo    | ory Consi | stency.   |        |       |       |      |      |      |      |     |       |       | <br> |   | <br>37 |

|    |                  | 2.1.1   | Sequent   | tial Con  | sisten | cy (S | SC) . |      |      |      |      |     |       |       | <br> |   | <br>37 |

|    |                  | 2.1.2   |           | tore Ord  |        |       |       |      |      |      |      |     |       |       |      |   |        |

|    |                  | 2.1.3   | Axioma    | atic vers | us Op  | erati | onal  | Μe   | emoi | ry N | Iode | els |       |       | <br> |   | <br>40 |

|    | 2.2              | Verific | cation .  |           |        |       |       |      |      |      |      |     |       |       | <br> |   | <br>41 |

|    |                  | 2.2.1   | Stateles  | ss Mode   | l Chec | king  |       |      |      |      |      |     |       |       | <br> |   | <br>41 |

|    |                  | 2.2.2   | Partial   | Order F   | Reduct | ion   |       |      |      |      |      |     |       |       | <br> |   | <br>42 |

|    |                  | 2.2.3   | GENM(     | J         |        |       |       |      |      |      |      |     |       |       | <br> |   | <br>43 |

|    |                  | 2.2.4   | KATER.    |           |        |       |       |      |      |      |      |     |       |       | <br> |   | <br>43 |

| <b>3.</b> | Pers       | sistent Memory 4                        | 5 |

|-----------|------------|-----------------------------------------|---|

|           | 3.1        | Basics of Persistent Memory             | 5 |

|           | 3.2        | Memory Persistency Models               | 6 |

|           |            | 3.2.1 Epoch Persistency                 | 7 |

|           |            | 3.2.2 Persistent x86-TSO (Px86)         | 8 |

|           |            | 3.2.3 Refinements on Px86               |   |

|           | 3.3        | Model Checking for Persistency          | 1 |

| 4.        | Dat        | a Structures                            | 3 |

|           | 4.1        | Preliminaries                           | 3 |

|           | 4.2        | Lock-Free Data Structures               | 4 |

|           |            | 4.2.1 Harris' Linked-List               | 4 |

|           |            | 4.2.2 MS-Queue                          | 6 |

|           |            | 4.2.3 Skiplist                          | 7 |

|           | 4.3        | Durable Data Structures                 | 8 |

|           |            | 4.3.1 Durable Linearizability           | 8 |

|           |            | 4.3.2 Persistent Queue                  | 0 |

|           |            | 4.3.3 NVTraverse                        | 0 |

|           |            |                                         | _ |

| <b>5.</b> |            | Suite                                   | - |

|           | 5.1        | Litmus Tests                            |   |

|           | 5.2        | Data Structure Tests                    |   |

|           |            | 5.2.1 NVTraverse Tests                  |   |

|           | F 0        | 5.2.2 Persistent Queue Tests            |   |

|           | 5.3        | Flush Elimination Tests                 | U |

| <b>6.</b> | Res        | ılts                                    | 3 |

|           | 6.1        | Results of Litmus Tests                 | 3 |

|           | 6.2        | Results of Data Structure Tests         | 3 |

|           |            | 6.2.1 Results of NVTraverse Tests       | 3 |

|           |            | 6.2.2 Results of Persistent Queue Tests | 5 |

|           | 6.3        | Results of Flush Elimination Tests      | 5 |

|           | 6.4        | Comparison with Consistency Checking    | 6 |

|           |            | _                                       | _ |

| 7.        | _          | ogue                                    |   |

|           | 7.1        | Related Work                            |   |

|           | 7.2        | Conclusion and Future Work              | 9 |

| Α.        | Test       | Suite Interface                         | 1 |

| R         | Sou        | rce Code                                | 2 |

| D.        |            | Litmus Tests                            |   |

|           | B.1<br>B.2 | Data Structure Tests                    |   |

|           |            | Flush Elimination Tests                 |   |

|           | ט.ט        | I tush Emiliation 16565                 | J |

| Bi        | bliog      | raphy                                   | 9 |

# Κατάλογος πινάκων

| 0.1          | Αποτελέσματα της επάληθευσης ορθότητας μικρών προγραμμάτων                                   | 28       |

|--------------|----------------------------------------------------------------------------------------------|----------|

| 0.2          | Αποτελέσματα της επάληθευσης ορθότητας για το NVTraverse                                     | 29       |

| 0.3          | Αποτελέσματα της επάληθευσης ορθότητας για την Persistent Queue                              | 29       |

| 0.4          | Αποτελέσματα της επάληθευσης ορθότητας για το NVTraverse με αφαίρεση ορισμένων flush εντολών | 30       |

| 0.5          | $\Sigma$ ύγχριση ελέγχου συνέπειας και επιμονής                                              | 3        |

| Πίναχ        | ες στο αγγλικό κείμενο                                                                       |          |

| Πίναχ        | ες στο αγγλικό κείμενο                                                                       |          |

| Πίναχ<br>6.1 |                                                                                              | 7:       |

|              | Results for litmus tests.  Results for NVTraverse tests.                                     | 7;<br>7: |

| 6.1          | Results for litmus tests                                                                     | -        |

| 6.1<br>6.2   | Results for litmus tests                                                                     | 7        |

# Κατάλογος σχημάτων

| 0.1               | Απλό αχολουθιαχό πρόγραμμα                                                   |

|-------------------|------------------------------------------------------------------------------|

| 0.2               | Αρχική κατάσταση της λίστας με τους κόμβους $n_0$ και $n_3$                  |

| 0.3               | Κατάσταση της λίστας τη στιγμή πριν το crash                                 |

| 0.4               | Έξοδος του PerSeVerE για το WW litmus test                                   |

| 0.5               | Litmus test μεταφοράς μηνύματος                                              |

|                   |                                                                              |

| Σχήμο             | ιτα στο αγγλικό κείμενο                                                      |

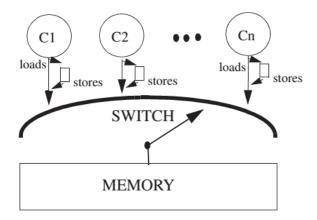

| 2.1               | Modeling Sequential Consistency with a switch                                |

| 2.2               | Modeling TSO with a switch and store buffers.                                |

| 2.3               | Store buffering litmus test showing the difference between SC and TSO        |

| 2.4               | Restoring SC with the use of mfence in SB                                    |

| 2.5               | N threads performing a write to some variables                               |

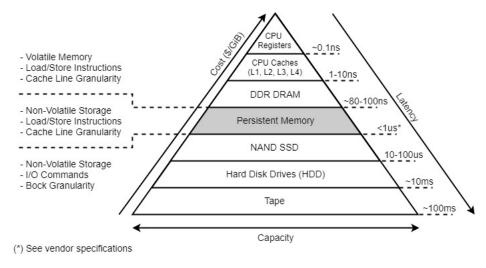

| 3.1               | Memory-storage hierarchy with the newly introduced Persistent Memory layer   |

| $\frac{3.1}{3.2}$ | Simple sequential program                                                    |

| 3.3               | Example of pfence instruction                                                |

| 3.4               | Px86 storage subsystem                                                       |

| 3.5               | Simple sequential programs showcasing the difference of the explicit persist |

| 0.0               | instructions of Intel's x86                                                  |

| 3.6               | Adding an sfence; instruction after flush <sub>opt</sub>                     |

| 4.1               |                                                                              |

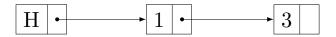

| $\frac{4.1}{4.2}$ | Initial state of linked-list                                                 |

| 4.2               | Marking the <i>next</i> field of the deleted node                            |

| $\frac{4.3}{4.4}$ | Example of an MS-Queue                                                       |

| $\frac{4.4}{4.5}$ | Empty queue                                                                  |

| 4.6               | Dequeue and enqueue concurrently on an empty queue                           |

| $\frac{4.0}{4.7}$ | Example of skiplist                                                          |

| 4.8               | Inserting a node to a skiplist                                               |

| 4.9               | Initial list containing $n_0$ and $n_3$                                      |

| 4.10              |                                                                              |

|                   |                                                                              |

| 5.1               | Output of PerSeverE for the WW litmus test                                   |

| 5.2               | Output of PERSEVERE for the WFW litmus test                                  |

| 5.3               | Message passing litmus test                                                  |

| 5.4               | CAS-based locking litmus test                                                |

| Λ 1               | Error graph for III litmus tost                                              |

# Εκτεταμένη Ελληνική Περίληψη

Η κύρια γλώσσα της παρούσας διπλωματικής εργασίας είναι η αγγλική, κυρίως για λόγους προσβασιμότητας και απόδοσης των τεχνικών όρων. Στην εκτεταμένη ελληνική περίληψη θα συνοψίσουμε το περιεχόμενό της, δίνοντας έμφαση στους βασικούς ορισμούς, τις μεθοδολογίες που ακολουθήθηκαν και τα αποτελέσματα που πήραμε. Η δομή της ενότητας αυτής είναι σε ένα προς ένα αντιστοίχηση με το αγγλικό κείμενο.

#### Εισαγωγή

Ένα από τα πιο ελπιδοφόρα τεχνολογικά επιτεύγματα των τελευταίων ετών στον τομέα της αρχιτεκτονικής υπολογιστών είναι η εισαγωγή της Επίμονης Μνήμης (ΕΜ). Η ΕΜ στοχεύει στην αντικατάσταση των παραδοσιακών DRAM, ενώ είναι μη πτητική, δηλαδή διατηρεί το περιεχόμενό της μετά από διακοπή ρεύματος, όπως κάνουν οι δίσκοι.

Ωστόσο, το να γράψει κανείς ορθά προγράμματα για EM εμφανίζει αρκετές δυσκολίες. Για παράδειγμα, μπορούν να συμβούν αποτυχίες συστήματος (system crashes) οποιαδήποτε στιγμή κατά την εκτέλεση του προγράμματος, γεγονός που μπορεί να οδηγήσει σε ασυνεπείς καταστάσεις της μνήμης κατά τη διάρκεια της διαδικασίας ανάκτησης (recovery) της κατάστασης του προγράμματος. Συνεπώς, οι προγραμματιστές πρέπει να κατανοήσουν πολύ προσεκτικά τις αναμενόμενες συμπεριφορές των προγράμματών τους ως προς τα πιθανά σφάλματα, αλλά και να χρησιμοποιήσουν ειδικές εντολές (π.χ. flush) οι οποίες γράφουν τα δεδομένα των caches στην ΕΜ. Οι συμπεριφορές της ΕΜ μπορούν να μοντελοποιηθούν με τη χρήση των μοντέλων επιμονής (persistency models), τα οποία καθορίζουν τη σειρά με την οποία γράφονται τα δεδομένα στην επίμονη μνήμη.

Σε αυτή την εργασία, θα συζητήσουμε πώς μπορούν να χρησιμοποιηθούν τα μοντέλα επιμονής σε συνδυασμό με μεθόδους ελέγχου μοντέλου (model checking), οι οποίες είναι πολύ ισχυρές τεχνικές επαλήθευσης λογισμικού, προκειμένου να ελέγξουμε την ορθότητα διαφόρων προγραμμάτων ΕΜ. Ο έλεγχος μοντέλου για ΕΜ εισάγει νέες προκλήσεις, όπως το γεγονός ότι ένα σφάλμα μπορεί να συμβεί οποιαδήποτε στιγμή κατά τη διάρκεια του προγράμματος. Αυτό οδηγεί σε πολύ μεγαλύτερο χώρο καταστάσεων από ό,τι τα ταυτόχρονα προγράμματα χωρίς crashes. Θα χρησιμοποιηθεί το εργαλείο PerseVere για να ελέγξουμε προγράμματα ΕΜ κάτω από το Px86 μοντέλο επιμονής.

Η κύρια συνεισφορά της εργασίας είναι η δημιουργία μίας σουίτας ελέγχου προγραμμάτων επίμονης μνήμης. Στη σουίτα αυτήν περιλαμβάνονται μικρά συνθετικά προγράμματα (litmus tests) με σκοπό τον έλεγχο της ορθότητας του εργαλείου, αλλά και προγράμματα για δομές δεδομένων χωρίς κλειδώματα, για τα οποία χρησιμοποιήσαμε τόσο τις απλές ταυτόχρονες υλοποιήσείς τους, όσο και καινούριες παραλλαγές τους τους, οι οποίες είναι ανθεκτικώς γραμμικοποιήσιμες (durably linearizable). Η ανθετική γραμμικοποιησιμότητα είναι το βασικό κριτήριο ορθότητας για δομές δεδομένων στην ΕΜ και μέσω της σουίτας μας επιβεβαιώσαμε ότι οι απλές εκδοχές των δομών αυτών δεν είναι ανθεκτικώς γραμμικοποιήσιμες, αλλά και ότι η αφαίρεση flush εντολών από τις παραλλαγές των δομών οδηγεί σε παραβάσεις ορθότητας.

Εκτός από τα πειραματικά αποτελέσματα που παρουσιάζονται σε αυτήν τη διπλωματική εργασία με χρήση της τρέχουσας σουίτας, θεωρούμε ότι η σουίτα μας μπορεί να αποτελέσει οδηγό για την χρήση εργαλείων ελέγχου μοντέλου στην ΕΜ με σκοπό την επαλήθευση ανθεκτικών δομών και βιβλιοθηκών, αλλά και ως σημείο αναφοράς για τη σύγκριση τέτοιου είδους εργαλείων.

## Συνέπεια Μνήμης

Τα σύγχρονα υπολογιστικά συστήματα χρησιμοποιούν πολλαπλούς πυρήνες με σκοπό την αύξηση της επίδοσής τους. Το πιο συνηθισμένο μοντέλο μνήμης σε αυτά τα συστήματα είναι η κοινή μνήμη, δηλαδή τα διάφορα νήματα δρουν πάνω στις ίδιες θέσεις μνήμης [Adve96]. Το ερώτημα που εύλογα γεννάται είναι: ποια είναι η σειρά με την οποία τα διάφορα νήματα βλέπουν τα αποτελέσματα της εκτέλεσης των υπολοίπων νημάτων; Η απάντηση δίνεται από τα μοντέλα συνέπειας (consistency models) με βάση τα οποία μπορεί κανείς να προσδιορίσει τα αποτελέσματα ενός πολυνηματικού προγράμματος.

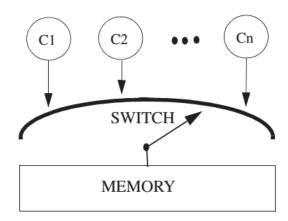

Ένα από τα βασικότερα μοντέλα συνέπειας και ίσως αυτό που βρίσκεται πιο κοντά στην αντίληψη των προγραμματιστών για πολυνηματικά προγράμματα είναι η Ακολουθιακή Συνέπεια (Sequential Consistency) ο ορισμός της οποίας έχει δοθεί από τον Leslie Lamport [Lamp79] ως εξής.

Ορισμός. (Ακολουθιακή Συνέπεια) Ένα πολυπύρηνο σύστημα είναι ακολουθιακά συνεπές εάν το αποτέλεσμα κάθε εκτέλεσης ενός προγράμματος είναι το ίδιο με το να έχουν εκτελεστεί όλες οι λειτουργίες ακολουθιακά (δηλαδή να περιμένει η μία εντολή να ολοκληρωθεί η προηγούμενη) και να διατηρείται η σειρά του προγράμματος για κάθε επεξεργαστή.

Ουσιαστικά, η Ακολουθιακή Συνέπεια εξασφαλίζει ότι υπάρχει μία ολική διάταξη των load και των store εντολών, την οποία "βλέπουν" όλα τα νήματα ταυτόχρονα με τον ίδιο τρόπο. Το πρόβλημα με την Ακολουθιακή Συνέπεια είναι ότι πολύ περιοριστική, καθώς κάθε στιγμή μπορεί να εκτελείται μόνο μία έντολη. Χάνεται, δηλαδή, ο παραλληλισμός από τη χρήση πολλών πυρήνων.

Για να αντιμετωπιστεί αυτό το φαινόμενο, έχουν προταθεί πιο χαλαρά μοντέλα συνέπειας, όπως η Ολική Σειρά Αποθήκευσης (TSO - Total Store Ordering). Αυτό το μοντέλο συνέπειας εισάγει ειδικούς store buffers σε κάθε πυρήνα, μέσω των οποίων "κρύβεται" η καθυστέρηση των stores. Τα loads μπορούν να εκτελούνται πριν ολοκληρωθούν προήγουμενα κατά σειρά προγράμματος writes, χρησιμοποιώντας τον buffer του πυρήνα τους για να διαβάζουν τις τιμές των stores. Αυτό, όμως, έχει ως αποτέλεσμα να είναι επιτρεπτές περισσότερες συμπεριφορές σε σχέση με το SC μοντέλο. Για την αποφυγή τέτοιων συμπεριφορών είναι απαραίτητη η χρήση fence εντολών. Το TSO μοντέλο χρησιμοποιείται ευρέως από σύγχρονες αρχιτεκτονικές, όπως η x86 της Intel.

Οι παραπάνω περιγραφές των μοντέλων συνέπειας έγιναν με χρήση λειτουργικής σημασιολογίας, δηλαδή κάναμε μία αφαίρεση του συστήματος χρησιμοποιώντας ιδανικά δομικά στοιχεία, όπως τους store buffers, για να περιγράψαμε πως το σύστημα μεταβαίνει από μία κατάσταση στην επόμενη.

Υπάρχει, όμως, και μία διαφορετική προσέγγιση για να εκφραστούν τα μοντέλα συνέπειας με χρήση αξιωματικής σημασιολογίας [Algl12]. Συγκεκριμένα, ορίζονται σχέσεις μεταξύ των διαφόρων λειτουργιών της μνήμης και τίθενται συγκεκριμένοι περιορισμοί σε αυτές τις σχέσεις. Τα αξιωματικά μοντέλα χρησιμοποιούν πρακτικά έννοιες σχεσιακής άλγεβρας και οι περιορισμοί που τίθενται δημιουργούν ένα σύνολο αξιωμάτων, το οποίο ορίζει τις συμπεριφορές που είναι συνεπείς με το εκάστοτε μοντέλο.

## Έλεγχος Μοντέλου

Η διαδικασία της επαλήθευσης ορθότητας ενός προγράμματος αναφέρεται στη μαθηματική απόδειξη ότι το πρόγραμμα είναι σύμφωνο με κάποιο κριτήριο ορθότητας. Μία ευρέως χρησιμοποιούμενη τακτική σε αυτό το πεδίο είναι ο έλεγχος μοντέλου (model checking), δηλαδή η συστηματική εξευρεύνηση του χώρου καταστάσεων του προγράμματος και η επαλήθευση του κριτηρίου ορθότητας σε κάθε κατάσταση.

Οι πρώτες προσεγγίσεις για τον έλεγχο μοντέλου αποθήκευαν τις καταστάσεις που έχουν επισκεφθεί, για να μην τις ξαναεπισκεφθούν στο μέλλον. Αυτό, όμως, είναι προβληματικό, καθώς

οι καταστάσεις αυτές μπορεί να χρειάζονται πολύ μεγάλο αριθμό στοιχείων του συστήματος για να προσδιοριστούν, όπως τα περιεχόμενα της μνήμης, των καταχωρητών κ.λπ. Τη λύση σε αυτό το πρόβλημα δίνουν οι τεχνικές του ελέγχου μοντέλου χωρίς κατάσταση (SMC - Stateless Model Checking), οι οποίες δεν χρειάζεται να αποθηκεύουν αυτές τις καταστάσεις.

Όμως, αχόμα και οι τεχνικές ελέγχου μοντέλου χωρίς κατάσταση παραμένουν ευάλωτες στο μεγαλύτερο πρόβλημα των πολυνηματικών προγραμμάτων, το οποίο είναι η εκθετική (ή και χειρότερη) αύξηση του αριθμού των καταστάσεων ως προς τον αριθμό των νημάτων και το μήκος του προγράμματος. Για να μειωθεί ο αριθμός των εκτελέσεων των εργαλείων ελέγχου μοντέλων χωρίς κατάσταση χρειάζεται κανείς να παρατηρήσει ότι πολλές από αυτές τις εκτελέσεις είναι ισοδύναμες, δηλαδή οδηγούν στις ίδιες καταστάσεις. Για παράδειγμα, αν αλλάξει η σειρά από δύο διαδοχικά loads, το καθένα σε διαφορετική μεταβλητή, το αποτέλεσμα ενός προγράμματος θα παραμείνει το ίδιο. Τέτοιου είδους αναμίξεις εντολών ονομάζονται ισοδύναμες και το SMC χρειάζεται να εξερευνήσει μόνο μία από αυτές.

Οι τεχνικές που εντοπίζουν τέτοιες κλάσεις ισοδυναμίας εκτελέσεων ενός προγράμματος με σκοπό τη μείωση των συνολικών καταστάσεων καλούνται Partial Order Reduction (POR) (Ελάττωση βασισμένη σε Μερικές Διατάξεις). Οι πρώιμες τεχνικές ελάττωσης βασισμένες σε μερικές διατάξεις υπολόγιζαν στατικά τις κλάσεις ισοδυναμίας, ενώ οι πιο σύγχρονες τέτοιες τεχνικές αναφέρονται ως τεχνικές Δυναμικής Ελάττωσης βασισμένη σε Μερικές Διατάξεις (DPOR - Dynamic Partial Order Reduction) [Flan05, Abdu14] διότι υπολογίζουν τις κλάσεις ισοδυναμίας δυναμικά κατά την εκτέλεση του προγράμματος με χρήση ενός δρομολογητή χρόνου εκτέλεσης.

Ένα σύγχρονο και πολύ αποδοτικό SMC εργαλείο, που χρησιμοποιεί μία μορφή DPOR, είναι το GenMC [Koko21b]. Το συγκεκριμένο εργαλείο κατασκευάζει σταδιακά ένα γράφο εκτέλεσης του προγράμματος και ελέγχει σε κάθε βήμα αν ο γράφος είναι συνεπής σύμφωνα με τον αξιωματικό ορισμό του εκάστοτε μοντέλου συνέπειας. Η εισαγωγή των διάφορων μοντέλων στο GenMC γίνεται με τη χρήση ενός υπό ανάπτυξη εργαλείου, το οποίο ονομάζεται κατέλ. Το κατέλ δέχεται σαν είσοδο ένα αρχείο που περιγράφει με όρους σχεσιακής άλγεβρας ένα μοντέλο συνέπειας και δίνει σαν έξοδο κώδικα, ο οποίος μπορεί πολύ εύκολα να ενσωματωθεί στον πυρήνα του GenMC.

## Επίμονη Μνήμη

Οι εξελίξεις στις τεχνολογίες μνήμης τα τελευταία χρόνια και πιο συγκεκριμένα η ανάπτυξη της Επίμονης Μνήμης (ΕΜ) [Lee09, Kawa12] έχουν πρακτικά γεφυρώσει το χάσμα μεταξύ των ψηλότερων βαθμίδων της ιεραρχίας μνήμης (RAM, caches, καταχωρητές) και των χαμηλότερων βαθμίδων (αποθηκευτικός χώρος, π.χ. SSD, HDD). Η ΕΜ προσφέρει πρόσβαση σε επίπεδο byte, ενώ παράλληλα είναι μη πτητική, δηλαδή τα δεδομένα της παραμένουν και μετά τη διακοπή παροχής ηλεκτρικού ρεύματος. Οι επιδόσεις της, μάλιστα, είναι συγκρίσιμες με αυτές της DRAM. Αυτή τη στιγμή, η ΕΜ είναι εμπορικά διαθέσιμη από την Intel με την τεχνολογία Optane [Intel9b] και μπορεί να τοποθετηθεί μαζί με τη DRAM στο διάδρομο μνήμης ή να την αντικαταστήσει τελείως.

Η επίμονη μνήμη, όμως, δημιουργεί ορισμένες δυσκολίες για τους προγραμματιστές. Οι caches αναμένεται να παραμείνουν πτητικές, ενώ τα δεδομένα τους δεν εγγράφονται στη μνήμη αμέσως, αλλά σε κάποια μελλοντική (πιθανόν μη ντετερμινιστική) στιγμή. Ως αποτέλεσμα, τα προγράμματα ΕΜ μπορούν να οδηγήσουν τη μνήμη μετά από ένα crash σε καταστάσεις που δεν είναι επιτρεπτές από το μοντέλο συνέπειας του συστήματος, όπως δείχνουμε με το Παράδειγμα 0.1

#### Παράδειγμα 0.1: Εγγραφή δεδομένων στην ΕΜ εκτός σειράς

Ας θεωρήσουμε το ακόλουθο ακολουθιακό πρόγραμμα, όπου οι μεταβλητές  $\mathbf x$  και  $\mathbf y$  είναι αρχικοποιημένες με 0.

$$\begin{array}{l} x:=1;\\ y:=1; \end{array} \tag{WW}$$

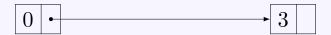

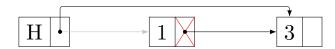

Σχήμα 0.1: Απλό ακολουθιακό πρόγραμμα.

Παρόλο που η εγγραφή στο x προηγείται της εγγραφής στο y, είναι πιθανό η γραμμή της cache του y να εγγραφεί στην EM πριν από αυτή του x. Εάν συμβεί ένα crash μετά την εγγραφή του y και πριν την εγγραφή του y, τότε είναι πιθανό κατά την ανάκτηση του προγράμματος, το y να περιέχει την τιμή y, ενώ το y να εξακολουθεί να έχει την τιμή y. Είναι σημαντικό να σημειωθεί ότι η κατάσταση της μνήμης y το μοντέλο y το μον

Όπως και με τα μοντέλα συνέπειας, έτσι και στην περίπτωση της ΕΜ, μπορούμε να ορίσουμε τα λεγόμενα μοντέλα επιμονής (persistency models) [Pell14]. Μέσω αυτών τον μοντέλων, ο προγραμματιστής μπορεί να κατανοήσει τη σειρά των εγγραφών που μπορεί να εμφανιστεί στο πρόγραμμά του, και έτσι να βγάλει συμπεράσματα για τη συμπεριφορά του προγράμματός του, αυτήν τη φορά, όμως, ως προς τα crashes.

Τα μοντέλα επιμονής μπορούν να κατηγοριοποιηθούν ως προς τη σχέση τους με τα μοντέλα συνέπειας του συστήματος, δηλαδή αν η σειρά που γίνονται οι εγγραφές στην ΕΜ είναι η ίδια με τη σειρά που ορίζεται από το μοντέλο συνέπειας. Αν οι δύο σειρές ταυτίζονται, τότε μιλάμε για αυστηρό μοντέλο επιμονής, ενώ αν είναι διαφορετικές έχουμε χαλαρό μοντέλο επιμονής. Τα χαλαρά μοντέλα χρησιμοποιούνται για να προσφέρουν καλύτερες επιδοσείς από τα αυστηρά. Μία άλλη κατηγοροποίηση των μοντέλων επιμονής είναι αν οι εγγραφές στην ΕΜ γίνονται σύγχρονα, δηλαδή την στιγμή που εκτελείται η αντίστοιχη εντολή, ή ασύγχρονα, δηλαδή αποθηκεύονται σε κάποιον επίμονο buffer και εκτελούνται αργότερα.

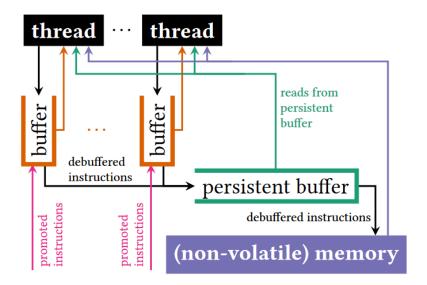

Το πιο διαδεδομένο μοντέλο επιμονής είναι το Px86 [Raad20], το οποίο μοντελοποιεί τη σημασιολογία της αρχιτεκτονικής x86 της Intel, η οποία υλοποιεί το TSO μοντέλο συνέπειας. Το Px86 είναι χαλαρό και ασύγχρονο, καθώς χρησιμοποιεί έναν καθολικό επίμονο buffer για να αποθηκεύει τις εγγραφές, όταν αυτές βγαίνουν από τον αντίστοιχο (store) buffer του εκάστοτε πυρήνα.

Η x86 αρχιτεκτονική προσφέρει τις εντολές clflush και clflushopt, οι οποίες κάνουν flush μία cache line, καθώς και την sfence, η οποία χρησιμοποιείται για να συγχρονίσει τις εγγραφές στην ΕΜ από διαφορετικά threads. Η χρήση της clflush μπορεί να αποτρέψει την μη επιθυμητή συμπεριφορά του προγράμματος WW, αν τοποθετηθεί μεταξύ των δύο εγγραφών. Όμως, λόγω της ασύγχρονης φύσης του Px86, η εντολή αυτή περιορίζει μόνο τη σειρά που μπορεί να γίνουν οι εγγραφές στην ΕΜ και όχι ότι η εγγραφή του κ στην ΕΜ θα έχει προηγηθεί της εκτέλεσης της εντολής του y.

Η ασύγχρονη φύση του μοντέλου Px86 είναι αντίθετη με την αντίληψη που έχουν οι προγραμματιστές για τη χρήση των εντολών clflush και clflushopt, καθώς και με την πρόσφατη βιβλιογραφία για την ΕΜ [Pell14, Izra16, Frie18, Frie21a, Scar20]. Το πρόβλημα αυτό έρχεται να λύσει μία πρόσφατη αναθεώρηση του Px86 μοντέλου, η οποία χρησιμοποιεί σύγχρονες εντολές και αποδεικνύεται ότι είναι ισοδύναμη με το Px86. Το μοντέλο αυτό, το οποίο ονομάζεται PTSO<sub>syn</sub> [Khyz21], χρησιμοποιεί έναν επίμονο buffer για κάθε γραμμή της cache, το οποίο οδηγεί στην έκφραση της σειράς εγγραφής στην ΕΜ ως μερική διάταξη. Οι μερικές διατάξεις

μπορούν να χρησιμοποιηθούν από εργαλεία SMC, που χρησιμοποιούν κάποια DPOR μέθοδο για την εξερεύνηση του χώρου καταστάσεων του προγράμματος. Στην εργασία αυτή θα χρησιμοποιήσουμε το εργαλείο PerseVerE [Koko21a], το οποίο έχει πρόσφατα επεκταθεί ώστε να μοντελοποιεί την αναθεωρημένη εκδοχή του μοντέλου επιμονής Px86.

Το PerseVerE χρησιμοποιεί τον πυρήνα του GenMC και προσθέτει υποστήριξη για τον έλεγχο της επιμονής. Πιο συγκεκριμένα, προσθέτει στο πρόγραμμα ένα ακόμα νήμα, το οποίο καλείται παρατηρητής ανάκτησης (recovery observer). Το νήμα αυτό εκτελείται σε κάθε βήμα της κατασκευής του γράφου εκτέλεσης, μοντελοποιώντας τη διαδικασία ανάκτησης ενός προγράμματος μετά από κάποιο crash, και ελέγχει αν τηρούνται τα αξιώματα επιμονής που ορίζονται από το μοντέλο επιμονής.

Για τη χρήση του εργαλείου, ο προγραμματιστής πρέπει να ορίσει κάποιες επίμονες μεταβλητές, οι οποίες είναι οι μόνες που επιτρέπεται να διαβαστούν κατά τη διαδικασία ανάκτησης του προγράμματος. Ο ορισμός αυτών των μεταβλητών γίνεται με χρήση της μακροεντολής \_\_VERIFIER\_persistent\_storage(). Το εργαλείο, επίσης, προσφέρει τις ακόλουθες εντολές και λειτουργίες ΕΜ:

- 1. \_\_VERIFIER\_pbarrier(), οποία χρησιμοποιείται ως "φράχτης", ο οποίος ορίζει ότι όλες οι προηγούμενες εντολές του προγράμματος θα θεωρούνται ότι έχουν εγγραφεί στην ΕΜ κατά τη διαδικασία της ανάκτησης του προγράμματος.

- 2. \_\_VERIFIER\_clflush(), η οποία δέχεται σαν παράμετρο τη διεύθυνση μίας μεταβλητής και υλοποιεί τη σημασιολογία της clflush εντολής με τη σημασιολογία του αναθεωρημένου μοντέλου Px86.

- 3. \_\_VERIFIER\_recovery routine(), η οποία είναι η συνάρτηση που περιέχει τον κώδικα που θα τρέξει κατά την ανάκτηση του προγράμματος

Για την περιγραφή του μοντέλου επιμονής χρησιμοποιείται το ΚΑΤΕR.

## Δομές Δεδομένων

Σε ένα περιβάλλον ταυτόχρονης εκτέλεσης προγραμμάτων, διάφορα νήματα μπορούν να εκτελέσουν λειτουργίες πάνω σε μια δομή δεδομένων που μοιράζεται μεταξύ τους. Κάθε λειτουργία συνδέεται με την αίτηση (request) και την απόκρισή (response) της. Μία ιστορία μπορεί να οριστεί ως μια πεπερασμένη ακολουθία των αιτήσεων και των αποκρίσεων των λειτουργιών που εκτελούνται από διάφορα νήματα στο ταυτόχρονο περιβάλλον. Μία ιστορία ονομάζεται σειριακή εάν κάθε αίτηση μίας λειτουργίας ακολουθείται αμέσως στη σειρά της ιστορίας από την απόκρισή της.

Με βάση την έννοια της ιστορίας, μπορεί να οριστεί το βασικό κριτήριο ορθότητας μίας δομής δεδομένων σε ταυτόχρονο περιβάλλον, το οποίο είναι η γραμμικοποιησιμότητα (linearizability) [Herl90]. Πιο συγκεκριμένα, μία ιστορία είναι γραμμικοποιήσιμη ανν είναι ισοδύναμη με κάποια σειριακή ιστορία. Πρακτικά, η γραμμικοποιησιμότητα σημαίνει ότι οι διάφορες λειτουργίες φαίνεται να λαμβάνουν χώρα ατομικά μέσα στο διάστημα που ορίζεται από την αίτηση και την απόκρισή τους.

Οι γραμμικοποιήσιμες δομές δεδομένων ικανοποιούν επίσης την non-blocking ιδιότητα, δηλαδή μία αίτηση κάποιας λειτουργίας δε χρειάζεται να περιμένει την ολοκλήρωση κάποιας άλλης εκρεμμής λειτουργίας. Αυτό έρχεται σε αντίθεση με τη συνήθη προσέγγιση της χρήσης κλειδωμάτων για την εξασφάλιση συγχρονισμού στις δομές δεδομένων, καθώς τα κλειδώματα μπορούν να οδηγήσουν σε αδιέξοδα (deadlocks και livelocks).

Βάση της παραπάνω ιδιότητας μπορούν να οριστούν δύο συνθήχες προόδου για ταυτόχρονες δομές δεδομένων:

**ελευθερία από κλειδώματα (lock-freedom)** Μία μέθοδος λέγεται ότι είναι ελεύθερη από κλειδώματα εάν υπάρχει κάποια εγγύηση οτί μεταξύ των εκτελούντων νημάτων, τουλάχιστον ένα θα τερματίσει σε πεπερασμένο αριθμό βημάτων.

**ελευθερία από αναμονή (wait-freedom)** Μία μέθοδος λέγεται ότι είναι ελεύθερη από αναμονή εάν εγγυάται ότι όλα τα νημάτα θα τερματίσουν σε πεπερασμένο αριθμό βημάτων. Μία μέθοδος χωρίς αναμονή είναι πάντα και χωρίς κλειδώματα, αλλά δεν ισχύει το αντίθετο.

Στην εργασία αυτή θα ασχοληθούμε με κάποιες βασικές δομές ελεύθερες από κλειδώματα, τις οποίες θα χρησιμοποιήσουμε στην πειραματική μας διαδικασία. Οι δομές δεδομένων χωρίς κλειδώματα χρησιμοποιούν εντολές, όπως την CAS (compare-and-swap), η οποία συγκρίνει με ατομικό τρόπο το περιεχόμενο μίας θέσης μνήμης με μία αναμενόμενη τιμή και αν αυτή είναι όντως η αναμενόμενη, ανανεώνει κατάλληλα την τιμή της. Χρησιμοποιώντας, λοιπόν, την CAS εντολή, οι δομές χωρίς κλειδώματα ελέγχουν συγκεκριμένους δείκτες και κόμβους της εκάστοτες δομής και σε περίπτωση που η εντολή αποτύχει ξαναρχίζουν τη μέθοδό τους από την αρχή.

Ένα βασικό παράδειγμα δομής χωρίς κλειδώματα είναι η συνδεδεμένη λίστα του Harris (Harris' linked-list) [Harr01]. Η λίστα αυτή χρησιμοποιεί τη λεγόμενη μέθοδο διαγραφής σε δύο βήματα, όπου το πρώτο βήμα μαρκάρει τον προς διαγραφή κόμβο, αφαιρώντας λογικά από τη λίστα, και το δεύτερο τον αφαιρεί και φυσικά σε κάποια μεταγενέστερη χρονική στιγμή. Η συνδεδεμένη λίστα του Harris προσφέρει μεθόδους εισαγωγής και διαγραφής με ελευθερία από κλειδώματα και αναζήτηση στοιχείου με ελευθερία από αναμονή.

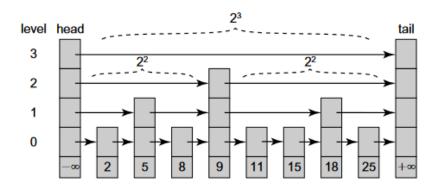

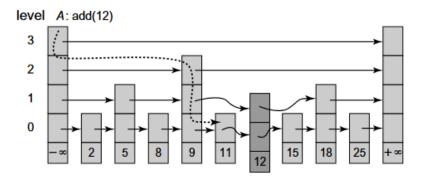

Επέκταση της συνδεδεμένης λίστας αποτελεί η δομή skiplist. Η δομή αυτή αποτελείται από απλά συνδεδεμένες λίστες πολλών επιπέδων, όπου στο χαμηλότερο επίπεδο βρίσκονται όλα τα στοιχεία της λίστας. Στα ψηλότερα επίπεδα βλέπουμε όλο και μικρότερο αριθμό κόμβων, τα οποία στοχεύουν στη γρηγορότερη αναζήτηση στοιχείων της λίστας, η οποία έχει χρονική πολυπλοκότητα  $\mathcal{O}(\log N)$ . Η εκδοχή χωρίς κλειδώματα της skiplist βασίζεται στο μηχανισμό μαρκαρίσματος της συνδεδεμένης λίστας του Harris και οι λειτουργίες της ικανοποιούν τις ίδιες συνθήκες προόδου με αυτή [Mich02b, Herl08].

Τέλος, μία ακόμη ευρέως διαδεδομένη δομή χωρίς κλειδώματα είναι η ουρά Michael-Scott (MS-Queue) [Mich96]. Η διαδικασία εισαγωγής (enqueue) και εξαγωγής (dequeue) στοιχείων από τη λίστα γίνεται από δύο σημεία πρόσβασης στη λίστα, το δείκτη head και το δείκτη tail αντίστοιχα. Η MS-Queue κάνει χρήση της CAS εντολής για να αλλάξει τους δείκτες αυτούς, όταν καλούνται οι αντίστοιχες μέθοδοι. Ιδιαίτερη προσοχή δίνεται στην περίπτωση που η λίστα είναι κενή. Οι δύο μέθοδοι enqueue και enqueue έχουν ελευθερία από κλειδώματα.

Η γραμμικοποιησιμότητα δεν μπορεί να εφαρμοστεί απευθείας στην επίμονη μνήμη λόγω των crashes. Για αυτό το λόγο έχει προταθεί μία επέκταση της, η οποία καλείται ανθεκτική γραμμικοποιησιμότητα (durable linearizability) [Izra16]. Η ανθεκτική γραμμικοποιησιμότητα επιβάλλει ότι έπειτα από ένα crash, όλες οι λειτουργίες που έχουν ολοκληρωθεί πριν από το crash θα πρέπει να έχουν εγγραφεί και στην ΕΜ και να είναι ανιχνεύσιμες κατά την ανάκτηση του προγράμματος. Μπορεί εύκολα να δειχθεί ότι οι δομές χωρίς κλειδώματα, που παρουσιάσαμε, δεν είναι ανθεκτικώς γραμμικοποιήσιμες, όπως φαίνεται στο Παράδειγμα 0.2 για την συνδεδεμένη λίστα του Harris.

# Παράδειγμα 0.2: Παραβίαση της ανθεκτικής σειριοποιησιμότητας σε μία συνδεδεμένη λίστα

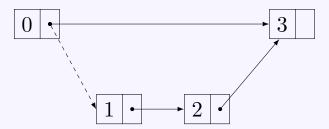

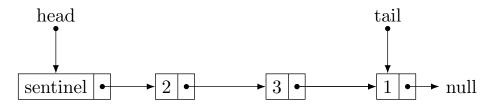

Ας θεωρήσουμε μία συνδεδεμένη λιστα αποτελούμενη από δύο κόμβους, όπου ο ένας περιέχει το κλειδί 0 (κόμβος  $n_0$ ) και ο άλλος το κλειδί 3 (κόμβος  $n_3$ ), όπως φαίνεται στο Σχήμα 0.2. Ας υποθέσουμε επίσης ότι δύο νήματα (T1 και T2) θέλουν να εισάγουν στη λίστα κόμβους με το κλειδί 1 (κόμβος  $n_1$ ) και το κλειδί 2 (κόμβος  $n_2$ ).

**Σχήμα 0.2:** Αρχική κατάσταση της λίστας με τους κόμβους  $n_0$  και  $n_3$ .

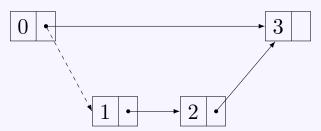

Το νήμα T1 εκτελεί μία CAS εντολή και αλλάζει το δείκτη next του κόμβου  $n_0$  προς τον κόμβο  $n_1$ , όποτε και σταματάει την εκτέλεσή του χωρις να εγγράψει τις αλλαγές στην EM. Έπειτα, το νήμα T2 ξεκινάει την εκτέλεσή του και εκτελεί μία CAS, η οποία αλλάζει το next δείκτη του κόμβου  $n_1$ , ώστε να δείχνει στον  $n_2$ . Τέλος, το T2 γράφει (με flush) τις αλλαγές στην EM και ολοκληρώνει επιτυχώς την εισαγωγή του  $n_2$ . Η κατάσταση της λίστας τη στιγμή αυτή φαίνεται στο  $\Sigma$ χήμα 0.3. Μόλις τελειώσει, όμως, την εκτέλεσή του το T2, συμβάινει ένα crash.

Σχήμα 0.3: Κατάσταση της λίστας τη στιγμή πριν το crash. Οι συνεχείς γραμμές έχουν εγγραφεί στην ΕΜ, ενώ οι διακεκομένες όχι.

Μετά το crash, τόσο ο χόμβος  $n_1$ , όσο και ο  $n_2$  έχουν χαθεί, αφού ο δείκτης από τον  $n_0$  προς τον  $n_1$  δεν έχει εγγραφεί στην EM πριν το crash. Έτσι, παρόλο που έχει ολοκληρωθεί η λειτουργία του T2 (εισαγωγή του  $n_2$ ) πριν το crash, τα αποτελέσματά του δεν μπορούν να ανιχνευθούν κατά τη διαδικασία ανάκτησης. Αυτό είναι μία παραβίαση ανθεκτικής σειριοποιησιμότητας. Ας σημειώσουμε, ότι σε περίπτωση που το νήμα T2 είχε γράψει στην EM το δείκτη από τον  $n_0$  στο  $n_1$ , τότε αυτό το παράδειγμα θα ήταν ανθεκτικώς γραμμικοποιήσιμο.

Στην πρόσφατη βιβλιογραφία έχουν προταθεί κάποιες τροποποιήσεις δομών χωρίς κλειδώματα, οι οποίες είναι ανθεκτικά γραμμικοποιήσιμες. Ένα παράδειγμα είναι η Persistent (ή Durable) Queue, η οποία είναι επέκταση της MS-Queue. Για την επίτευξη ανθεκτικότητας χρησιμοποιούνται προσεκτικά τοποθετημένες flush εντολές.

Η προσέγγιση για την επίτευξη ανθεκτικότητας της Persistent Queue προϋποθέτει πολύ καλή κατανόηση της δομής δεδομένων και πιθανότατα δεν μπορεί να γενικευτεί σε άλλες δομές. Για αυτόν το λόγο, έχουν προταθεί διάφοροι αυτόματοι μετασχηματισμοί. Ο πρώτος τέτοιος μετασχηματισμός καλείται μετασχηματισμός Izraelevitz [Izra16] και πρακτικά προσθέτει flush εντολές μετά από κάθε διάβασμα ή εγγραφή μίας μεταβλητής.

Ένας πιο αποδοτικός μετασχηματισμός είναι ο NVTraverse [Frie21a], ο οποίος μετατρέπει μία οικογένεια δομών δεδομένων ελεύθερες από κλειδώματα (στην οποία περιλαμβάνονται η συνδεδεμένη λίστα του Harris και η skiplist) σε ανθεκτικώς γραμμικοποιήσιμες με αυτόματο τρόπο.

#### Algorithm 1: Operation in a NVTraverse data structure

Ο Αλγόριθμος 1 παρουσιάζει τη λειτουργία μίας NVTraverse δομής δεδομένων, όπου με σκιασμένο χρώμα είναι οι μέθοδοι που προστίθενται για να εξασφαλίσουν την ανθεκτικότητα. Η μέθοδος ensureReachable εξασφαλίζει ότι υπάρχει ανθεκτικό μονοπάτι για τον κόμβο, στον οποίο γίνεται η εκάστοτε λειτουργία, ενώ η makePersistent κάνει flush τους αναγκαίους κόμβους του μονοπατιού, ώστε να διασφαλιστεί η ανθεκτική γραμμικοποιησιμότητα.

## Σουίτα Ελέγχου για Επίμονη Μνήμη

Η κύρια συνεισφορά αυτής της εργασίας είναι η δημιουργία μίας σουίτας ελέγχου για προγράμματα επίμονης μνήμης, η οποία αποτελείται από:

- 1. **Litmus tests**. Τα litmus tests είναι μικρά συνθετικά benchmarks, τα οποία στοχεύουν στον έλεγχο του εργαλείου για συγκεκριμένες συμπεριφορές του μοντέλου που υλοποιεί.

- 2. **Tests δομών δεδομένων**. Προσεχτικά κατασκευασμένα tests ανθεκτικών και μη δομών δεδομένων χωρίς κλειδώματα.

Ένας στόχος αυτής της σουίτας ελέγχου είναι να ελέγξει την ορθότητα και την επεκτασιμότητα του εργαλείου PerSeVere. Όπως θα δούμε σύντομα, μέσω της σουίτας μας μπορέσαμε να βρούμε μια εσωτερική αδυναμία του PerSeVere, που οδηγούσε στη λάθος μοντελοποίηση μίας συμπεριφοράς του Px86. Ένας πιο γενικός στόχος της σουίτας είναι να χρησιμοποιηθεί ως βάση για τη δημιουργία σημείων αναφοράς (benchmarks) για εργαλεία επαλήθευσης ΕΜ προγραμμάτων.

Αρχικά, τονίζουμε ότι τα tests της σουίτας είναι δύο ειδών. Στην πρώτη κατηγορία είναι αυτά τα οποία έχουν κάποιο assertion, το οποίο δεν πρέπει να παραβιάζεται σε καμία εκτέλεση. Αυτά τα tests θεωρούνται ασφαλή. Στη δεύτερη κατηγορία βρίσκονται tests στα οποία κάποιο assertion αναμένεται να αποτυγχάνει και συμβολίζονται ως μη ασφαλή. Σε αυτά το PerseVere πρέπει να εντοπίζει κάποιο σφάλμα.

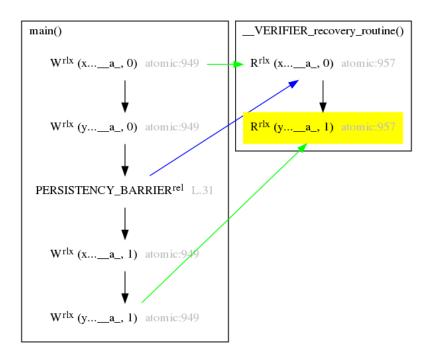

Θα ξεκινήσουμε την ανάλυση της σουίτας μας με την υλοποίηση του παραδείγματος WW, η οποία φαίνεται στο Πρόγραμμα 1. Για να ορίσουμε τις μεταβλητές x και y ως επίμονες, χρησιμοποιούμε τη μακροεντολή \_\_VERIFIER\_persistent\_storage(). Αρχικοποιούμε τις δύο μεταβλητές με 0 και εκτελούμε το επίμονο φράγμα \_\_VERIFIER\_pbarrier() για να οριστεί η αρχική κατάσταση της EM. Στη ρουτίνα ανάκτησης \_\_VERIFIER\_recovery\_routine() διαβάζουμε τις επίμονες μεταβλητές και εξετάζουμε με τη χρήση ενός assertion εάν μπορούν να πάρουν τον ανεπιθύμητο συνδυασμό  $x = 0 \land y = 1$ . Το PERSEVERE εντοπίζει παραβίαση του assertion, όπως φαίνεται και στο Σχήμα 0.4, γεγονός που σημαίνει ότι η κατάσταση αυτή γίνεται να επιτευχθεί.

```

#include <stdio.h>

2 #include <stdlib.h>

3 #include <atomic>

4 #include <pthread.h>

5 #include <assert.h>

6 #include <genmc.h>

8 #define relaxed std::memory_order_relaxed

10 __VERIFIER_persistent_storage(std::atomic_int x);

11 __VERIFIER_persistent_storage(std::atomic_int y);

13 extern "C"{

void __VERIFIER_clflush(void*);

void __VERIFIER_recovery_routine(void)

assert(!(x.load(relaxed) == 0 && y.load(relaxed) == 1));

20

return;

21 }

22

23 int main()

24 {

x.store(0, relaxed);

25

26

y.store(0, relaxed);

27

28

__VERIFIER_pbarrier();

29

x.store(1, relaxed);

30

31

y.store(1, relaxed);

32

33

return 0:

34 }

```

Πρόγραμμα 1: WW litmus test

Μέσα από τη χρήση των litmus tests, καταφέραμε να βρούμε μία εσωτερική αδυναμία του PerSeVerE. Πιο συγκεκριμένα, το πρόγραμμα που φαίνεται στο Σχήμα 0.5, ανέδειξε ότι το PerSeVerE δεν μπορούσε να μοντελοποιήσει το flush μίας μεταβλητής από διαφορετικό νήμα από αυτό που έχει γίνει η εγγραφή. Οι δημιουργοί του PerSeVerE διόρθωσαν το πρόβλημα αυτό προσθέτωντας επιπλέον υποστήριξη στον πυρήνα του εργαλείου.

Όσον αφορά τα tests για τις δομές δεδομένων, πειραματιστήκαμε αρχικά με τη συνδεδεμένη λίστα και τη skiplist. Πιο συγκεκριμένα, ελέγξαμε τρεις εκδοχές αυτών των δομών:

- 1. Τις αρχικές εκδοχές των δομών (e.g., Harris' linked-list), οι οποίες δεν είναι ανθεκτικώς γραμμικοποιήσιμες.

- 2. Το μετασχηματισμό Izraelevitz.

- 3. Το μετασχηματισμό NVTraverse.

Τα tests μας εστίασαν σε δύο άξονες:

- 1. Να δείξουμε ότι οι αρχικές εκδοχές δεν είναι πράγματι ανθεκτικώς γραμμικοποιήσιμες, ενώ οι άλλες εκδοχές περνάνε επιτυχώς τους ελέγχους μας. Για αυτό, τα tests των αρχικών εκδοχών δηλώνονται ως ασφαλή, ενώ των δύο μετασχηματισμών ως μη ασφαλή.

- 2. Να φτιάξουμε κάποια μεγάλα και περίπλοκα tests για να δούμε πως ανταποκρίνεται σε αυτά το PerSeVerE.

```

Error detected: Recovery error!

Event (1, 2) in graph:

<-1, 0> main:

(0, 1): Wrlx (x..._a_, 0) atomic:949

(0, 2): Wrlx (y..._a, 0) atomic:949

(0, 3): PERSISTENCY_BARRIERrel L.31

(0, 4): Wrlx (x..._a_, 1) atomic:949

(0, 5): Wrlx (y..._a, 1) atomic:949

(0, 6): THREAD_END

<-1, 1> __VERIFIER_recovery_routine:

(1, 1): Rrlx (x..._a, 0) [(0, 1)] atomic:957

(1, 2): Rrlx (y..._a, 1) [(0, 5)] atomic:957

Coherence:

y..._a: [ (0, 2) (0, 5) ]

x..._a: [ (0, 1) (0, 4) ]

Assertion violation: !(x.load(relaxed) == 0 && y.load(relaxed) == 1)

Number of complete executions explored: 2

Total wall-clock time: 0.04s

```

Σχήμα 0.4: Έξοδος του PerseVerE για το WW litmus test. Η έξοδος αποτελείται από το είδος του σφάλματος που εντοπίστηκε (assertion violation), την εκτέλεση που οδήγησε στο σφάλμα, τον αριθμό των εκτελέσεων που εξερεύνησε (και που μπλόκαρε) το εργαλείο, καθώς και το συνολικό χρόνο εκτέλεσης.

$$x := 42;$$

|  $a := y;$

$y := 7;$  | if  $(a \neq 0);$

$flush x;$

$z := 1;$  (2W+RFW)

Σχήμα 0.5: Litmus test μεταφοράς μηνύματος (2W+RFW). Η μεταβλητή κ γράφεται από το πρώτο νήμα και γίνεται flush από το δεύτερο.

$$((s1)|1)((or)|(iz)|(tr)) - (((pw)(+(w|d)^{+})^{+})|((w|d)^{+}(+(w|d)^{+})^{*}))$$

όπου

- το 1 αναφέρεται στη συνδεδεμένη λίστα, ενώ το s1 αναφέρεται στη skiplist

- το οr αναφέρεται στις απλές εκδοχές των δομών (π.χ. συνδεδεμένη λίστα Harris), το iz αναφέρεται στο μετασχηματισμό του Izraelevitz, ενώ το tr αναφέρεται στο μετασχηματισμό NVTraverse

- το pw σημαίνει ότι έχουν γίνει κάποιες εισαγωγές στη δομή πριν το φράγμα αρχικοποίησης

ΕΜ

- ο όρος  $+(w|d)^+$  σημαίνει ότι ένα νέο νήμα δημιουργείται, το οποίο εκτελεί έναν αυθαίρετο αριθμό από εισαγωγές ή/και διαγραφές στοιχείων στη δομή.

Για παράδειγμα, το test lor-pw+w+d ελέγχει την αρχική εκδοχή της συνδεδεμένης λίστας, έχοντας εισάγει κάποια στοιχεία πριν το φράγμα αρχικοποίησης και στη συνέχεια δημιουργούνται δύο νήματα, όπου το ένα κάνει μια εισαγωγή και το άλλο μία διαγραφή.

Για τα tests της Persistent Queue αχολουθήσαμε παρόμοια ονοματοδοσία με το NVTraverse:

```

((msq)|(dq)) - (((pe)(+(e|d)^{+})^{+})|((e|d)^{+}(+(e|d)^{+})^{*}))

```

όπου

- το msq αναφέρεται στην MS-Queue, ενώ το dq στην Durable Queue. Τα tests για την MS-Queue δηλώνονται ως μη ασφαλή, ενώ για την Durable Queue ως ασφαλή.

- pe σημαίνει ότι έχουν γίνει κάποιες εισαγωγές στη δομή πριν το φράγμα αρχικοποίησης

EM

- ο όρος  $+(e|d)^+$  σημαίνει ότι ένα νέο νήμα δημιουργείται, το οποίο εκτελεί έναν αυθαίρετο αριθμό από εισαγωγές (enqueues) ή/και διαγραφές (dequeues) στοιχείων στη δομή.

Πέρα από τον απλό έλεγχο των δομών, πειραματιστήκαμε επίσης και με την αφαίρεση εντολών flush από τον κώδικα του NVTraverse. Σκοπός αυτής της διαδικασίας είναι να ελεγχθεί αν μπορούμε να αφαιρέσουμε κάποια από τα flush για να επιτύχουμε καλύτερη επίδοση ή αν είναι όλα απαραίτητα για να εξασφαλιστεί η ανθεκτική γραμμικοποιησιμότητα.

Η αφαίρεση των flush εντολών γίνεται με τη χρήση κάποιας σημαίας. Στο Πρόγραμμα 2 φαίνονται έχουμε δύο σημαίες που κάνουν αυτή τη δουλειά. Η σημαία BIMF αφαιρεί το flush μετά τη δημιουργία του προς εισαγωγή κόμβου, ενώ η BICF αφαιρεί το flush μετά την εκτέλεση της CAS για να αλλάξει το δείκτη του προηγούμενου κόμβου, ώστε να δείχνει στον κόμβο που εισάγεται.

```

1 bool insert(int k, int item) {

while (true) {

Window* window = find(head, k);

Node* pred = window->pred;

Node* curr = window->curr;

free(window);

if (curr && curr->key == k)

return false;

Node* node = getNewNode();

10

node->set(k, item, curr);

12 #ifndef BIMF

FLUSH(node);

13

14 #endif

16 #ifdef BICF

bool res = pred->CAS_next(curr, node);

bool res = pred->CAS_nextF(curr, node);

20 #endif

21 if (res)

return true;

22

23

24 }

```

Πρόγραμμα 2: Κώδικας για τη χειροκίνητη αφαίρεση flush εντολών στη συνάρτηση εισαγωγής στοιχείων στην NVTraverse έκδοση της συνδεδεμένης λίστας. Φαίνονται δύο σημαίες που αφαιρούν flush (BIMF και BICF).

Ιδιαίτερο ενδιαφερόν για την αφαίρεση flush εντολών αποτελεί ο τρόπος που γίνονται flush αντιχείμενα, όπως ο χόμβος της συνδεδεμένες λίστας. Η συνάρτηση \_\_VERIFIER\_clflush() του PERSEVERE παίρνει ως παράμετρο τη διεύθυνση μίας μεταβλητής και την κάνει flush. Όμως, όταν έχουμε μία ολόκληρη δομή, το PERSEVERE δεν κάνει flush όλα τα πεδία της, αλλά μόνο το πρώτο. Για να εξασφαλιστεί, λοιπόν, η σωστή εγγραφή των δεδομένων στην ΕΜ, πρέπει να χρησιμοποιήσουμε την \_\_VERIFIER\_clflush() για κάθε ένα από τα πεδία της δομής.

Στο Πρόγραμμα 3 έχουμε ορίσει τη σημαία BMFN, η οποία όταν ενεργοποιείται κάνει flush τη δομή και όχι το κάθε πεδίο ξεχωριστά.

Πρόγραμμα 3: Η σημαία BMFN ενεργοποιεί τη λανθασμένη διαδικασία του flush του κόμβου μίας συνδεδεμένης λίστας.

## Αποτελέσματα

Στον Πίναχα 0.1 παραθέτουμε τα αποτελέσματα για τα litmus tests. Όλα τα litmus tests επέστρεψαν τα αναμενόμενα αποτελέσματα και βλέπουμε ότι απαιτούν μικρό αριθμό από εκτελέσεις. Αυτό είναι λογικό, καθώς η πολυπλοκότητά τους είναι μικρή.

|          |                 | Εκτ     |           |        |

|----------|-----------------|---------|-----------|--------|

|          | Αναμ.Αποτέλεσμα | Πλήρεις | Φραγμένες | Χρόνος |

| 2W+2W    | μη ασφαλές      | 3       |           | 0.04   |

| 2W+RFW   | ασφαλές         | 3       |           | 0.04   |

| 2WRW+WFW | μη ασφαλές      | 1       |           | 0.04   |

| 6W       | ασφαλές         | 4       |           | 0.04   |

| CAS+CAS  | ασφαλές         | 5       |           | 0.04   |

| WFW      | ασφαλές         | 2       |           | 0.04   |

| WFW+RW   | ασφαλές         | 3       |           | 0.04   |

| WMW+WFW  | μη ασφαλές      | 2       |           | 0.04   |

| WW       | μη ασφαλές      | 2       |           | 0.04   |

| WW+RMFW  | ασφαλές         | 3       |           | 0.04   |

Πίνακας 0.1: Αποτελέσματα της επάληθευσης ορθότητας μικρών προγραμμάτων

Στον Πίνακα 0.2 παραθέτουμε τα αποτελέσματα για τα tests του NVTraverse. Οι αρχικές εκδοχές τόσο της συνδεδεμένης λίστας, καθώς και της skiplist, έχουν οριστεί ως μη ασφαλή, επειδή δεν είναι ανθεκτικώς γραμμικοποιήσιμες. Όλα τα σχετικά tests εντοπίζουν κάποια παραβίαση συνέπειας κατά το recovery.

Τα υπόλοιπα tests ορίζονται ως ασφαλή, καθώς δεν αναμένουν κάποια παραβίαση ανθεκτικής σειριοποιησιμότητας. Πράγματι, σχεδόν όλα τα tests επιστρέφουν τα αναμενόμενα αποτελέσματα, εκτός από δύο. Το liz-pw+d+d παράγει εσωτερικό σφάλμα στο PerseVere, ενώ το sltr-pw+w+w εντοπίζει κάποια παραβίαση ορθότητας, η οποία πιθανόν οφείλεται σε κάποιο λάθος στην υλοποίηση της skiplist, π.χ. λείπει κάποιο flush. Τέλος, τα μεγάλα tests με τα τρία νήματα παράγουν πάνω από 40 χιλιάδες εκτελέσεις για την απλή συνδεδεμένη λίστα, ενώ για την skiplist ξεπερνούν το όριο χρόνου που έχουμε θέσει, το οποίο είναι 24 ώρες.

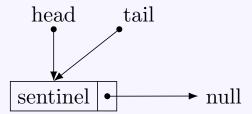

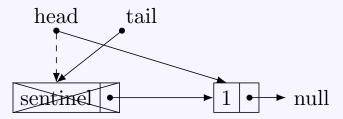

Στον Πίνωχα 0.3 φαίνονται τα αποτελέσματα για την Persistent Queue. Έχουμε υλοποιήσει λιγότερα tests για την Persistent Queue σε σύγχριση με το NVTraverse, καθώς είναι λιγότερο περίπλοχη και δεν επιδειχνύει πολλές προβληματιχές συμπεριφορές. Όπως και με το NVTraverse, οι μη ανθεχτιχώς γραμμιχοποιήσιμες εχδοχές ορίζονται ως μη ασφαλή και τα tests για την Durable Queue ως ασφαλή. Τα αποτελέσματα είναι τα αναμενόμενα.

|               |                    | Ехт        |            |            |

|---------------|--------------------|------------|------------|------------|

|               | Αναμ.Αποτέλεσμα    | Πλήρεις    | Φραγμένες  | Χρόνος     |

| lor-ww        | μη ασφαλές         | 5          |            | 0.10       |

| lor-pw+d+d    | μη ασφαλές         | 9          |            | 0.28       |

| lor-pw+w+d    | μη ασφαλές         | 3          |            | 0.15       |

| lor-pw+w+w    | μη ασφαλές         | 2          |            | 0.15       |

| lor-pw+ww     | μη ασφαλές         | 6          |            | 0.17       |

| lor-pw+w+w+d  | μη ασφαλές         | 3          |            | 0.18       |

| lor-pw+w+ww   | μη ασφαλές         | 6          |            | 0.26       |

| liz-ww        | ασφαλές            | 3          |            | 0.13       |

| liz-pw+d+d    | ασφαλές            | !!         | !!         | !!         |

| liz-pw+w+d    | ασφαλές            | 116        |            | 3.59       |

| liz-pw+w+w    | ασφαλές            | 35         |            | 1.37       |

| liz-pw+ww     | ασφαλές            | 3          |            | 0.16       |

| liz-pw+w+w+d  | ασφαλές            | 42293      |            | 1981.83    |

| liz-pw+w+ww   | ασφαλές            | 123        |            | 7.77       |

| ltr-ww        | ασφαλές            | 3          |            | 0.17       |

| ltr-pw+d+d    | ασφαλές            | 118        | 2          | 10.41      |

| ltr-pw+w+d    | ασφαλές            | 76         |            | 3.11       |

| ltr-pw+w+w    | ασφαλές            | 25         |            | 1.38       |

| ltr-pw+ww     | ασφαλές            | 3          |            | 0.20       |

| ltr-pw+w+w+d  | ασφαλές            | 13902      |            | 1019.78    |

| ltr-pw+w+ww   | ασφαλές            | 108        |            | 10.04      |

| slor-pw+d+d   | μη ασφαλές         | 4          |            | 0.14       |

| slor-pw+w+w   | μη ασφαλές         | 2          |            | 0.16       |

| slor-pw+w+w+d | μη ασφαλές         | 5          |            | 0.32       |

| sliz-pw+d+d   | ασφαλές            | 7119       | 16         | 2869.06    |

| sliz-pw+w+w   | ασφαλές            | 15         |            | 7.39       |

| sliz-pw+w+w+d | ασφαλές            | <u>(+)</u> | <u>(b</u>  | <u>(-)</u> |

| sltr-pw+d+d   | ασφαλές            | 26732      | 14         | 12247.60   |

| sltr-pw+w+w   | <del>ασφαλές</del> | 1812       | 1          | 460.08     |

| sltr-pw+w+w+d | ασφαλές            | <u>(1)</u> | <u>(1)</u> | <b>(</b>   |

Πίνακας 0.2: Αποτελέσματα της επάληθευσης ορθότητας για το NVTraverse.  $\Theta$ : όριο χρόνου (>24ώρες), !!: εσωτερικό πρόβλημα στο PerSeVere, διαγράμμιση: λάθος αποτελέσμα (σε σύγκριση με το αναμενόμενο)

|           | Εκτελέσεις      |         |           |        |  |

|-----------|-----------------|---------|-----------|--------|--|

|           | Αναμ.Αποτέλεσμα | Πλήρεις | Φραγμένες | Χρόνος |  |

| ms-e      | μη ασφαλές      | 3       |           | 0.08   |  |

| ms-pe+e+e | μη ασφαλές      | 2       |           | 0.10   |  |

| dq-e      | ασφαλές         | 1       |           | 0.10   |  |

| dq-pe+e+d | ασφαλές         | 6       |           | 0.18   |  |

| dq-pe+e+e | ασφαλές         | 28      | 24        | 0.53   |  |

| dq-pe+d+d | ασφαλές         | 28      | 2         | 0.83   |  |

Πίνακας 0.3: Αποτελέσματα της επάληθευσης ορθότητας για την Persistent Queue

Στον Πίναχα 0.4 παρουσιάζονται τα αποτελέσματα για τη διαδικασία αφαίρεσης flush εντολών. Όπως φαίνεται, οι περισσότερες σημαίες παράγουν σφάλμα σε τουλάχιστον ένα test. Αυτό υποδηλώνει ότι όλες οι flush εντολές είναι απαραίτητες για την εξασφάλιση ανθεκτικής γραμμικοποιησιμότηταςς. Η μόνη εξαίρεση είναι η σημαία BRMF, η οποία αφαιρεί το flush αμέσως μετά την πρόσβαση στον κόμβο που πρόκειται να αφαιρεθεί. Αυτό, ωστόσο, δεν σημαίνει ότι αυτό το flush μπορεί να αφαιρεθεί. Είναι πιθανό να ανακαλυφθεί κάποιο σφάλμα σε πιο περίπλοκα tests.

Το test ltr-pw+w+w-tmf αντιστοιχεί επαχριβώς στο Παράδειγμα 0.2, καθώς έχει αφαιρεθεί το flush που εισάγεται από το NVTraverse για να εξασφαλιστεί ότι το μονοπάτι προς τον κόμβο που εισάγεται έχει εγγραφεί στην ΕΜ. Επίσης, μπορούμε να παρατηρήσουμε ότι η αφαίρεση flush εντολών οδηγεί σε περισσότερες εκτελέσεις, όπως για παράδειγμα στην περίπτωση του test ltr-pw+w+d-tmf, στο οποίο εξερευνείται μία επιπλέον εκτέλεση σε σύγκριση με την εκδοχή με όλα τα flush. Αυτό είναι λογικό, καθώς αφαιρώντας flush εντολές επιτρέπουμε περισσοτέρες πιθανές καταστάσεις μετά από κάποιο crash.

|                                  |                          | Εκτ      |           |                |

|----------------------------------|--------------------------|----------|-----------|----------------|

|                                  | Αποτέλεσμα               | Πλήρεις  | Φραγμένες | Χρόνος         |

| ltr-pw+w+w-mfn                   | μη ασφαλές               | 2        |           | 0.55           |

| ltr-pw+w+d-mfn                   | μη ασφαλές               | 3        |           | 0.29           |

| ltr-pw+w+w-imf<br>ltr-pw+w+d-imf | μη ασφαλές<br>μη ασφαλές | 2<br>3   |           | $0.59 \\ 0.19$ |

| ltr-pw+w+w-icf                   | μη ασφαλές               | 2        |           | 0.21           |

| ltr-pw+w+d-icf                   | ασφαλές                  | 76       |           | 3.37           |

| ltr-pw+d+d-tmf                   | ασφαλές                  | 119      | 2         | 5.77           |

| ltr-pw+w+w-tmf                   | μη ασφαλές               | 2        |           | 0.23           |

| ltr-pw+w+d-tmf                   | ασφαλές                  | 77       |           | 1.63           |

| ltr-pw+d+d-rmf                   | ασφαλές                  | 118      | 2         | 11.30          |

| ltr-pw+w+d-rmf                   | ασφαλές                  | 76       |           | 3.43           |

| ltr-pw+d+d-rcf<br>ltr-pw+w+d-rcf | μη ασφαλές<br>ασφαλές    | 71<br>76 |           | $7.29 \\ 3.41$ |

Πίνακας 0.4: Αποτελέσματα της επάληθευσης ορθότητας για το NVTraverse με αφαίρεση ορισμένων flush εντολών..

Τέλος, κάναμε και μία σύγκριση μεταξύ του ελέγχου μοντέλου για μοντέλα συνέπειας και μοντέλα επιμονής. Τα αποτελέσματα φαίνονται στον Πίνακα 0.5. Για τον έλεγχο της συνέπειας χρησιμοποιήσαμε το GenMC με το TSO μοντέλο συνέπειας. Όπως αναμένεται, παρατηρούμε ότι στην περίπτωση του ελέγχου της επιμονής, το εργαλείο εξερευνεί πολύ μεγαλύτερο αριθμό εκτελέσεων, εώς και 4 τάξεις παραπάνω (sl-pw+d+d). Αυτό είναι απολύτως λογικό, καθώς στον έλεγχο της επιμονής πρέπει να ληφθούν υπόψη όχι μόνο η συνέπεια του προγράμματος, αλλά και οι πιθανές καταστάσεις μετά από ένα crash.

### Επίλογος

Η εργασία αυτή πραγματεύτηκε την τομή διαφορετικών πεδίων και πιο συγκεκριμένα του ελέγχου ορθότητας μέσω τεχνικών ελέγχου μοντέλου, της ΕΜ και των μοντέλων επιμονής και των δομών δεδομένων χωρίς κλειδώματα. Παρουσιάσαμε μία σουίτα ελέγχου προγραμμάτων ΕΜ, η οποία μπορεί να χρησιμοποιηθεί από εργαλεία ελέγχου μοντέλου για την επαλήθευση ορθότητας των προγραμμάτων, αλλά και των ίδιων των εργαλείων.

|             |                 | GENMC TSO |           |        | PERSEVERE |             |          |

|-------------|-----------------|-----------|-----------|--------|-----------|-------------|----------|

|             | Ανάμ.Αποτέλεσμα | Πλήρεις   | Φραγμένες | Χρόνος | Πλήρεις   | Φραγμένες   | Χρόνος   |

| CAS+CAS     | ασφαλές         | 4         |           | 0.04   | 5(44)     |             | 0.04     |

| l-pw+w+d    | ασφαλές         | 14        |           | 0.09   | 126       | 2           | 5.60     |

| l-pw+w+w+d  | ασφαλές         | 1543      | 2         | 5.49   | 13902     |             | 1019.78  |

| sl-pw+d+d   | ασφαλές         | 50        | 1         | 0.26   | 26732     | 14          | 12247.60 |

| sl-pw+w+w+d | ασφαλές         | 1400      |           | 9.20   | <b>(</b>  | <u>(-</u> ) | <b>(</b> |

Πίνακας 0.5: Σύγκριση ελέγχου συνέπειας και επιμονής

Μέσα από τα tests της σουίτας μας μπορέσαμε να βρούμε ένα εσωτερικό πρόβλημα του PerSeVerE, το οποίο αναφέρθηκε στους δημιουργούς του εργαλείου, οι οποίο στη συνέχεια πρόσθεσαν επιπλέον υποστήριξη στον πυρήνα του εργαλείου για να αντιμετωπιστεί το πρόβλημα. Επιπλέον, επιβεβαιώσαμε ότι οι απλές εκδοχές κάποιων βασικών δεδομένων χωρίς κλειδώματα δεν είναι ανθεκτικά γραμμικοποιήσιμες, ενώ οι ανθεκτικές εκδοχές τους περάσαν όλους τους ελέγχους μας. Τέλος, με την αφαίρεση flush εντολών από την υλοποίηση του NVTraverse, δείξαμε την αναγκαιότητα τους για να εξασφαλίσουν την ορθότητα της δομής, καθώς προέκυπταν παραβιάσεις ορθότητας.

Αναφορικά με σχετική βιβλιογραφία, αλλά και μελλοντική επέκταση της σουίτας μας, υπάρχουν πολλές βιβλιοθήκες ΕΜ δημόσια διαθέσιμες, όπως η PMDK [Inte15]. Επιπλέον, υπάρχει μεγάλη ποικιλία υλοποιήσεων δομών δεδομένων για ΕΜ [Lee19, Izad21, Cai21, Kim21], όπως key-value stores, δέντρα κ.λπ. Με παρόμοιο τρόπο με το NVTraverse, έχουν προταθεί ανθεκτικοί μετασχηματισμοί γραμμικοποιήσιμων δομών δεδομένων [Frie21b], καθώς και ορισμένες βιβλιοθήκες που απαιτούν ελάχιστη παρέμβαση του χρήστη για την επίτευξη ανθεκτικότητας [Wei22]. Μία μελλοντική επέκταση της σουίτας μας, θα μπορούσε να περιλάβει πολλές από αυτές τις δομές και παραδείγματα από τις βιβλιοθήκες.

Επίσης, θα είχε ενδιαφέρον να προστεθούν και άλλα μοντέλα στο Persevere (με τη χρήση του kater), όπως αυστηρά μοντέλα επιμονής, π.χ. TSOPER [Ekem21], αλλά και άλλων αρχιτεκτονικών, π.χ. PARMv8 [Raad18]. Θα μπορούσε, επιπλέον, να μελετηθεί η ευρωστία (robustness) μεταξύ χαλαρών και αυστήρων μοντέλων επιμονής, δηλαδή να εξεταστεί κατά πόσο το υπό εξέταση πρόγραμμα εμφανίζει τις ίδιες συμπεριφορές μεταξύν των δύο μοντέλων.

Τέλος, θα μπορούσε να προστεθεί υποστήριξη για τις εντολές clflushopt και sfence στο PerSeVerE, έτσι ώστε να μελετηθούν κάποιες βελτιστοποιημένες εκδοχές των δομών δεδομένων.

#### Chapter 1

### Introduction

#### 1.1 Overview

In computer architecture, one of the most promising technological breakthroughs of recent years is the introduction of Persistent Memory. Persistent Memory aims to replace traditional DRAMs, while being non-volatile, i.e., preserving its contents after a crash, like disks do.

However, writing crash-safe programs for Persistent Memory is tricky. Crashes can happen at any time during the program's execution and can lead to inconsistent states during the recovery process. Therefore, programmers have to carefully reason about the behaviour of their programs with respect to crashes. This behaviour can be formalized with the use of persistency memory models, which define the order in which memory operations persist.

In this thesis, we are going to discuss how persistency memory models can be used in combination with model checking, which is a powerful verification technique, in order to check the correctness of various Persistent Memory programs. Persistency model checking introduces new challenges. For example, a crash can happen at any time during program execution leading to a far bigger state space than non-crashing concurrent programs. Recent model checking tools use state space reduction techniques like Dynamic Partial Order Reduction [Flan05, Abdu14] in order to avoid exploring redundant executions. One such tool is Persever [Koko21a], which we are going to use in this thesis.

An important class of concurrent programs are those that implement so called *lock-free data structures*. These data structures ensure that the memory is always in a consistent state. As a result, they may seem like very intuitive fit for Persistent Memory. However, in a crashing execution it is possible for these data structures to be left in an inconsistent state due to cache volatility. There have been various studies on how to ensure durability for lock-free data structures [Frie18, Frie21a] and we are going to investigate how to employ persistency model checking in order to test them.

In summary, the new challenges that arise with the introduction of Persistent Memory create new opportunities for research in the field of verification. In this thesis, we are going to discuss the basics of model checking, persistency memory models and lock-free data structures and we are going to employ model checking in order to verify Persistent Memory programs.

#### 1.2 Contributions