#### ΕΘΝΙΚΟ ΜΕΤΣΟΒΙΟ ΠΟΛΥΤΕΧΝΕΙΟ

#### ΣΧΟΛΗ ΗΛΕΚΤΡΟΛΟΓΩΝ ΜΗΧΑΝΙΚΩΝ ΚΑΙ ΜΗΧΑΝΙΚΩΝ ΥΠΟΛΟΓΙΣΤΩΝ Τομέας Τεχνολογίας Πληροφορικής και Υπολογιστών Εργαστήριο Μικροϋπολογιστών και Ψηφιακών Συστημάτων

# Acceleration of Image Recognition on Caffe framework using FPGAs

ΔΙΠΛΩΜΑΤΙΚΗ ΕΡΓΑΣΙΑ

Δημήτριος Ν. Δανόπουλος

Επιβλέπων: Δημήτριος Ι. Σούντρης

Αναπληρωτής Καθηγητής

#### ΕΘΝΙΚΟ ΜΕΤΣΟΒΙΟ ΠΟΛΥΤΕΧΝΕΙΟ

#### ΣΧΟΛΗ ΗΛΕΚΤΡΟΛΟΓΩΝ ΜΗΧΑΝΙΚΩΝ ΚΑΙ ΜΗΧΑΝΙΚΩΝ ΥΠΟΛΟΓΙΣΤΩΝ Τομέας Τεχνολογίας Πληροφορικής και Υπολογιστών Εργαστήριο Μικροϋπολογιστών και Ψηφιακών Συστημάτων

# Acceleration of Image Recognition on Caffe framework using FPGAs

#### ΔΙΠΛΩΜΑΤΙΚΗ ΕΡΓΑΣΙΑ

Δημήτριος Ν. Δανόπουλος

**Επιβλέπων**: Δημήτριος Ι. Σούντρης Αναπληρωτής Καθηγητής

Εγκρίθηκε από την τριμελή εξεταστική επιτροπή την  $18^{\eta}$  Μαΐου 2018 .

.....

Δ. Σούντρης Κ. Πεκμεστζή Γ. Γκούμας

Αναπληρωτής Καθηγητής Καθηγητής Επίκουρος Καθηγητής

Αθήνα, Μάιος 2018

| Δημήτριος Ν. Δανόπουλος                                                                                                                                                    |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Διπλωματούχος Ηλεκτρολόγος Μηχανικός και Μηχανικός Υπολογιστών Ε.Μ.Π.                                                                                                      |

|                                                                                                                                                                            |

|                                                                                                                                                                            |

|                                                                                                                                                                            |

|                                                                                                                                                                            |

|                                                                                                                                                                            |

|                                                                                                                                                                            |

|                                                                                                                                                                            |

| Copyright © Δημήτριος Ν. Δανόπουλος, 2018.                                                                                                                                 |

| Με επιφύλαξη παντός δικαιώματος. All rights reserved.                                                                                                                      |

| Απαγορεύεται η αντιγραφή, αποθήκευση και διανομή της παρούσας εργασίας, εξ ολοκλήρου ή τμήματος αυτής, για εμπορικό σκοπό. Επιτρέπεται η ανατύπωση, αποθήκευση και διανομή |

για σκοπό μη κερδοσκοπικό, εκπαιδευτικής ή ερευνητικής φύσης, υπό την προϋπόθεση να αναφέρεται η πηγή προέλευσης και να διατηρείται το παρόν μήνυμα. Ερωτήματα που αφορούν τη χρήση της εργασίας για κερδοσκοπικό σκοπό πρέπει να απευθύνονται προς τον

Οι απόψεις και τα συμπεράσματα που περιέχονται σε αυτό το έγγραφο εκφράζουν τον συγγραφέα και δεν πρέπει να ερμηνευθεί ότι αντιπροσωπεύουν τις επίσημες θέσεις του

συγγραφέα.

Εθνικού Μετσόβιου Πολυτεχνείου.

# Περίληψη

Η Μηχανική Μάθηση έχει σημειώσει σημαντική εξέλιξη τα τελευταία χρόνια. Η αναγνώριση εικόνας καθίσταται σημαντικό στοιχείο σε όλο και περισσότερες εφαρμογές, από ιατρικές διαγνώσεις και αυτόνομα αυτοκίνητα μέχρι και σε μεγάλα κέντρα δεδομένων. Τα τελευταία χρόνια, state-of-the-art Συνελικτικά Νευρωνικά Δίκτυα Βαθιάς Μάθησης που μπορούν να καταγράψουν πολύπλοκα μη γραμμικά χαρακτηριστικά, έχουν δείξει τη δημοφιλία τους σε διάφορες εφαρμογές πραγματικού χρόνου, επιτυγχάνοντας ακρίβεια σε όλα τα τεστ κατανόησης εικόνας (Αναγνώριση Εικόνας, Ανίχνευση Εικόνας κ.λπ.). Ωστόσο, αυτή η δυνατότητα έρχεται με το κόστος των υψηλών απαιτήσεων υπολογισμών και μνήμης. Τα νευρωνικά δίκτυα απαιτούν δισεκατομμύρια αριθμητικές πράξεις και εκατομμύρια παραμέτρους, έχοντας έτσι πολύ υψηλή υπολογιστική πολυπλοκότητα.

Πολλές εφαρμογές νευρωνικών δικτύων αντιπροσωπεύουν μια υπολογιστική πρόκληση για τους επεξεργαστές γενικής χρήσης. Απαιτούν λύσεις υψηλής απόδοσης που ενσωματώνονται σε υπάρχοντα συστήματα με αυστηρούς περιορισμούς πραγματικού χρόνου και ισχύος. Ένα πρώτο σημαντικό βήμα της επιτάχυνσης αυτών των εφαρμογών είναι μια προσανατολισμένη προς το υλικό προσέγγιση που επιτρέπει γρήγορες και αποδοτικές λύσεις. Ως αποτέλεσμα, έχουν υιοθετηθεί επιταχυντές υλικού σε πλατφόρμες υψηλής απόδοσης, όπως η συστοιχία επιτόπια προγραμματιζόμενων πυλών (FPGAs), για τη βελτίωση της απόδοσης αυτών των εφαρμογών.

Αυτή η διπλωματική εργασία διερευνά τις δυνατότητες της επιτάχυνσης των νευρωνικών δικτύων με βάση το FPGA, χρησιμοποιώντας τη πλατφόρμα βαθιάς μάθησης Caffe και αποδεικνύει την βασιμότητα της ιδέας μια πλήρως λειτουργικής εφαρμογής σε ένα σύστημα Zynq System-on-Chip. Το ετερογενές σύστημα CPU-FPGA έχει σχεδιαστεί για την επιτάχυνση της αναγνώρισης εικόνας μέσω της πλατφόρμας Caffe, χρησιμοποιώντας τον επιταχυντή υλικού, επιτυγχάνοντας σημαντικά αποτελέσματα.

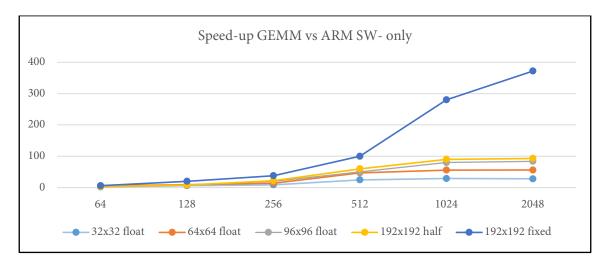

Ο επιταχυντής FPGA βασίζεται σε μια συνάρτηση που ονομάζεται GEMM (General Matrix Multiply), η οποία είναι το πιο υπολογιστικά συμφορητικό μέρος των αλγορίθμων αναγνώρισης εικόνας στη πλατφόρμα του Caffe. Αυτός ο αλγόριθμος πολλαπλασιασμού με πολλαπλούς ενσωματωμένους βρόχους επανάληψης υιοθετεί διάφορες τεχνικές βελτιστοποίησης τόσο στο λογισμικό όσο και στο υλικό για να ελαχιστοποιήσει τις προσβάσεις στη μνήμη και να παραλληλοποιήσει πλήρως τις αριθμητικές πράξεις. Ο επιταχυντής FPGA έχει υλοποιηθεί με Σύνθεση Υψηλού Επιπέδου στο περιβάλλον ανάπτυξης SDSoC για τη πλακέτα Xilinx Zynq ZC702 και φτάνει τη μέγιστη συχνότητα ρολογιού που υποστηρίζεται, η οποία είναι 200MHz με χρήση πόρων κοντά στο 80%. Η αξιολόγηση του επιταχυντή δείχνει ότι η εκτέλεση της συνάρτησης GEMM μπορεί να επιταχυνθεί έως και 380 φορές σε σχέση με την απλή εκδοχή σε ARM επεξεργαστή, ενώ το τελικό σύστημα με τον ενσωματωμένο επιταχυντή μπορεί να αυξήσει την απόδοση και την ενεργειακή κατανάλωση της αναγνώρισης εικόνας ως και 10% με λιγότερο από 0.4% μείωση στην ακρίβεια πρόβλεψης.

**Λέξεις Κλειδιά:** μηχανική μάθηση, συνελικτικά νευρωνικά δίκτυα, DNN, αναγνώριση εικόνας, Caffe, επιτάχυνση υλικού, FPGA, σύνθεση υψηλού επιπέδου, Zyng SoC

#### **Abstract**

Machine Learning has achieved major breakthroughs in recent years. Image Recognition is becoming a vital feature in ever more applications ranging from medical diagnostics and autonomous vehicles to big data centers. In recent years, state-of-the-art Deep Convolutional Neural Networks (DNNs) which can capture complex non-linear features have shown their popularity in various real world applications achieving record-breaking accuracies in all image understanding benchmarks (i.e. Image Recognition, Image Detection etc.). However, this ability comes at the cost of high computational and memory requirements. DNNs require billions of arithmetic operations and millions of parameters, thus they have a very high computational complexity.

Many DNN applications represent a computational challenge for general purpose processors. They demand high performance solutions that integrate into existing systems with tight real-time and power constraints. A first important step of the acceleration of these applications is a hardware-oriented approximation that enables fast and efficient solutions. As a result, hardware accelerators on high performance platforms, such as Field Programmable Gate Arrays (FPGAs), have been adopted to improve the performance of these applications.

This master thesis explores the potential of FPGA-based acceleration of DNNs, using Caffe Deep Learning Framework and demonstrates a fully functional proof-of-concept implementation on a Zynq System-on-Chip. The heterogeneous CPU-FPGA system is designed for the acceleration of image classification with Caffe framework by utilizing the hardware accelerator achieving significant results.

The FPGA accelerator is based on a function called GEMM (General Matrix Multiply) which is the most computational intensive part of the image classification algorithms in Caffe framework. This nested-loop matrix multiplication algorithm adopts several optimization techniques both in software and hardware to minimize the memory accesses and fully parallelize the arithmetic operations. The FPGA accelerator has been synthesized using High-Level Synthesis on SDSoC Development Environment for the Xilinx Zynq ZC702 board and reaches its maximum supported clock frequency of 200MHz with a device utilization of ~80%. The evaluation shows that the accelerator function can achieve up to 380 × speed-up over the simple ARM SW version while the final system with the integrated accelerator can boost the performance by 10% of the image classification with less than 0.4% accuracy drop while maintaining substantial energy-efficiency.

**Keywords:** machine learning, convolutional neural networks, DNN, image recognition, Caffe, hardware acceleration, FPGA, high-level synthesis, Zynq SoC

# Ευχαριστίες

Αρχικά, θα ήθελα να ευχαριστήσω τον επιβλέποντα καθηγητή μου κ. Δημήτριο Σούντρη, για την εμπιστοσύνη που μου έδειξε και την ξεχωριστή εκπαιδευτική ευκαιρία που μου προσέφερε αυτή η διατριβή. Επιπλέον, εκφράζω την ειλικρινή μου ευγνωμοσύνη στον Μεταδιδακτορικό Ερευνητή κ. Χριστόφορο Κάχρη, για τη διαρκή υποστήριξη, ενθάρρυνση και τις συμβουλές του κατά τη διάρκεια της έρευνάς μου στο ΕΜΠ. Ήταν ένα πραγματικό προνόμιο και τιμή για μένα να μοιράζομαι την εξαιρετική του γνώση και τον ευχαριστώ επίσης για την οργάνωση αυτού του έργου και τη συμμετοχή μου σε διάφορα ενδιαφέροντα έργα και εκδηλώσεις. Ιδιαίτερες ευχαριστίες απευθύνω και σε όλο το προσωπικό του Εργαστηρίου Μικροϋπολογιστών (MicroLab) του ΕΜΠ για την πολύτιμη βοήθεια τους.

Τέλος, θέλω να εκφράσω την ευγνωμοσύνη μου σε όλη την οικογένειά μου που μου έδωσε την ενθάρρυνση και το κουράγιο κατά τη διάρκεια των σπουδών μου στο πανεπιστήμιο και ιδιαίτερα στη μητέρα μου για τη συνεχή άνευ όρων υποστήριξη και έμπνευση. Επίσης, μια ιδιαίτερη ευχαριστία προς τη Μαρία για όλη την αγάπη και την υποστήριξη.

# Acknowledgments

First and foremost, I would like to thank Professor Dimitrios Soudris, the supervisor of this project, for the trust he showed me and the distinct educational opportunity that I was offered for this thesis. Moreover, I express my sincere gratitude to PostDoctoral Reasearcher Christoforos Kachris, my advisor, for his enduring support, encouragement and advice during my research at Technical University of Athens, Greece. It was a real privilege and an honor for me to share of his exceptional knowledge and I also thank him for arranging this project and involving me in various interesting projects and events. Special thanks also goes to the whole staff of the Microprocessors and Digital Systems Laboratory (MicroLab) of NTUA.

Finally, I want to express my gratitude to my whole family who gave me the encouragement and motivation throughout my studies in the university and especially my mother for the constant unconditional support and inspiration. Last but not least, a special thanks to Maria for all the love and support.

# **Contents**

| Π | [ερίλ | .ηψη                                             | i   |

|---|-------|--------------------------------------------------|-----|

| A | bstr  | act                                              | iii |

| E | κτετ  | αμένη Περίληψη                                   | xi  |

| 1 | Int   | roduction                                        | 1   |

|   | 1.1   | Motivation                                       | 1   |

|   | 1.2   | Chapter Organization                             | 2   |

| 2 | Bac   | kground                                          | 3   |

|   | 2.1   | Introduction to Machine Learning                 | 3   |

|   | 2.2   | Introduction to Convolutional Neural Networks    | 4   |

|   |       | 2.2.1 Brain analogy                              | 4   |

|   |       | 2.2.2 Operation of a multi-layer network         | 5   |

|   |       | 2.2.3 Network Topologies                         | 8   |

|   | 2.3   | FPGAs                                            | 11  |

|   |       | 2.3.1 Introduction to FPGA                       | 11  |

|   |       | 2.3.2 Introduction to High Level Synthesis       | 14  |

|   |       | 2.3.3 Heterogeneous Systems                      | 16  |

|   | 2.4   | Caffe Framework                                  | 19  |

|   |       | 2.4.1 Anatomy of Caffe                           | 19  |

|   |       | 2.4.2 Operation of the framework                 | 21  |

|   |       | 2.4.3 Caffe tools                                | 22  |

| 3 | Caf   | fe in Embedded SoC                               | 25  |

|   | 3.1   | Caffe in Zynq SoC                                | 25  |

|   |       | 3.1.1 Creating the boot image                    | 25  |

|   |       | 3.1.2 Cross-compiling 3d party libraries for ARM | 26  |

|   |       | 3.1.3 Cross-compiling Caffe for ARM              | 30  |

|   | 3.2   | DNN architectures for embedded SoC               | 31  |

|   |       | 3.2.1 Memory optimized networks                  | 31  |

|   |       | 3.2.2 Accuracy optimized networks                | 32  |

|   |       | 2.2.2 Final Wardin                               | 22  |

| 4 FPGA Accelerator Design                      | 33 |

|------------------------------------------------|----|

| 4.1 Selecting function for acceleration        | 34 |

| 4.2 Software function implementation           | 37 |

| 4.2.1 Algorithm Design                         | 38 |

| 4.2.2 Software optimizations                   | 40 |

| 4.3 Hardware function implementation           | 43 |

| 4.3.1 Communication interface                  | 44 |

| 4.3.2 Hardware optimizations                   | 46 |

| 4.4 Integration with Caffe                     | 51 |

| 4.4.1 Creating the booting system              | 51 |

| 4.4.2 Linking the hardware function with Caffe | 52 |

| 4.5 Setting up and running the final system    | 53 |

| 5 Evaluation and Results                       | 57 |

| 5.1 Caffe on embedded CPU performance          | 57 |

| 5.1.1 Caffe metrics on ARM                     | 58 |

| 5.1.2 Neural Network Analysis                  | 62 |

| 5.2 Hardware Accelerator Performance           | 67 |

| 5.2.1 Hardware Kernel Analysis                 | 67 |

| 5.2.2 Hardware function Acceleration           | 71 |

| 5.3 Caffe in CPU-FPGA performance              | 73 |

| 5.4 Caffe in AWS cloud performance             | 75 |

| 6 Conclusion                                   | 79 |

| Appendix <b>A.</b>                             | 81 |

| Appendix <b>B</b>                              | 83 |

| Bibliography                                   | 93 |

# Εκτεταμένη Περίληψη

## Εισαγωγή

Η συνεχής εκθετική αύξηση των μέσων ενημέρωσης, των ΙοΤ και των μεγάλων δεδομένων απαιτεί γενικά γρήγορες ταχύτητες επεξεργασίας, ενώ οι εφαρμογές πρέπει να διατηρούν χαμηλό κόστος ενέργειας και να διατηρούν μικρό χρόνο ανάπτυξης. Πολλά συστήματα υψηλής απόδοσης βασίζονται σε αλγόριθμους μηχανικής μάθησης (Machine Learning), όπως η ταξινόμηση εικόνων, οι αναλύσεις δεδομένων κ.λπ. που απαιτούνται για ενσωματωμένες και εφαρμογές μεγάλων δεδομένων.

Σε αυτό το πεδίο, τα Συνελικτικά Νευρωνικά Δίκτυα Βαθιάς Μάθησης ή στα αγγλικά Deep Convolutional Neural Networks (DNNs) έχουν αποκτήσει σημαντική έλξη λόγω του ότι προσφέρουν αξιόλογη ακρίβεια στην πρόβλεψη και μεγάλη ευελιξία. Αυτοί οι αλγόριθμοι εμπνευσμένοι από τον εγκέφαλο αποτελούνται από πολλαπλά στρώματα ανιχνευτών και ταξινομητών προτύπων και χρησιμοποιούν τεχνικές από τη μηχανική μάθηση, οι οποίες τους επιτρέπουν να ανταγωνίζονται την ακρίβεια των ανθρώπων όταν πρόκειται για παράδειγμα για αναγνώριση εικόνων.

Παρόλο που απαιτείται σοβαρός υπολογισμός για την ανάλυση των μεγάλων ποσοτήτων δεδομένων, η χρήση συστημάτων υψηλών επιδόσεων φαίνεται πολλά υποσχόμενη, αλλά η πρόκληση της μείωσης του υψηλού ενεργειακού κόστους και των χρόνων επεξεργασίας παραμένει. Από την άλλη πλευρά, οι υλοποιήσεις από τέτοια συστήματα όπως η συστοιχία επιτόπια προγραμματιζόμενων πυλών ή αλλιώς στα αγγλικά Field-programmable gate array (FPGA) έχουν δει μεγάλη πρόοδο, καθώς οι νέες αναδυόμενες τεχνικές αξιοποιούν την αρχιτεκτονική των FPGAs εκμεταλλευόμενη τους επιταχυντές υλικού υψηλής απόδοσης (hardware accelerators) με μικρά κόστη ενέργειας, διατηρώντας παράλληλα την προσαρμοστικότητα των γρήγορων πρωτοτύπων. Με τη χρήση επιταχυντών υλικού αυξάνεται ο συνολικός ρυθμός εκτέλεσης των προγραμμάτων λόγω του εξαιρετικά παραλληλοποιήσιμου μαζικού αριθμού πράξεων που χρειάζονται οι αλγόριθμοι των DNN και επίσης μειώνεται η κατανάλωση ενέργειας. Το Caffe, ένα μια πλατφόρμα βαθιάς μάθησης του UC Berkley, έχει ήδη εφαρμοστεί και βελτιστοποιηθεί αρχικά μόνο σε δύο διαφορετικές αρχιτεκτονικές για CPU και GPU και μπορεί εύκολα να διαμορφωθεί χωρίς μεγάλες αλλαγές κώδικα.

Στην παρούσα εργασία παρουσιάζουμε:

- Μια τροποποιημένη έκδοση του Caffe για εύκολη μεταφορά του στον επεξεργαστή ARM (Zynq 7000) του FPGA SoC.

- Έναν επιταχυντή υλικού σχεδιασμένο στο περιβάλλον Xilinx SDSoC που εκμεταλλεύεται τα πλεονεκτήματα του FPGA και είναι κρίσιμος για τον αλγόριθμο αναγνώρισης εικόνας.

- Ένα σύστημα βασισμένο σε CPU-FPGA, εξαιρετικά ετερογενές προγραμματιζόμενο SoC που υποστηρίζει το περιβάλλον του Caffe και χρησιμοποιεί τον επιταχυντή υλικού, επιτυγχάνοντας σημαντική ταχύτητα και αποδοτικότητα ισχύος σε σύγκριση με τον επεξεργαστή ARM Zyng.

#### Θεωρητικό Υπόβαθρο

Μηχανική Μάθηση Η εκμάθηση μηχανών στη βάση της είναι η πρακτική της χρήσης αλγορίθμων για την ανάλυση δεδομένων, την εκμάθηση από αυτήν και, στη συνέχεια, για να γίνει μια απόφαση ή πρόβλεψη για κάτι στον κόσμο. Έτσι, αντί για την προυπάρχουσα ρουτίνα της χειροκίνητης τροποποίησης του λογισμικού με ένα συγκεκριμένο σύνολο οδηγιών για την εκτέλεση μιας συγκεκριμένης εργασίας, το μηχάνημα «εκπαιδεύεται» χρησιμοποιώντας μεγάλα ποσά δεδομένων και αλγορίθμων που του δίνουν τη δυνατότητα να μάθει πώς να εκτελέσει την εργασία. Έτσι, ο βασικός στόχος είναι να γενικευτεί και να καλυτερεύσει από την εμπειρία του. Γενίκευση σε αυτό το πλαίσιο είναι η ικανότητα μιας μηχανής εκμάθησης να εκτελεί με ακρίβεια νέα παραδείγματα / εργασίες αφού έχει εκπαιδευτεί σε ένα σετ δεδομένων. Τα παραδείγματα εκπαίδευσης προέρχονται από κάποια γενικά άγνωστη κατανομή πιθανότητας και ο εκπαιδευόμενος πρέπει να οικοδομήσει ένα γενικό μοντέλο σχετικά με αυτό το χώρο που του επιτρέπει να παράγει επαρκώς ακριβείς προβλέψεις σε νέες περιπτώσεις.

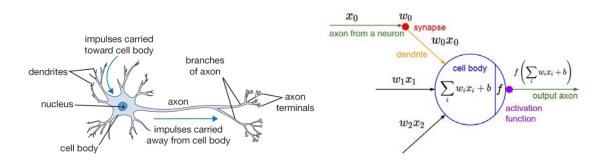

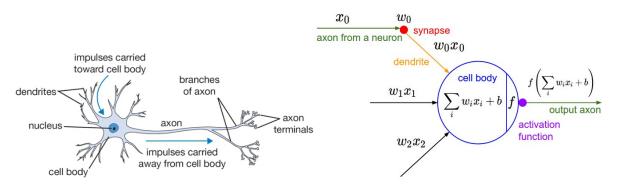

Νευρωνικά Δίκτυα Τα Συνελικτικά Νευρωνικά Δίκτυα (CNNs) είναι ένα είδος μοντέλου μηχανικής μάθησης που έχει μεγάλη πρακτική αξία στον τομέα της αναγνώρισης προτύπων. Διακρίνονται για την υπερσύγχρονη συμπεριφορά τους επειδή μπορούν να δημιουργήσουν αυτόματα τόσο χαρακτηριστικά υψηλού επιπέδου όσο και χαμηλού επιπέδου. Ένα συνελικτικό νευρωνικό δίκτυο είναι εμπνευσμένο από βιολογικές διεργασίες στις οποίες το πρότυπο σύνδεσης μεταξύ των νευρώνων εμπνέεται από την οργάνωση του ζωτικού οπτικού φλοιού. Το βασικό δομικό στοιχείο στα τεχνητά νευρωνικά δίκτυα είναι ο νευρώνας ο οποίος ανταποκρίνεται σε ερεθίσματα μόνο σε μια περιορισμένη περιοχή του οπτικού πεδίου, με αποτέλεσμα πολλοί μαζί να αντιλαμβάνονται συγκεκριμένα χαρακτηριστικά μιας εικόνας. Το παρακάτω διάγραμμα δείχνει ένα σχέδιο ενός βιολογικού νευρώνα (αριστερά) και ενός κοινού μαθηματικού μοντέλου (δεξιά). Μέσω συνάψεων οι οποίες ελέγχουν την ένταση κάθε ερεθίσματος παράγεται ένα τελικό ερέθισμα, το οποίο είναι το άθροισμα όλων των δενδριτών στον νευρώνα.

Εικόνα 1: Βιολογικός νευρώνας (αριστερά) και το μαθηματικό του μοντέλό (δεξιά) [1].

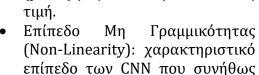

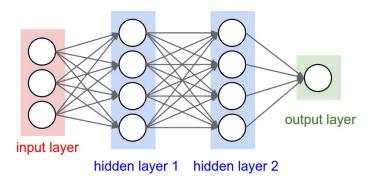

**Λειτουργία Νευρωνικών Δικτύων Βαθιάς Μάθησης** Ένα νευρωνικό δίκτυο δημιουργείται διασυνδέοντας πολλούς τεχνητούς νευρώνες. Οι νευρώνες είναι διατεταγμένοι σε ένα κατευθυνόμενο ακυκλικό γράφημα σε ένα δίκτυο προώθησης ώστε οι έξοδοι ορισμένων νευρώνων μπορούν να γίνουν εισροές σε άλλους νευρώνες. Τα βάρη στην είσοδο τους καθορίζουν πόσο σχετικοί ή όχι είναι στην εργασία που εκτελείται. Υπάρχουν στρώματα εισόδου και εξόδου και επιπλέον κρυφά επίπεδα που πολλές φορές αυξάνουν το μέγεθος και την πολυπλοκότητα του δικτύου. Αυτά μπορεί να περιλαμβάνουν επίπεδα όπως:

• Επίπεδο Συνέλιξης (Convolution): προσομοιώνει την απόκριση ενός μεμονωμένου ερεθίσματος κάνοντας την πράξη της συνέλιξης μεταξύ της εικόνας εισόδου και των βαρών

διαφόρων φίλτρων.

Επίπεδο Συγκέντρωσης (Pooling):

πρόκειται για μια διαδικασία

δειγματοληψίας που συνοψίζει

τις εξόδους γειτονικών γκρουπ

νευρώνων εντός ενός παραθύρου

(patch) με μια αντιπροσωπευτική

τιμή.

Εικόνα 2: Οργάνωση ενός νευρωνικού δικτύου με πολλαπλά επίπεδα [1].

- εφαρμόζει μια διορθωτική μη γραμμική συνάρτηση (πχ. ReLU,tanh(x), sigmoid).

- Πλήρως Συνδεδεμένο Επίπεδο (Fully Connected): συνδέει κάθε νευρώνα σε ένα στρώμα με κάθε νευρώνα σε ένα άλλο στρώμα αθροίζοντας τα αποτελέσματα για να πάρει την έξοδό του.

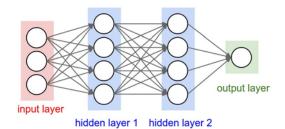

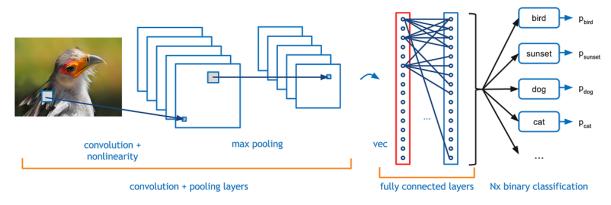

Επίσης τα νευρωνικά δίκτυα μπορούν να εκπαιδευτούν και οι παράμετροί τους μαθαίνονται κατά τη διάρκεια αυτής της φάσης. Το δίκτυο μπορεί να μάθει και να βρει τα βέλτιστα βάρη, καθορίζοντας μια λειτουργία απώλειας και χρησιμοποιώντας τον αλγόριθμο οπίσθιας τροφοδότησης (backpropagation) για την προσαρμογή των βαρών. Μετά την εκμάθηση, το δίκτυο είναι έτοιμο να αναγνωρίσει εικόνες. Ο στόχος είναι η εξαγωγή του συμπεράσματος (inference), το οποίο είναι η τελική έξοδος για την πρόβλεψη της εικόνας και καθορίζεται κατόπιν μετά από τον υπολογισμό όλων των ενδιάμεσων επιπέδων (επίπεδα συνέλιξης, συγκέντρωσης κτλ.).

Εικόνα 3: Πρόβλεψη εικόνας μετά από τον υπολογισμό της εξόδου του νευρωνικού δικτύου [2].

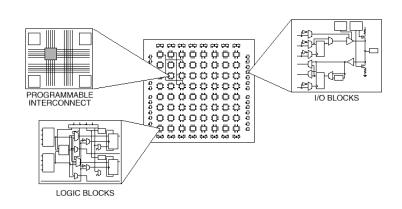

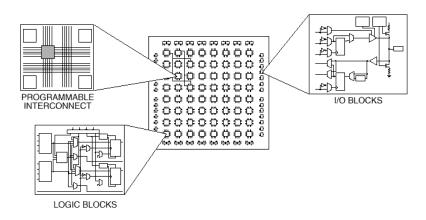

Αρχιτεκτονική FPGA Field-Programmable Gate Array (FPGA) ή στα ελληνικά συστοιχία επιτόπια προγραμματιζόμενων πυλών είναι ένα ολοκληρωμένο κύκλωμα το οποίο "προγραμματίζεται" και διαμορφώνεται αναλόγως την κατάσταση του προβλήματος. Η διαμόρφωση του FPGA καθορίζεται γενικά με τη χρήση μιας γλώσσας περιγραφής υλικού (HDL), παρόμοιας με εκείνη που χρησιμοποιείται για ένα ολοκληρωμένο κύκλωμα εξειδικευμένης εφαρμογής (ASIC) και αποσκοπεί στην εκτέλεση μιας υπολογιστικά έντονης εργασίας. Το πλεονέκτημά τους είναι ότι πολλές φορές είναι σημαντικά ταχύτερα για ορισμένες εφαρμογές λόγω της παραλληλοποιήσιμης φύσης τους.

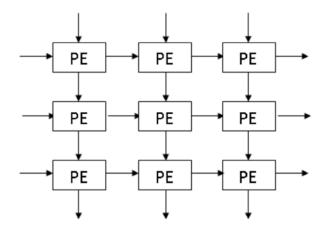

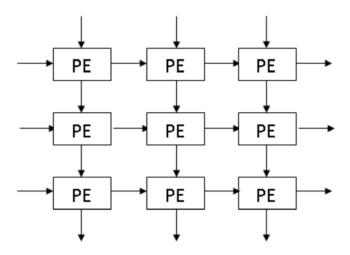

Σε αντίθεση με τους κοινούς επεξεργαστές, τα συστήματα FPGAs έχουν ανεξάρτητους κόμβους επεξεργασίας (PEs) που ανατίθενται σε ένα ειδικό τμήμα του τσιπ μπορούν να εργαστούν αυτόνομα χωρίς καμιά άλλη επίδραση από άλλα λογικά μπλοκ. Τα FPGAs αποτελούνται από (ή και 3D) συστοιχίες λογικών μπλοκ οι οποίες

Εικόνα 4: Εσωτερική αρχιτεκτονική ενός FPGA [9]

συνδέονται μέσω προγραμματιζόμενων διασυνδέσεων για την υλοποίηση ενός αναδιαμορφώσιμου ψηφιακού κυκλώματος με σκοπό την εκτέλεση και επιτάχυνση κάποιας συγκεκριμένης λειτουργίας ή πράξης.

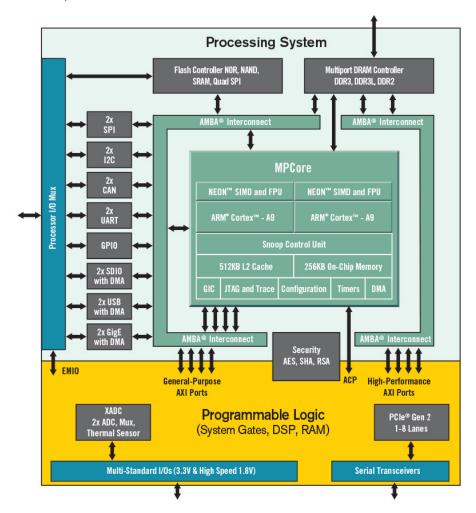

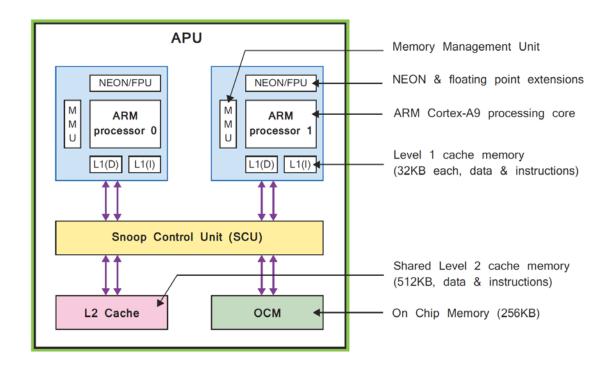

Συχνά, τα FPGAs ενσωματώνονται σε «ετερογενή» συστήματα δηλαδή συστήματα που χρησιμοποιούν περισσότερα από ένα είδος επεξεργαστών για την εξιδεικευμένη προβλημάτων. αντιμετώπιση διαφόρων Για παράδειγμα η προγραμματιζόμενων συστημάτων Zyng-7000 SoC της Xilinx ενσωματώνει την ενός προγραμματισιμότητα του λογισμικού επεξεργαστή ARM προγραμματιζόμενη τεχνολογία του FPGA. Παραδοσιακά, οι προγραμματισμοί τέτοιων συστημάτων γίνονταν χρησιμοποιώντας μια γλώσσα περιγραφής υλικού (HDL) όπως VHDL ή Verilog αλλά τώρα έχουν βρεθεί βελτιστοποιημένες μεθοδολογίες, όπως η σύνθεση υψηλού επιπέδου (HLS), η οποία καθιστά την σύνθεση υλικού ευκολότερη, με πλατφόρμες όπως το SDSoC της Xilinx. Το εργαλείο αυτό καθιστά τον προγραμματισμό λογισμικού και υλικού πολύ πιο εύκολο, προσφέροντας για την σύνθεση υλικού γλώσσα προγραμματισμού υψηλού επιπέδου (C, C++), επιτρέποντας στους προγραμματιστές να εκμεταλλευτούν τα πλεονεκτήματα υλικού χωρίς να έχουν μεγάλη τεχνογνωσία υλικού.

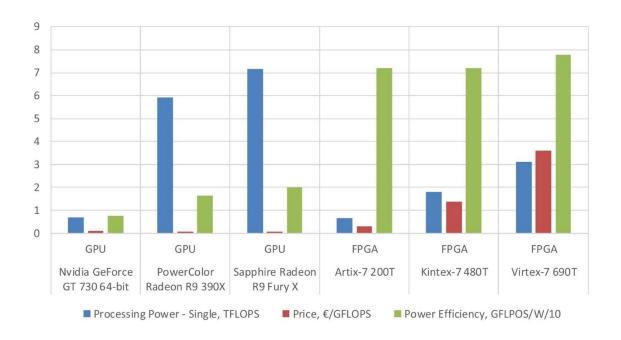

Τα FPGAs και οι επιταχυντές υλικού, διαθέτουν σημαντικά πλεονεκτήματα έναντι άλλων συστημάτων (CPU, GPU) καθώς είναι εξαιρετικά παραλληλοποιήσιμοι έχοντας ταυτόχρονα μικρή ενεργειακή κατανάλωση. Το μερίδιο αγοράς των FPGA στην διεθνή αγορά των υπολογιστικών συστημάτων είναι αξιόλογο, με εφαρμογές σε ενσωματωμένα συστήματα όσο και στο υπολογιστικό νέφος (cloud computing) που για παράδειγμα παρέχει η υπηρεσία Amazon EC2.

#### Υλοποίηση DNN σε Zynq SoC

Τα ενσωματωμένα συστήματα έχουν συνήθως πολύ συγκεκριμένες απαιτήσεις και περιορισμούς όσον αφορά την υπολογιστική ισχύ και ενέργει και την διαχείριση των περιορισμένων πόρων σε πραγματικό χρόνο (πχ. περιορισμένη μνήμη). Τα Zynq SoCs είναι ιδανικά για την αποτελεσματική υλοποίηση του DNN καθώς επιτρέπουν τη δημιουργία προσαρμοσμένων κυκλωμάτων στο υλικό, συντονισμένα ακριβώς με τις ανάγκες του αλγορίθμου. Το αποτέλεσμα είναι η κορυφαία απόδοση ανά watt που συχνά ξεπερνά τα ενσωματωμένα συστήματα CPU και GPU. Σε αυτή την παράγραφο παρουσιάζουμε μια νέα μέθοδο για την εύκολη προσαρμογή ενός DNN που εκτελείται στο περιβάλλοντου Caffe σε ένα σύστημα με βάση το Zynq χρησιμοποιώντας την πλακέτα ZC702 της Xilinx, η οποία αποτελείται από επεξεργαστή ARM 32 bit με δύο πυρήνες.

- 1. Το πρώτο βήμα προκειμένου να μεταφερθεί ολόκληρο το περιβάλλον του Caffe στο Zyng 7000 SoC για να τρέξει στον πυρήνα ARM ήταν να μεταγλωττιστούν οι απαιτούμενες εξαρτήσεις βιβλιοθήκης του Caffe (3d party libraries) και στη συνέχεια ολόκληρη το περιβάλλον του και μετέπειτα να συνδεθούν όλες οι βιβλιοθήκες για την ορθή λειτουργία του (πχ. OpenCV, Boost, OpenBlas, HDF5, LMDB, Glog κτλ.). Για αυτά τα βήματα χρησιμοποιήσαμε τον cross-compiler ARM που συμπεριελήφθη στο περιβάλλον SDSoC. Συγκεκριμένα, χρειάστηκε χειροκίνητα να κατεβάσουμε τα αρχεία προέλευσης κάθε βιβλιοθήκης που χρειάζεται και εξαρτάται το Caffe και στη συνέχεια να τα εγκαταστήσουμε ένα προς ένα χρησιμοποιώντας το ARM toolchain «arm-linux-gnueabihf», καθορίζοντας την κατάλληλη διαμόρφωση για κάθε βιβλιοθήκη ξεπερνώντας αρκετές επιπλοκές σε ορισμένες εγκαταστάσεις. Είναι σημαντικό να τονιστεί ότι στην εγκατάσταση και σύνδεση των βιβλιοθηκών επιλέχτηκε η υποστήριξη για τα NEON instrinsics που επιτρέπουν την επέκταση της SIMD αρχιτεκτονικής για λειτουργίες πολλαπλών πράξεων αλλά και η χρήση νημάτων (pthreads).

- 2. Το δεύτερο βήμα ήταν να βρεθεί μια κατάλληλη αρχιτεκτονική μοντέλου DNN για να χωρέσει στην περιορισμένη μνήμη του ενσωματωμένου SoC. Για την μεταγλώτισση του Caffe, η διεπαφή διατηρήθηκε αμετάβλητη και το μόνο μέρος που έπρεπε να τροποποιηθεί ήταν το Makefile. Μετά από την επιτυχή κατασκευή των δυναμικών βιβλιοθηκών (dynamic libraries) για το Caffe, έγινε η σύνδεση (linking) ρυθμίζοντας κατάλληλα το Makefile και επιλέγοντας αντί τον προ-υπάρχων μεταγλωττιστή g++, τον ARM cross-compiler για το ενσωματωμένο σύστημα.

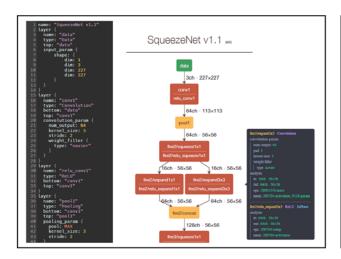

- 3. Τέλος, οι αυστηροί περιορισμοί στην χρήση DNN σε μικρά ενσωματωμένα συστήματα περιλαμβάνουν την περιορισμένη μνήμη της συσκευής (on-chip memory). Για αυτόν τον λόγο, προτιμήθηκε η χρήση σχετικά μικρών μοντέλων νευρωνικών δικτύων (πχ. GoogleNet, SqueezeNet) τα οποία έχουν μικρές απαιτήσεις και παράλληλα προσφέρουν αποδεκτή ακρίβεια.

#### Σχεδιασμός του επιταχυντή υλικού για FPGA

Οι επιταχυντές υλικού χρησιμοποιούνται για να εκφορτώσουν συγκεκριμένες εργασίες από τη CPU, βελτιώνοντας την παγκόσμια απόδοση του συστήματος και μειώνοντας τη δυναμική κατανάλωση ενέργειας. Τα FPGAs μέσα από την αναδιαμορφώσιμη αρχιτεκτονικής τους, μπορούν να αναδείξουν τον παραλληλισμό ενός συγκεκριμένου υπολογιστικά εντατικού κώδικα στο υλικό. Σε αυτή την παράγραφο αναλύουμε τον επιταχυντή υλικού που επιλέξαμε να αναπτύξαμε σε σύνθεση υψηλού επιπέδου (C++) χρησιμοποιώντας το Xilinx SDSoC για τον προγραμματισμό του λογισμικού και υλικού, επιδιώκοντας να επιταχύνουμε την εκτέλεσή του σε σχέση με τον επεξεργαστή ARM του Zynq SoC.

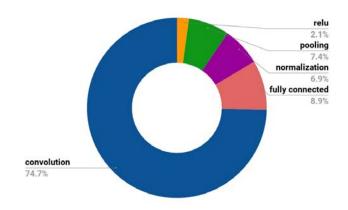

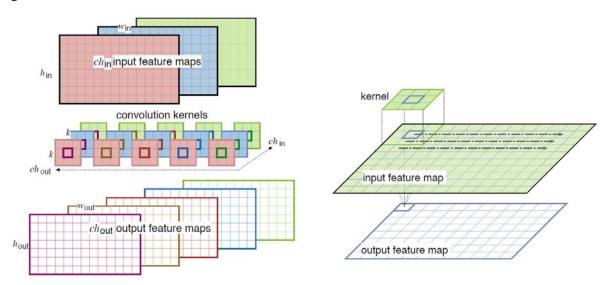

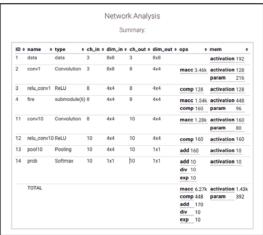

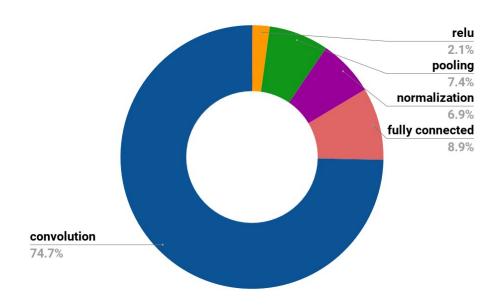

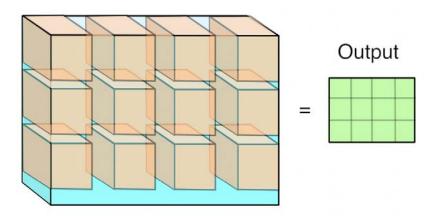

Καθορισμός συνάρτησης για επιτάχυνση Προκειμένου να οριστεί το μέρος του κώδικα προς επιτάχυνση, εκτελέσαμε αρχικά μια αξιολόγηση χρόνου (profiling) στο περιβάλλον του Caffe για τον εντοπισμό των σημείων συμφόρησης μνήμης ή υπολογισμού. Από την Εικόνα 5 φαίνονται τα επίπεδα του νευρωνικού δικτύου που παίρνουν περισσότερο χρόνο (convolution layers). Η Εικόνα 2 δείχνει τον τρόπο με τον οποίο κάνει συνέλιξη το Caffe με τα διάφορα φίλτρα.

Εικόνα 5: Profiling στο Caffe.

Όπως φαίνεται από την εικόνα, τα επίπεδα συνέλιξης στο Caffe (convolution layers) παίρνουν περίπου το 75% του συνολικού χρόνου εκτέλεσης του δικτύου. Οπότε η εξεύρεση των υπολογισμών για επιτάχυνση θα εντοπιστεί σε αυτό το επίπεδο.

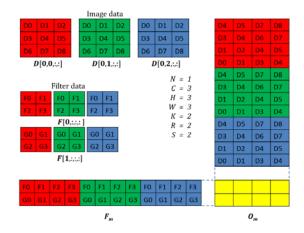

Εικόνα 6: Η συνέλιξη στο Caffe [3].

Όπως παριστάνει η εικόνα, το Caffe πραγματοποιεί συνέλιξη μεταξύ των εισόδων και των φίλτρων του δικτύου μέσα από πράξεις πολλαπλασιασμού πινάκων. Αυτές γίνονται στο Caffe, μέσα από την συνάρτηση GEMM (General Matrix Multiply) που πρόκειται για την συνάρτηση πινάκων  $C = \alpha AB + \beta C$  και εκτελείται από την βιβλιοθήκη BLAS στον ARM επεξεργαστή.

**Βελτιστοποίηση συνάρτησης για επιτάχυνση** Αφού ορίστηκε η συνάρτηση που θα επιταχυνθεί μέσα από το υλικό (GEMM), η διαδικασία προχώρησε στα επόμενα βήματα που αφορούν την ορθή λειτουργία της συνάρτησης GEMM αλλά και τη βελτιστοποίηση την συνάρτησης σε λογισμικό και υλικό.

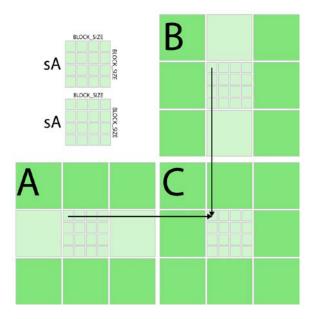

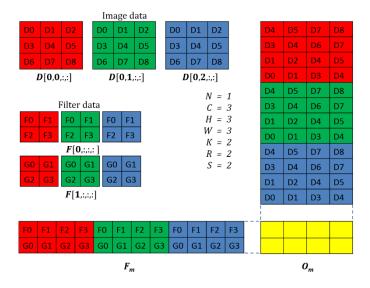

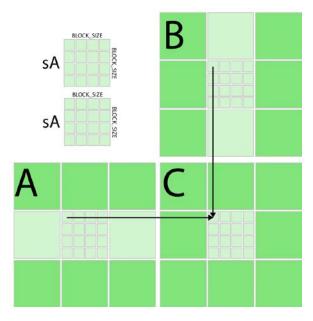

▶ Βελτιστοποίηση \_Λογισμικού: 0 πολλαπλασιασμός των πινάκων πραγματοποιήθηκε με το «σπάσιμο» του πίνακα σε μικρές παρτίδες και τον υπολογισμός των επιμέρους μπλοκ του πίνακα με την τελική την συνένωση αυτών για την οριστική έξοδο του πίνακα C. Αυτό βοήθησε στη ταχύτερη επικοινωνία στη μνήμη καθώς τα μπλοκ φορτώνονταν στην γρήγορη μνήμη cache του επεξεργαστή ARM (μελετήθηκε και το κατάλληλο μέγεθος μπλοκ). Συγκεκριμένα, για τον ορισμό των μπλοκ σε συνεχή μνήμη, χρησιμοποιήσαμε την εντολή το sds\_alloc() αντί για malloc() (αυτό είναι επίσης μια απαίτηση για την εξασφάλιση της γρήγορης επικοινωνίας με τους πυρήνες υλικού που συζητάμε στην επόμενη παράγραφο). Επιπλέον, μια μικρή βελτιστοποίηση που κάναμε ήταν να αντιγράψουμε τη μήτρα Β πριν από την αντίστοιχη μήτρα Α. Αυτό τελικά αποκρύπτει ένα μέρος της συνολικής καθυστέρησης φορτίου, αφού η πρόσβαση της λειτουργικής μονάδας του Α αντιστοιχεί φυσικά στη σειρά με την οποία φορτώνεται, επιτρέποντας στον υπολογισμό να αρχίσει μόλις το πρώτο στοιχείο του Α επιστρέψει από τη μνήμη. Τέλος, για τη γρήγορη αντιγραφή και εκκαθάριση των μπλοκ κάθε φορά, χρησιμοποιήσαμε λειτουργίες memcpy() και memset() αντίστοιχα, οι οποίες είναι ίσως οι ταχύτερες λειτουργίες για το χειρισμό αυτών των υπολογισμών μνήμης στο λογισμικό.

Εικόνα 7: GEMM στον επεξεργαστή.

Όπως παρουσιάζεται στην εικόνα η συνάρτηση GEMM, γίνεται διαμερισμός της πράξης του πολλαπλασιασμού πινάκων σε μικρότερους και τελική συνένωση με το άθροισμά τους στο τελικό πίνακα C. Αξίζει να τονισθεί ότι η συνάρτηση υποστηρίζει και διαφορετικά/ακανόνιστα μεγέθη πινάκων καθώς τα νευρωνικά δίκτυα στο Caffe πολλές φορές απαιτούν «περίεργες» διαστάσεις πινάκων (πχ. A=128x288 B=288x784).

Ακολουθεί η παράγραφος που περιγράφει τις βελτιστοποιήσεις στο υλικό [4].

Όπως αναφέρθηκε, η ο υπολογισμός του τελικού πίνακα γίνεται με μικρότερες πράξεις υποπινάκων οι οποίες και τελικά έχουν όλο το υπολογιστικό φορτίο πράξεων (MACC operations). Σε αυτή την παράγραφο περιγράφουμε τις κυριότερες τεχνικές βελτιστοποίησης του GEMM σε επίπεδο υλικού.

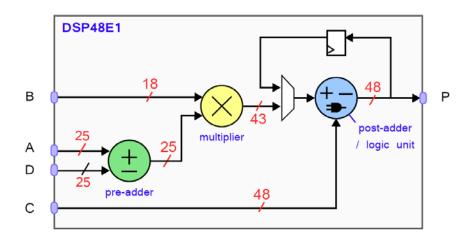

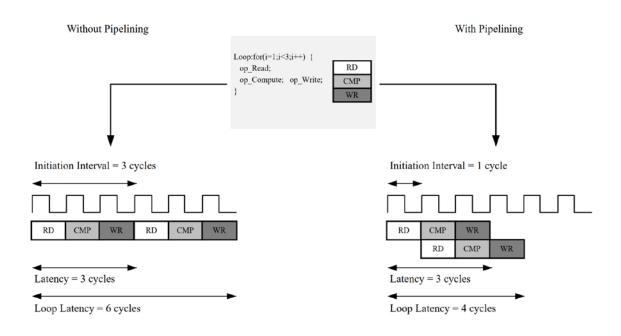

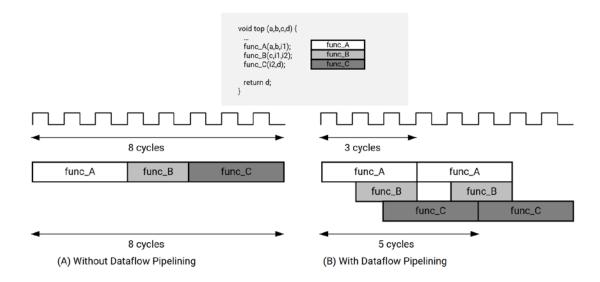

**Βελτιστοποίηση Υλικού**: Για την καθοδήγηση της σύνθεσης και της χρήσης του υλικού χρησιμοποιήθηκαν, μέσα από το SDSoC, συγκεκριμένες ντιρεκτίβες (pragmas) που καθοδηγούν τους πόρους του υλικού και την λειτουργία τους. Όσον αφορά τη διασύνδεση του επιταχυντή με το λογισμικό επιλέχτηκε πρότυπο ΑΧΙ SIMPLE\_DMA με θύρες συστήματος ΑСΡ για σύνδεση με την κύρια μνήμη μέσω του διαύλου ΑΧΙ4 στο Zyng ZC702. Προστέθηκε επίσης η οδηγία #pragma SDS data access\_pattern (array: SEQUENTIAL) στις επιμέρους συναρτήσεις υλικού που προσδιορίζει συνεχές (sequential) μοτίβο πρόσβασης με την διεπαφή (ap\_fifo) για γρήγορη μεταφορά δεδομένων. Επίσης, επιλέξαμε να αποθηκεύσουμε τα δεδομένα του υλικού σε προσωρινούς πίνακες ορισμένους κοντά στον υπολογισμό των πράξεων, προκειμένου να μειώσουμε όσο το δυνατόν περισσότερο την επικοινωνία μνήμης. Για την καθοδήγηση της χρήσης on-chip μνήμης (BRAM) χρησιμοποιήσαμε την οδηγία #pragma HLS RESOURCE variable = <array> core = RAM\_2P\_BRAM για τα μπλοκ πινάκων A και B. Τέλος, για την παραλληλοποίηση της εκτέλεσης τον πράξεων επιλέξαμε την τεχνική της διασωλήνωση (pipeline) τοποθετώντας σε κάθε βρόχο του κώδικα υλικού την ντιρεκτίβα #pragma HLS pipeline II=1 αφού προσέξαμε να μην έχουμε αλληλεξαρτήσεις αποτελεσμάτων μεταξύ τους. Σε συνδυασμό με αυτή την τεχνική, για να αποδεσμεύσουμε τον αριθμό των υπολογιστικών μονάδων (PEs) που ήταν αρχικά περιορισμένες σε ένα μπλοκ μνήμης που δεσμεύσαμε, διαμελίσαμε ισόποσα τους καταχωρητές μνήμης σε περισσότερα BRAMs επιτρέποντας περισσότερες θύρες πρόσβασης και μονάδες υπολογισμού (πχ. DSPs). Αυτό έγινε με τη χρήση της οδηγίας #pragma HLS array\_partition variable=<array> block factor=<N> dim=<dim> μετά την δήλωση των υποπινάκων δίνοντας προσοχή στις ρυθμίσεις της ντιρεκτίβας (πχ. block factor, dim κτλ).

Εικόνα 8: Αρχιτεκτονική υλικού [5].

Όπως φαίνεται στην εικόνα η αρχιτεκτονική του υλικού του FPGA σχεδιάστηκε ώστε να είναι συστολική. Δηλαδή, τα δεδομένα φτάνουν ταυτόχρονα (ανά κύκλο) στις μονάδες επεξεργασίας από διαφορετικά σημεία κάνοντας τους εκάστοτε υπολογισμούς με διασωλήνωση, κατέχοντας μικρή καθυστέρηση μεταφοράς (latency) και γρήγορη ταχύτητα επεξεργασίας.

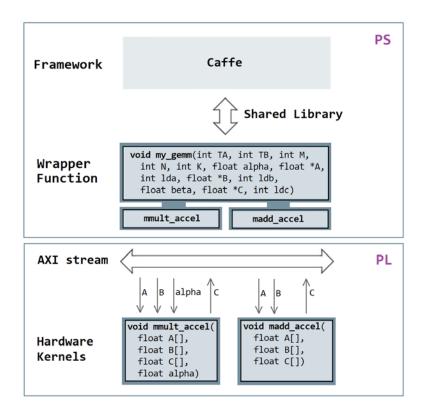

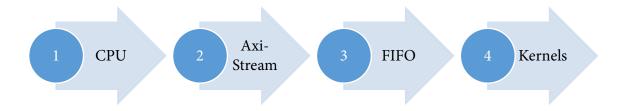

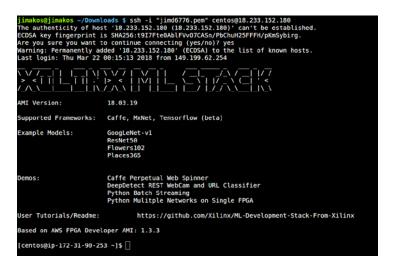

Κατασκευή και λειτουργία του τελικού συστήματος Μετά τη μεταφορά του Caffe στον ARM του Zynq SoC και το σχεδιασμό του επιταχυντή FPGA (GEMM) που θα χρησιμοποιηθεί για την επιτάχυνση του αλγόριθμου ταξινόμησης εικόνας ακολουθεί η ενσωμάτωσή του με το περιβάλλον του Caffe για την πλήρη εκτέλεση του στο FPGA SoC. Αυτή η διαδικασία τα εξής βήματα:

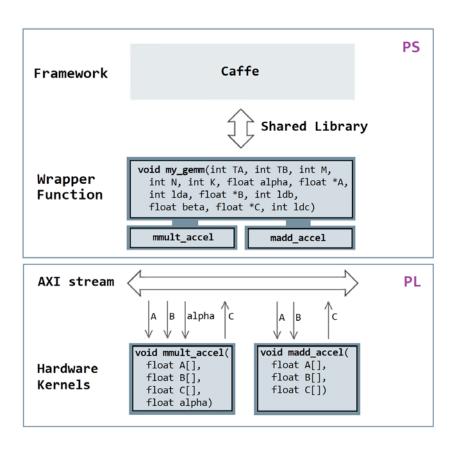

Προκειμένου να ενσωματωθεί ο επιταχυντής υλικού με το περιβάλλον του Caffe και να το μεταφέρουμε στο FPGA SoC, έπρεπε να το εξάγουμε ως κοινή/μοιραζόμενη βιβλιοθήκη αντί για binary εφαρμογή και στη συνέχεια να την συνδέσουμε με το περιβάλλον του Caffe. Μέσα από το SDSoC Development Environment καταφέραμε όχι μόνο να δημιουργήσουμε τη δυναμική/κοινή βιβλιοθήκη (dynamic library) του επιταχυντή, αλλά και το bitstream μαζί με την κάρτα SD από την οποία θα ξεκινούσε το σύστημά μας. Η κοινή βιβλιοθήκη ήταν κατάλληλη για σύνδεση και η λειτουργία του επιταχυντή ενσωματώθηκε με επιτυχία στο πλαίσιο του Caffe, επικοινωνώντας με το υλικό του FPGA όταν χρειαζόταν. Η διαδικασία παρουσιάζεται στην παρακάτω εικόνα.

Εικόνα 9: Λειτουργία συστήματος.

Όπως φαίνεται στο σχήμα, ολόκληρη η διαδικασία ξεκινάει από το Caffe όπου ο χρήστης τρέχει την εντολή αναγνώρισης εικόνας στον επεξεργαστή και στη συνέχεια, κάθε φορά που χρειάζεται να γίνει μια κλήση GEMM, φορτώνει την συνάρτηση μας my\_gemm, εκτελώντας τις πράξεις στο υλικό και μέσω επικοινωνώντας του διαύλου AXI DMA (stream).

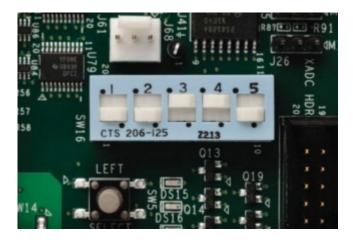

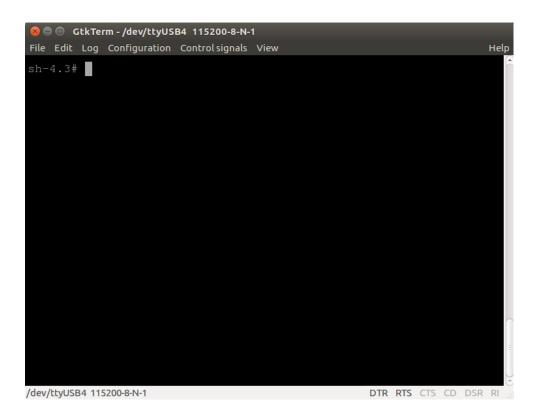

Τέλος, η δημιουργία της κάρτας SD για την εκκίνησης του συστήματος έγινε με εργαλεία SDK από το περιβάλλον SDSoC. Λήφθηκε υπόψη το bitstream από τον επιταχυντή υλικού καθώς προστέθηκε στην εικόνα εκκίνησης. Επιπλέον, για το ενσωματωμένο σύστημα, προτιμήθηκε το ελαφρύ λειτουργικό σύστημα της Xilinx Petalinux αφού παρείχε όλες τις απαραίτητες λειτουργίες που έχει ένα αντίστοιχο λειτουργικό Linux. Για την ρύθμιση του FPGA για λειτουργία, επιλέχτηκε σειριακό πρωτόκολλο επικοινωνίας με το Desktop PC μέσω της θύρας UART, επικοινωνώντας με το λειτουργικό μέσα από το πρόγραμμα TerraTerm.

## Αξιολόγηση και Αποτελέσματα

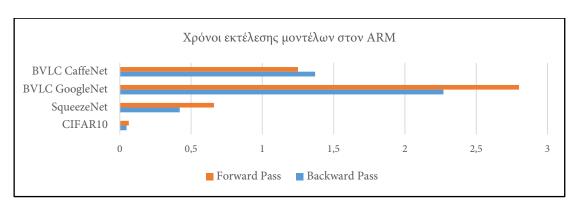

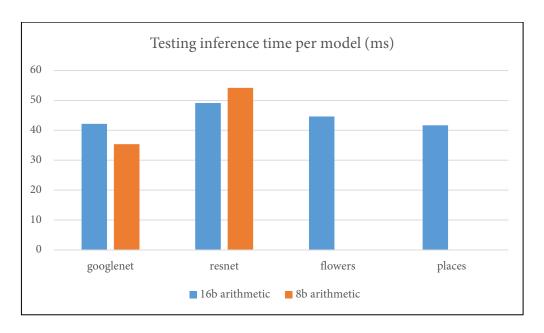

Απόδοση Caffe στον ενσωματωμένο επεξεργαστή Στην παράγραφο αυτή περιορίζουμε τα αποτελέσματα σε μια περίληψη των πιο σημαντικών χαρακτηριστικών της λειτουργίας του περιβάλλοντος του Caffe στον ARM CPU. Αρχικά, παρέχουμε αρκετές μετρήσεις στο Caffe σχετικά με τη λειτουργία του (ακρίβεια πρόβλεψης, χρόνος εκτέλεσης κ.λπ.) και στη συνέχεια αναλύουμε ορισμένα χαρακτηριστικά ορισμένων μοντέλων νευρωνικών δικτύων παρουσιάζοντας την εσωτερική δομή πίσω από την λειτουργία τους.

| GoogleNet                                      | SqueezeNet                                     |

|------------------------------------------------|------------------------------------------------|

|                                                |                                                |

| real 0m8.597s<br>user 0m9.860s<br>sys 0m1.430s | real 0m1.228s<br>user 0m1.530s<br>sys 0m0.510s |

Εικόνα 10: Αναγνώριση εικόνας μέσα από το Caffe στον ARM σε διαφορετικά μοντέλα.

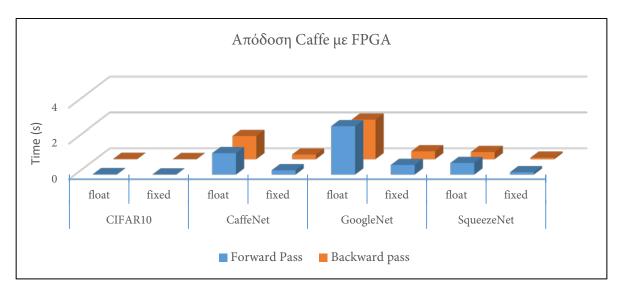

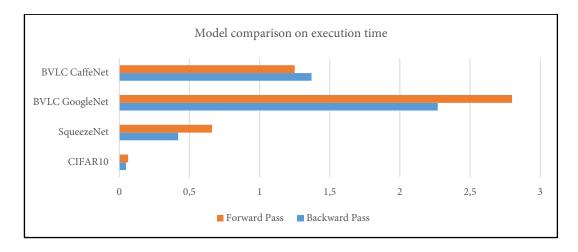

Εικόνα 11: Σύγκριση χρόνων για συμπέρασμα (forward pass) και εκμάθηση (backward pass).

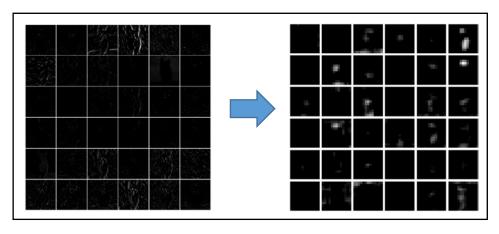

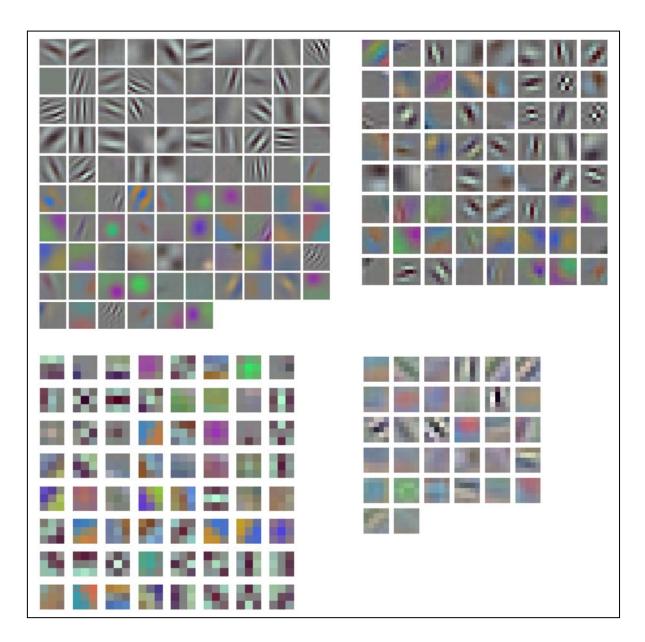

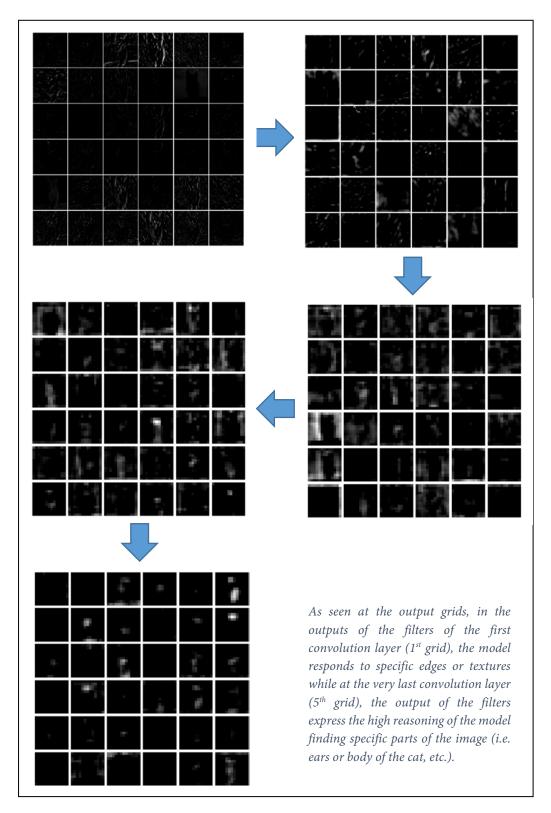

Εικόνα 12: Σύγκριση απόκρισης εξόδου από 1° σε 5° επίπεδο συνέλιξης στο μοντέλο του CaffeNet

Απόδοση επιταχυντή στο FPGA Στην παράγραφο ξεκινάμε με την ανάλυση λειτουργίας του επιταχυντή σχετικά με την καθυστέρηση, την ανάλυση κίνησης δεδομένων, την χρήση των διαθέσιμων πόρων κ.λπ. Στη συνέχεια, δίνουμε αρκετές μετρήσεις για τον επιταχυντή υλικού σχετικά με την επιτάχυνση από το ARM χρησιμοποιώντας ένα πρόγραμμα C ++ σαν test-bench για τον προσδιορισμό της απόδοσης.

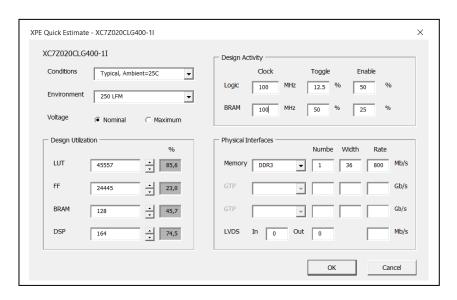

Πίνακας 1: Κατανομή πόρων επιταχυντή σε ZC702 FPGA Floating Point (αριστερά), Fixed Point (δεξιά)

| Resource | Used  | Total  | %Utilization |

|----------|-------|--------|--------------|

| DSP      | 164   | 220    | 75,55        |

| BRAM     | 128   | 140    | 91,43        |

| LUT      | 45557 | 53200  | 85,63        |

| FF       | 24445 | 106400 | 22,97        |

| Resource | Used  | Total  | %Utilization |

|----------|-------|--------|--------------|

| DSP      | 193   | 220    | 87,73        |

| BRAM     | 96    | 140    | 68,57        |

| LUT      | 36681 | 53200  | 68,95        |

| FF       | 26683 | 106400 | 25,08        |

Πίνακας 2: Σύνοψη καθυστέρησης στους βρόχους (κύκλοι ρολογιού). Floating Point (αριστερά), Fixed Point (δεξιά)

|           | Latency |        | Iteration | Initiation Interval |        | Trip  | Pipelined |

|-----------|---------|--------|-----------|---------------------|--------|-------|-----------|

| Loop Name | min     | max    | Latency   | achieved            | target | Count |           |

| -Loop1    | 36875   | 36875  | 13        | 1                   | 1      | 36864 | yes       |

| -Loop2    | 222143  | 222143 | 966       | 6                   | 1      | 36864 | yes       |

|           | Latency |       | Iteration | Initiation | Interval | Trip  | Pipelined |

|-----------|---------|-------|-----------|------------|----------|-------|-----------|

| Loop Name | min     | max   | Latency   | achieved   | target   | Count |           |

| -Loop1    | 36870   | 36870 | 8         | 1          | 1        | 36864 | yes       |

| -Loop2    | 37254   | 37254 | 392       | 1          | 1        | 36864 | yes       |

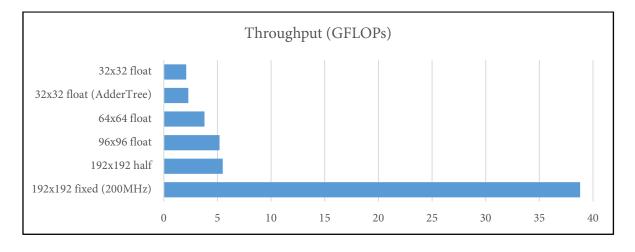

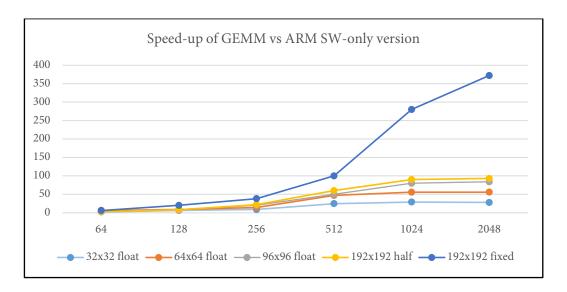

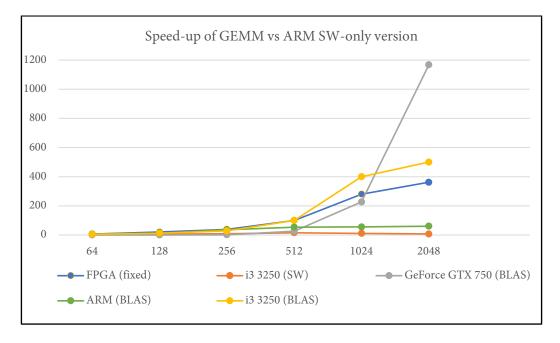

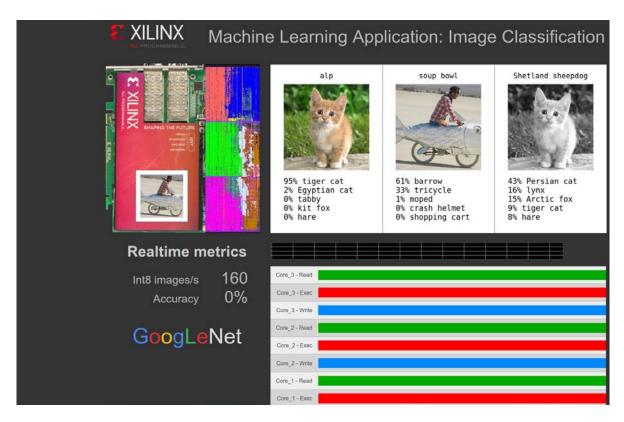

Τέλος για την αξιολόγηση του επιταχυντή έγιναν διάφορες δοκιμές όσον αφορά το μέγεθος του μπλοκ ή την ακρίβεια στην πράξη (πχ. Float/Fixed point). Πρωτεύουσα θέση κατείχε η υλοποίηση σε fixed point καθώς ελαχιστοποιούσε τον απαιτούμενο αριθμό πόρων και την καθυστέρηση επιτυγχάνοντας μέχρι και 38 GFLOPs σε επίδοση kernels υλικού με ρολόι 200MHz και τελική επιτάχυνση συνάρτησης GEMM στα 380×.

Εικόνα 13: Σύγκριση χρόνου σε διαφορετικές υλοποιήσεις της συνάρτησης GEMM

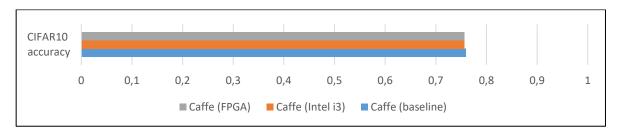

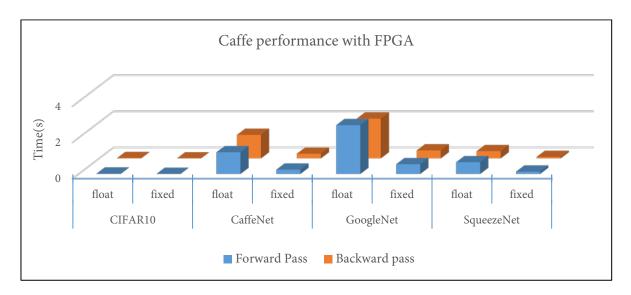

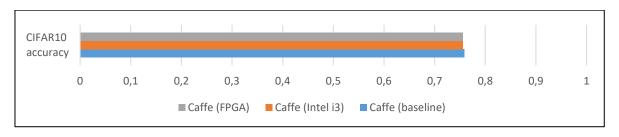

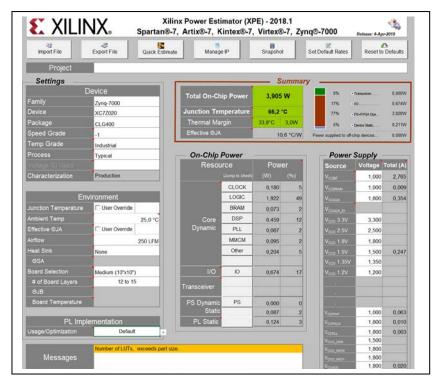

Απόδοση Caffe στο FPGA Soc Μετά την ενσωμάτωση του επιταχυντή υλικού που σχεδιάσαμε με το πλαίσιο Caffe, θέλαμε να μετρήσουμε τη συνολική απόδοση του Caffe στο ετερογενές CPU-FPGA Soc (ZC702) και να το συγκρίνουμε με την υλοποίηση αριθμητικής ακρίβειας float και fixed point στον επιταχυντή (η υλοποίηση fixed είναι προσομοιωμένη). Έτσι, σε αυτή τη παράγραφο μετράμε την απόδοση αναγνώρισης εικόνας και την ακρίβεια στο νέο τροποποιημένο πλαίσιο του Caffe στο FPGA που χρησιμοποιεί τον επιταχυντή GEMM και αξιολογούμε την κατανάλωση ισχύος και ενέργειας του συστήματός μας.

Εικόνα 14: Σύγκριση χρόνου για συμπέρασμα (forward pass) και εκμάθηση (backward pass) για διαφορετικές υλοποιήσεις της συνάρτησης GEMM σε διαφορετικά μοντέλα.

Εικόνα 15: Σύγκριση ακρίβειας πρόβλεψης σε διαφορετικές υλοποιήσεις

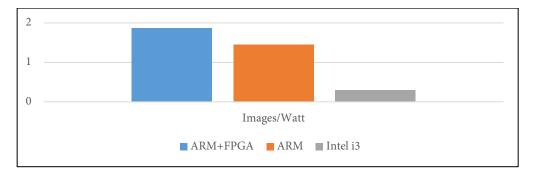

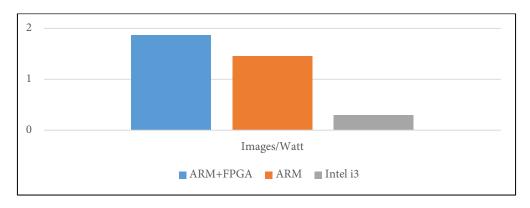

Εικόνα 16: Απόδοση ενέργειας τελικού συστήματος σε διάφορες αρχιτεκτονικές. Η υλοποίηση με FPGA καταναλώνει 3,905W και όπως φαίνεται στη εικόνα έχει 7 φορές καλύτερη ενεργειακή απόδοση/Watt σε σχέση με τον Intel i3 επεξεργαστή (προσομοιωμένο με υλοποίηση fixed point αριθμητική ακρίβεια).

#### Συμπεράσματα

Τα Νευρωνικά Δίκτυα Βαθιάς Μάθησης (DNNs) αντιπροσωπεύουν ένα καθολικό μοντέλο, το οποίο μπορεί να αξιοποιηθεί για να επιλύσει μια μεγάλη ποικιλία προβλημάτων. Στον τομέα αυτό, τα FPGAs μπορούν να βελτιώσουν σημαντικά την απόδοση και την ενέργεια αυτών των εφαρμογών χρησιμοποιώντας επιταχυντές υλικού (hardware accelerators). Ωστόσο, πλατφόρμες για υλοποίηση DNN, όπως το Caffe, δεν υποστηρίζουν επίσημα τη ευκολοδιάκριτη χρήση τέτοιων συστημάτων επιτάχυνσης.

Αυτό το έργο παρουσιάζει ξεκάθαρα την ανάπτυξη DNN στο Xilinx FPGA SoC χρησιμοποιώντας το περιβάλλον του Caffe ταυτόχρονα με τη χρήση επιταχυντών υλικού για να επιτύχει καλύτερη απόδοση. Μεταγλωττίσαμε πρώτα ολόκληρο το περιβάλλον του Caffe και όλες τις εξαρτήσεις βιβλιοθηκών για να δουλέψουν και να τρέχουν στον ενσωματωμένο επεξεργαστή ARM με τη μέθοδο cross-compilation. Στη συνέχεια, μέσω της πλήρους αξιολόγησης της λειτουργίας του περιβάλλοντος, προσδιορίσαμε τα σημεία υπολογιστικής συμφόρησης για να καθορίσουμε τη σωστή συνάρτηση επιτάχυνσης υλικού η οποία ήταν τελικά η συνάρτηση GEMM (General Matrix Multiplication). Στη συνέχεια περιγράψαμε τις στρατηγικές βελτιστοποίησης στο λογισμικό αλλά και στον επιταχυντή υλικού ώστε να αξιοποιήσουμε τον μαζικό παραλληλισμό και τους διαύλους επικοινωνίας της μνήμης του FPGA. Ο επιταχυντής FPGA έχει συντεθεί με Σύνθεση Υψηλού Επιπέδου (C++) χρησιμοποιώντας το περιβάλλον ανάπτυξης Xilinx SDSoC για το Xilinx Zyng ZC702 SoC και φτάνει επιτάχυνση μέχρι και 380x με τη μέγιστη συχνότητα ρολογιού των 200MHz και με χρήση πόρων στο ~80%. Η αξιολόγηση και η επαλήθευση της συνάρτησης υλικού ήταν επιτυχής, παράγοντας σωστά αποτελέσματα για διαφορετικά μεγέθη και διαστάσεις πινάκων. Τέλος, ενσωματώσαμε τον επιταχυντή υλικού με το πλαίσιο Caffe και το έτρεξε με επιτυχία στο ετερογενές σύστημα CPU-FPGA το οποίο αξιοποιεί την αρχιτεκτονική FPGA με το επιταχυντή υλικού που σχεδιάσαμε. Για την τελική αξιολόγηση του συστήματος μετρήσαμε την απόδοση της αναγνώρισης εικόνων και τα αποτελέσματα έδειξαν ότι το προτεινόμενο σύστημα μπορεί να μειώσει το χρόνο αναγνώρισης μέχρι και 10% σε σύγκριση με τον επεξεργαστή ARM και επίσης να μειώσει την κατανάλωση ενέργειας έχοντας λιγότερο από 0.4% μείωση ακρίβειας.

Το σύστημα βασισμένο σε CPU-FPGA με υποστήριξη του περιβάλλοντος Caffe έχει συναρμολογηθεί σε ένα πλήρως λειτουργικό σύστημα στην πλατφόρμα Xilinx Zynq-7000 All Programmable SoC. Αυτό το σχέδιο καταδεικνύει σαφώς τη σκοπιμότητα υλοποίησης ενσωματωμένων DNN βασισμένα σε FPGA. Η τρέχουσα λύση παρουσιάζει ήδη μια αποδοτική εκτέλεση και λειτουργία του συστήματος αυτού καθώς έχουν επισημανθεί αρκετές τεχνικές για σημαντικά κέρδη στην απόδοση και την κατανάλωση ενέργειας.

1 Introduction

#### 1.1 Motivation

The continuing exponential increase of media, IoTs and big data in general requires faster and faster processing speeds while the applications must maintain a low power cost and keep the development time small. Many high performance systems rely on machine learning (ML) algorithms such as image classification, data analytics etc. which are required for embedded and big data applications as well. Hardware and device makers are in a mad dash to create or acquire the perfect chip for performing deep learning training and inference.

In this field, Deep Convolutional Neural Networks (DNNs) have gained significant traction due to the fact that they offer state-of-the-art accuracies and important flexibility. These brain-inspired algorithms use techniques from machine learning which enables them to rival the accuracy of humans when it comes to classification of images. Although a serious amount of computation is needed to analyze the large amounts of data, the use of multicore systems seems promising but the challenge of reducing the high energy cost and the processing times remains. FPGA implementations on the other hand have seen great advancement as new emerging techniques leverage the FPGA architecture taking advantage of the high performance hardware accelerators with few power costs while keeping the adaptability of fast prototyping. With the utilization of hardware accelerators the total throughput is increased because of the highly parallelizable massive number of multiply-accumulate operations that DNN algorithms need and also the energy consumption is decreased. Caffe, a deep learning framework of UC Berkley, has already been implemented and optimized in two different architectures for CPU and GPU only and can be easily configured without hard-coding.

- In this paper we present:

- A modified version of Caffe to effortlessly port it into the ARM (Zynq 7000 based) processor of FPGA.

- A hardware accelerator designed on Xilinx SDSoC Environment that exploits the benefits of FPGA and is crucial for the image classification algorithm.

- A CPU-FPGA-based system, a highly heterogeneous all-programmable SoC that supports the Caffe framework and utilizes the hardware accelerator achieving significant speed and power efficiency compared to the ARM Zynq processor.

## 1.2 Chapter Organization

The thesis is organized as follows:

Chapter 2 provides background information on Machine Learning and Neural Networks, architecture and design of FPGAs, and at the end gives an analysis of Caffe Deep Learning framework. In the first section, a brief overview is given of Machine Learning concepts and related applications in this field. Next, a detailed presentation of Neural Networks is provided and then Deep Neural Networks are analyzed along with Image Recognition implementations. Then, in the second section, we discuss the design and architecture of FPGAs along with presenting design methods, such as High Level Synthesis, and their purpose in creating hardware accelerators for boosting applications performance. Last, we provide information of the operation of Caffe Deep Learning Framework.

Chapter 3 is dedicated on how we ported the whole Caffe framework in ARM CPU of the Zynq SoC in order to run it on the embedded system. Detailed information is given on the steps of this process in order to run Caffe with full support (image recognition, model benchmarks etc.) on the ARM processor and optimize in order to overcome the embedded system's physical constraints.

Chapter 3 consists of the design and optimization schemes used for the FPGA hardware accelerator that was used to accelerate the Caffe framework and specifically image recognition in the embedded SoC. The optimization and design strategies included both software and hardware techniques for maximum performance in throughput, parallelism and communication.

Chapter 5 gives a detailed analysis and evaluation of Caffe running on the embedded CPU, the designed hardware accelerator and last the results of the final heterogeneous CPU-FPGA system that runs and accelerates image recognition on Caffe utilizing the hardware accelerator. This chapter provides the appropriate testing and benchmark results of the proposed system and the performance and hardware analysis of the FPGA accelerator.

Chapter 6 summarizes the important results obtained by this research and gives suggestions on future work valuable to the reader.

# 2

# Background

# 2.1 Introduction to Machine Learning

Machine Learning at its most basic is the practice of using algorithms to parse data, learn from it, and then make a determination or prediction about something in the world. So rather than hand-coding software routines with a specific set of instructions to accomplish a particular task, the machine is "trained" using large amounts of data and algorithms that give it the ability to learn how to perform the task. Thus, the core objective is to generalize from its experience and perform accurately on new, unseen examples/tasks after having experienced a learning data set. The training examples come from some generally unknown probability distribution and the learner has to build a general model about this space that enables it to produce sufficiently accurate predictions in new cases.

Machine learning tasks are typically classified into two broad categories, depending on whether there is a learning "signal" or "feedback" available to a learning system:

- Supervised learning: The computer is presented with example inputs and their desired outputs, given by a "teacher", and the goal is to learn a general rule that maps inputs to outputs.

- Unsupervised learning: No labels are given to the learning algorithm, leaving it on its own to find structure in its input. Unsupervised learning can be a goal in itself (discovering hidden patterns in data) or a means towards an end (feature learning).

There are many approaches to machine learning tasks. Some of them include:

- Artificial neural network (ANN): a learning algorithm, usually called "neural network" which is inspired by biological neural networks. They are usually used to model complex relationships between inputs and outputs, to find patterns in data, or capture the statistical structure in unknown distributions.

- Clustering: an analysis that assigns a set of observations into subsets (called clusters) so that observations within the same cluster are similar according to some predesignated criterion or criteria, while observations drawn from different clusters are dissimilar.

- Genetic algorithm: a heuristic search that mimics the process of natural selection, and uses methods such as mutation and crossover to generate new genotype in the hope of finding good solutions to a given problem.

#### 2.2 Introduction to Convolutional Neural Networks

A convolutional neural network is one type of machine learning model which has great practical value in the field of pattern recognition. They are distinguished for their state-of-the-art behavior because they can automatically create both high level and low level features.

#### 2.2.1 Brain analogy

Convolutional neural networks (CNNs) were inspired by biological processes in which the connectivity pattern between neurons is inspired by the organization of the animal visual cortex. Individual cortical neurons respond to stimuli only in a restricted region of the visual field known as the receptive field. The receptive fields of different neurons partially overlap such that they cover the entire visual field. So, in a way it behaves similarly to the human brain, that is to simulate its densely interconnected brain cells using digital neurons that trigger or respond when they 'sense' certain features regardless of the feature position in the visual field.

Modeling of a neuron The basic building block in artificial neural networks is the neuron. The diagram below shows a drawing of a biological neuron (left) and a common mathematical model (right). Each neuron receives input signals from its dendrites and produces output signals along its (single) axon. The axon eventually branches out and connects via synapses to dendrites of other neurons. In the computational model of a neuron, the signals that travel along the axons (e.g. x0) interact multiplicatively (e.g. w0x0) with the dendrites of the other neuron based on the synaptic strength at that synapse (e.g. w0). The idea is that the synaptic strengths (the weights w) are learnable and control the strength of influence of one neuron on another. In the basic model, the dendrites carry the signal to the cell body where they all get summed. If the final sum is above a certain threshold, the neuron can fire, sending a spike along its axon. Based on this rate code interpretation, we model the firing rate of the neuron with an *activation function f*, which represents the frequency of the spikes along the axon. Historically, a common choice of activation function is the *sigmoid function \sigma*, since it takes a real-valued input (the signal strength after the sum) and squashes it to range between 0-1.

Figure 2.1: A biological neuron (left) and its mathematic model (right) [1].

**Neural Network** A neural network is formed by interconnecting many artificial neurons. The neurons are arranged in a directed acyclic graph in a *feed-forward network* although some architectures are using multilayer perceptrons in which the neurons are organized in layers. In other words, the outputs of some neurons can become inputs to other neurons. Cycles are not allowed since that would imply an infinite loop in the forward pass of a network. There are input and output layers and additional hidden layers that many times increase network size and complexity. As stated before, each neuron assigns a weighting to its input that is how correct or incorrect it is relative to the task being performed. The final output is then determined by the total of those weightings.

Figure 2.2: The organization of multiple layers of neurons [1].

#### 2.2.2 Operation of a multi-layer network

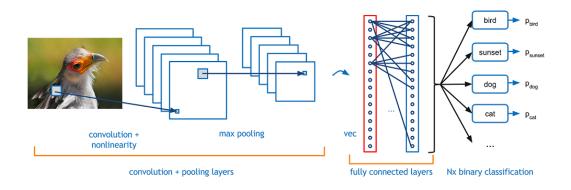

Layers Types Convolutional Neural Networks use many different interconnected layers, as shown in the previous figure, specifically designed among other tasks to recognize or detect 2-dimensional image data. A Neural Network can have different layers performing unique tasks aiming to give a specific output that is passed through the other layers. Some of the fundamental layers found in many models are:

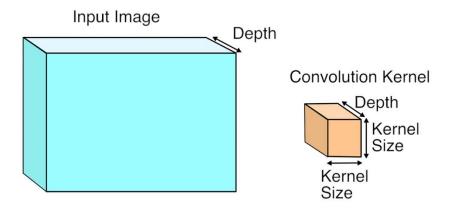

- Convolutional Layer applies a convolution operation to the input, passing the result to the next layer. The convolution emulates the response of an individual neuron to visual stimuli. Each convolutional neuron processes data only for its receptive field. Convolutional layers take several feature maps as input and using convolution with the filter weights  $k \times k$  acquired from the training process they produce feature maps as output. For filters larger than  $1 \times 1$ , border effects reduce the output dimensions. To avoid this effect, the input image is typically padded with zeros on each side thus reducing the output dimensions.

- Nonlinearity Layer apply a non-linear activation function to each input pixel. The most popular activation function is the Rectified Linear Unit (ReLU) which computes  $f(x) = \max(0, x)$  and clips all negative elements to zero. Other networks use sigmoidal functions such as  $f(x) = 1/(1 + e^{-x})$  or  $f(x) = \tanh(x)$ .

- Pooling Layer combines the outputs of neuron clusters at one layer into a single neuron in the next layer by summarizing multiple input pixels into one output pixel. For example, max pooling uses the maximum value from each of a cluster of neurons at the prior layer. Another example is average pooling, which uses the average value from each of a cluster of neurons at the prior layer. They are usually applied to a patch of 2x2 or 3x3 input pixels, but can also be applied as global pooling to the whole input image.

- Fully Connected Layer connects every neuron in one layer to every neuron in another layer. Each output value of a Fully Connected layer looks at every value in the input layer, multiplies them all by the corresponding weight it has for that input index, and sums the results to get its output. They can be visualized as one dimensional and perform the high level reasoning in the neural network.

- *Dropout Layer* is a popular method to combat overfitting in large CNNs. These layers randomly drop a selectable percentage of their connections during training which prevents the network from learning very precise mappings and forces some abstraction and redundancy to be built into the learned weights.

- Softmax Layer are often used in the final layer of a neural network-based classifier. It converts the raw class scores  $z_i$  into class probabilities  $P_i$  according to  $P_i = e^{z_i}/\sum_k e^{z_k}$ , which result in a vector P that sums up to 1.

**Training of a Neural Network** Neural networks can be trained and their parameters are learned during this phase. The network can learn and find the optimal weights, by defining a loss function and using the *backpropagation* algorithm to adapt weights. The most popular approach is called supervised training and requires a set of labeled examples. The training starts with small, maybe random, initial weights and each example is fed through the network many times to produce better results (*feed-forward pass*). The network is considers to be trained after reaching the target performance results on the training data. The *backpropagation* algorithm works by calculating the loss from the current network output and a ground truth and computing a weight update from it by passing the error backwards through the network (*backward-pass*). The goal of the learning process is to minimize this loss by updating training weights. The magnitude of these updates is determined by the so-called *learning rate*.

Below is a basic optimization algorithm called *Stochastic Gradient Descent* that minimizes the loss function. It consists in using a few examples to compute the gradient of the parameters with respect to loss function:

$$\theta_{t+1} = \theta_t - \lambda \cdot \nabla_{\theta_t} L(f_{\theta_t}(x_i), y_i)$$

There is no proof of good convergence. However, this algorithm reaches good local minima in practice, even when the parameters are randomly initialized. One of the reason could be the stochastic property of this algorithm, allowing the latter to optimize different loss functions and thus to get out of bad minima. The other reason could be that a lot of local minima are almost as accurate as the global minima. Answers to this question are still under active research.

**Image Classification** After training, the neural network is built and is ready to recognize images on new data through a process called *inference*. In this setting, the aim is to compute the output of the network. Colors of the image are represented as RGB values (a combination of red, green and blue ranging from 0 to 255). Computers could then extract the RGB value of each pixel and put the result in an array for interpretation which will be fed throughout all the layers of the network. Then the input image is scanned for features using small filters. This feature extraction starts with the input image where each pixel represents the input for the neurons grouped in features. The neurons in the feature maps are organized in 2-dimensional grids.

Figure 2.3: Left: Illustration of data inside a CNN Layer (left). The *ch<sub>in</sub>* input feature maps are transformed into *ch<sub>out</sub>* output feature maps by applying *ch<sub>in</sub>* x *ch<sub>out</sub>* filter kernels of size k x k.

Right: Illustration of a 2D convolution between 3x3 kernel and an input feature map by sliding the kernel over the input pixels and performing MACC operations at each pixel position [6].

The input is followed by alternating layers of convolution, pooling and others. The process of a CNN can involve numerous hidden layers besides convolutional and pooling which the data is fed through. After passing all layers, the network produces a final result vector with a possibility  $P_i$  for each category of our model.

Figure 2.4: The organization of multiple layers of neurons [2].

#### 2.2.3 Network Topologies

A lot of convolutional architectures have been developed from the 1990's. In this section, we make an inventory of the most known architectures. Each one represent a step further for more advanced visual recognition.

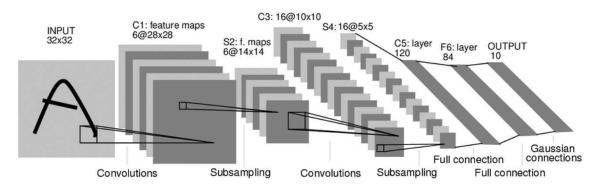

**LeNet** This kind of architecture is one of the first successful applications of CNNs. It was developed by Yann LeCun in the 1990's and was used to read zip codes and digits. This architecture, with regard to the modern ones, differs on many points. Thus, we will limit ourselves on the most known, LeNet-5, and we will not delve into the details. In overall this network was the origin of much of the recent architectures, and a true inspiration for many people in the field.

LeNet-5 features can be summarized as:

- sequence of 3 layers: convolution, pooling, non-linearity

- inputs are normalized using mean and standard deviation to accelerate training

- sparse connection matrix between layers to avoid large computational cost

- hyperbolic tangent or sigmoid as non-linearity function,

- trainable average pooling as pooling function,

- fully connected layers as final classifier,

- mean squared error as loss function.

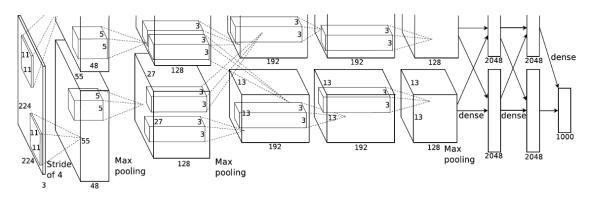

Figure 2.5: Architecture of LeNet-5, a convolutional neural network for digits recognition [7].

**AlexNet** It is one of the first work that popularized convolutional networks in computer vision. AlexNet was submitted to the ImageNet ILSVRC challenge of 2012 and significantly outperformed the other hand crafted models (accuracy top5 of 84% compared to the second runner-up with 74%). This network, compared to LeNet, was deeper (60 millions of parameters) and bigger (5 convolutional layers, 3 max pooling and 3 fully-connected layers). It popularized:

- the ReLU as non-linearity function of choice

- the method of stacking convolutional layers plus non-linearity on top of each other without being immediately followed by a pooling layer

• the method of overlapping Max Pooling, avoiding the averaging effects of Average Pooling.

Figure 2.6: Architecture of AlexNet [8].

**VggNet** It was the runner-up architecture of ILSVRC2014 with almost 140 millions of parameters. Its main contributions were to show that depth is a critical component for good performance, to use much smaller 3×3 filters in each convolutional layers and also to combine them as a sequence of convolutions. The great advantage of VggNet was the insight that multiple 3×3 convolution in sequence can emulate the effect of larger receptive fields, for examples 5×5 and 7×7. However, having so many weights, one forward pass requires nearly 16 billion MACC operations (multiply-accumulate operations).

**GoogleNet** GoogLeNet or Inception was the winner architecture of ILSVRC2014. Its main contribution was the development of an Inception Module that dramatically reduced the number of parameters (40 millions). Also, it eliminated a large amount of parameters by using average pooling instead of fully connected layers at the top of the convolutional layers. Further versions of the GoogLeNet has been released. The most recent architecture available is InceptionV3. Notably, it uses batch normalization.

**ResNet** It was the winner architecture of ILSVRC2015 with 152 layers. Its main contribution was to use batch normalization and special skip connections for training deeper architectures. ResNet with 1000 layers can be trained with those techniques. However, it has been empirically found that ResNet usually operates on blocks of relatively low depth which act in parallel, rather than serially flow the entire length of the network.

**SqueezeNet** It differs from the other CNN architectures in this list due to the fact that the design was not record-breaking in accuracy. Instead, the authors developed a network with an accuracy similar to AlexNet but with 50x less parameters. This parameter reduction has been achieved by using fire modules, a reduce-expand micro-architecture comparable to Inception modules, and careful balancing of the architecture. The 18-layer SqueezeNet uses 7x7, 3x3 and 1x1 convolutions, 3x3 max pooling, dropout and global average pooling, but

neither fully connected, nor Batch Normalization layers. One forward pass requires only 860 million MACC operations and 1.24 million parameters are enough to achieve less than 19.7% single-crop top-5 error.

Comparison of Topologies A common performance measure for deep CNNs is their classification accuracy. Most researchers give their performance numbers in top-1 and top-5 measure. The top-1 error measure gives the percentages of images that were classified incorrectly on the test set. Since the ImageNet data set has very fine-grained image classes which are sometime even hard for humans to distinguish, most researchers prefer to use the top-5 error measure. Hence, an image is considered as classified correctly if one of the top 5 predictions are correct. On the other hand, some research tend to focus on creating smaller networks that can achieve good classification performance. In the table below, there can be seen the tradeoff between accuracy and network size. For example VGG has a great accuracy but it is also the largest network in terms of parameter size and MACC operations. On the contrary, SqueezeNet which is a small network designed for mobile devices is not as accurate but has a drastically reduced size.

Table 2.1: Comparison of different CNN Topologies for Image Classification on ImageNet

|              | #conv. layers | #MACCs<br>[millions] | #params<br>[millions] | #activations<br>[millions] | ImageNet<br>top-5 error |

|--------------|---------------|----------------------|-----------------------|----------------------------|-------------------------|

| AlexNet      | 5             | 1140                 | 62.4                  | 2.4                        | 19.7%                   |

| VGG-16       | 16            | 15470                | 138.3                 | 29.0                       | 8.1%                    |

| GoogleNet    | 22            | 1600                 | 7.0                   | 10.4                       | 9.2%                    |

| ResNet-50    | 50            | 3870                 | 25.6                  | 46.9                       | 7.0%                    |

| Inception v3 | 48            | 5710                 | 23.8                  | 32.6                       | 5.6%                    |

| SqueezeNet   | 18            | 860                  | 1.2                   | 12.7                       | 19.7%                   |

# 2.3 FPGAs

A field-programmable gate array (FPGA) is an integrated circuit designed to be configured by a customer or a designer after manufacturing – hence "field-programmable" and its development started in the late 1980s. The FPGA configuration is generally specified using a hardware description language (HDL), similar to that used for an application-specific integrated circuit (ASIC) and they aim to perform a computational intensive task. Their advantage lies in that they are sometimes significantly faster for some applications because of their parallel nature and optimality in terms of the number of gates used for a certain process.

#### 2.3.1 Introduction to FPGA

An FPGA is a semiconductor device and usually contains a large integrated circuit that can be used to create custom logic functions and perform specific tasks as a digital circuit. Reprogrammable silicon also has the same flexibility of software running on a processor-based system, but it is not limited by the number of processing cores available. Unlike processors, FPGAs are truly parallel in nature, so different processing operations do not have to compete for the same resources. Each independent processing task is assigned to a dedicated section of the chip, and can function autonomously without any influence from other logic blocks. As a result, the performance of one part of the application is not affected when you add more processing because the application logic is implemented in hardware circuits rather than executing on top of an OS, drivers, and application software.

**FPGA Architecture** FPGAs consist of 2D array of configurable logic blocks (also 3D stacked architectures have been introduced) which are connected via programmable interconnects to implement a reconfigurable digital circuit and I/O blocks to allow the circuit to access the outside world. FPGAs resource specifications often include the number of configurable logic blocks, number of fixed function logic blocks such as multipliers, and size of memory resources like embedded block RAM.

Figure 2.7: The inside architecture of the FPGA [9].

The basic structure components of the FPGA are described below:

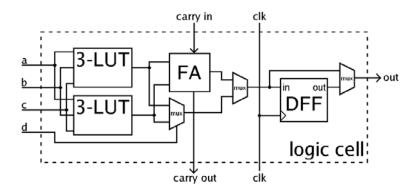

• Configurable Logic Blocks (CLB): In general, a logic block consists of a few logical cells (called ALM, LE, slice etc.). A typical cell consists of a 4-input LUT, a full adder (FA) and a D-type flip-flop, as shown below. The Lookup Tables (LUT) are in this figure split into two 3-input LUTs. In normal mode those are combined into a 4-input LUT through the left mux. In arithmetic mode, their outputs are fed to the FA. The selection of mode is programmed into the middle multiplexer. The output can be either synchronous or asynchronous, depending on the programming of the mux to the right, in the figure example. In practice, entire or parts of the FA are put as functions into the LUTs in order to save space [10].

Figure 2.8: Simplified example illustration of a logic cell [10].

- Programmable Interconnects: The interconnects can be thought of as a network of wire bundles running vertically and horizontally between the logic slices. They provide connections among logic blocks and I/O blocks to implement any user-defined circuit. The routing interconnect of an FPGA consists of wires and programmable switches that form the required connection. These programmable switches are configured using the programmable technology.

- External I/O Blocks: Since clock signals are normally routed via special-purpose dedicated routing networks in commercial FPGAs, they and other signals are separately managed. These blocks enable the FPGA to communicate with other parts of the system and send/receive external signals.

- Hard Blocks: Modern FPGA families expand upon the above capabilities to include higher level functionality fixed into the silicon. Having these common functions embedded into the silicon reduces the area required and gives those functions increased speed compared to building them from primitives. Examples of these include multipliers, generic Digital Signal Processor (DSP) blocks, embedded processors, high speed I/O logic, embedded memories and even IP cores such as Ethernet MACs etc. These cores exist alongside the programmable fabric, but they are built out of transistors instead of LUTs so they have greater level performance and power consumption while not consuming a significant amount of fabric resources, leaving more of the fabric free for the application-specific logic [11].

**Comparison with other architectures** FPGA-based products are basically very effective for low to medium volume production as they are easy to program and debug, and have less cost and faster time-to-market. All these major advantages of an FPGA come through their reconfigurability which makes them general purpose and field programmable. But, the very same reconfigurability is the major cause of its disadvantages; thus making it larger, slower and more power consuming than ASICs [12]. In contrast to FPGAs, ASICs do not suffer any area or timing overhead from configuration logic and generic interconnects, and therefore typically result in the smallest, fastest and most energy-efficient systems. However, the sophisticated fabrication processes for ASICs results in lengthy development cycles and very high upfront costs, which demands a first-time-right design methodology and very extensive design verification. Also the advantage of FPGA-based systems over traditional processorbased systems such as desktop computers, smartphones, most embedded systems, and also over GPUs, is the availability of freely programmable general-purpose logic blocks. These can be arranged into heavily specialized accelerators for very specific tasks, resulting in improved processing speed, higher throughput and energy savings. This advantage comes at the price of reduced agility and increased complexity during the development, where the designer needs to carefully consider the available hardware resources and the efficient mapping of his algorithm into the FPGA architecture. Furthermore, some algorithmic problems do not map well onto the rigid block structures found on FPGAs [12] [6].

Figure 2.9: A comparison between high-end GPUs and FPGAs [6].

# 2.3.2 Introduction to High Level Synthesis

High-level synthesis (HLS) is a methodology that provides optimized hardware synthesis from high-level programming language specifications such as C/C++ and System C. HLS tools allow designers to use a software program to specify the target system functionality, enabling them to exploit hardware advantages without building up hardware expertise.

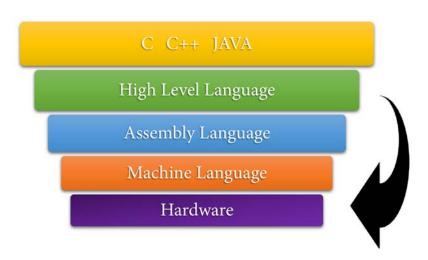

Traditionally, FPGAs are programmed using a Hardware Description Language (HDL) such as VHDL or Verilog. Most designs are described at Register Transfer Level (RTL), where the programmer specifies the algorithm using a multitude of parallel processes which operate on vectors of binary signals and simple integer data types derived from them. These processes describe combinational logic, basic arithmetic operations as well as registers, and are driven by the rising and falling edges of a clock signal. RTL descriptions are very close to the logic gates and wires which are actually available in the underlying FPGA or ASIC technology, and therefore the hardware that results from RTL synthesis can be closely controlled. However, the process of breaking down a given algorithm into logic blocks, processes and finite state machines on the register transfer level is very tedious and error-prone. Many design decisions have to be made before writing any code, and later changes are quite difficult and costly. This prevents iterative optimizations and demands a lot of intuition, experience and expert knowledge from designers. Increasing the level of abstraction with HLS High-Level Synthesis tries to lower this barrier by enabling designers to specify their algorithms in a high-level programming language such as C, C++ or SystemC. Many implementation details are abstracted away and handled by the HLS compiler, which converts the sequential software description into a concurrent hardware description, usually at RTL level [6] [13].

Figure 2.10: An illustration that shows the transition from High Level Language to Hardware.

**SDSoC Development Environment** The SDSoC development environment is an HLS tool that provides a familiar embedded C/C++/OpenCL application development experience including an easy to use Eclipse IDE and a comprehensive design environment for heterogeneous systems deployment [14]. SDSoC delivers system level profiling, automated software acceleration in programmable logic, automated system connectivity generation, and libraries to speed programming. It also enables end user and third party platform developers to rapidly define, integrate, and verify system level solutions and enable their end customers with a customized programming environment [15]. So in this way, designers can use loops, arrays, structs, floats, arithmetic operations, function calls, and even object-oriented classes. These are automatically converted into counters, memories, computation cores and handshake protocols as well as accompanying state machines and schedules with the most efficient way possible. The compilation can be influenced using scripted compiler directives or embedded compiler pragmas, which are instruction directives interpreted directly by the SDSoC compiler. Operations are by default scheduled to be executed concurrently and as early as possible. Using the compiler pragmas, the designer can further influence the inference of memories and interfaces, the parallelization of loops and tasks, the synthesis of computation pipelines, etc.

Although such tools exists that make the development of specific applications much easier and faster, there are still some difficulties on HLS synthesis tools. First, the results achieved especially for large applications with complex module and control-flow hierarchy are not as high as expected. Very often, the programming style of the source code has a severe impact on the quality of the synthesized implementation. Also many existing HLS compilers impose proprietary extensions or restrictions (e.g. exclusion of while loops) on the programming model of the specifications that they accept as input, and various heuristics on the HLS transformations that they utilize. At last, HLS tools have long learning curves meaning that only experienced users can develop efficient code on these platforms.

**Amazon AWS Cloud** Amazon provides a web service for Cloud Computing which is the ondemand delivery of compute power, database storage, applications, and other IT resources through a cloud services platform via the internet with pay-as-you-go pricing [16]. Specifically, Amazon Elastic Compute Cloud (Amazon EC2) is a web service that provides this web-scale cloud computing capability [17]. It provides with complete control of the computing resources and lets users run on Amazon's proven computing environment and build or test their applications on a secure environment.

Amazon provides along with these cloud service specific platforms, such as the EC2 F1 which is a compute instance with field programmable gate arrays (FPGAs) that users can program and test their custom hardware accelerations for their application [18]. F1 instances are easy to program and come with everything that has to do with developing, simulating, debugging and compiling the hardware acceleration code in High Level Synthesis.

## 2.3.3 Heterogeneous Systems