## ΕΘΝΙΚΟ ΜΕΤΣΟΒΙΟ ΠΟΛΥΤΕΧΝΕΙΟ

ΣΧΟΛΗ ΗΛΕΚΤΡΟΛΟΓΩΝ ΜΗΧΑΝΙΚΩΝ ΚΑΙ ΜΗΧΑΝΙΚΩΝ ΥΠΟΛΟΓΙΣΤΩΝ ΤΟΜΕΑΣ ΤΕΧΝΟΛΟΓΙΑΣ ΠΛΗΡΟΦΟΡΙΚΗΣ ΚΑΙ ΥΠΟΛΟΓΙΣΤΩΝ ΕΡΓΑΣΤΗΡΙΟ ΜΙΚΡΟΥΠΟΛΟΓΙΣΤΩΝ ΚΑΙ ΨΗΦΙΑΚΩΝ ΣΥΣΤΗΜΑΤΩΝ

# Design and Acceleration of Omnitrap Ion Storage Device Instrument Control

Διπλωματική Εργασία

του

# Σταύρου Κούβαρη

Επιβλέπων: Δημήτριος Σούντρης Καθηγητής Ε.Μ.Π

> Εργαστήριο Μικροϋπολογιστών και Ψηφιακών Συστημάτων Αθήνα, Ιούλιος 2020

## ΕΘΝΙΚΟ ΜΕΤΣΟΒΙΟ ΠΟΛΥΤΕΧΝΕΙΟ

ΣΧΟΛΗ ΗΛΕΚΤΡΟΛΟΓΩΝ ΜΗΧΑΝΙΚΩΝ ΚΑΙ ΜΗΧΑΝΙΚΩΝ ΥΠΟΛΟΓΙΣΤΩΝ ΤΟΜΕΑΣ ΤΕΧΝΟΛΟΓΙΑΣ ΠΛΗΡΟΦΟΡΙΚΗΣ ΚΑΙ ΥΠΟΛΟΓΙΣΤΩΝ ΕΡΓΑΣΤΗΡΙΟ ΜΙΚΡΟΥΠΟΛΟΓΙΣΤΩΝ ΚΑΙ ΨΗΦΙΑΚΩΝ ΣΥΣΤΗΜΑΤΩΝ

## **Design and Acceleration of Omnitrap Ion Storage Device**

## **Instrument Control**

Διπλωματική Εργασία

του

Σταύρου Κούβαρη

Επιβλέπων: Δημήτριος Σούντρης Καθηγητής Ε.Μ.Π

Εγκρίθηκε από την τριμελή εξεταστική επιτροπή την 10 Ιουλίου 2020

(Υπογραφή)

(Υπογραφή)

. . . . . . . . . . . . . . . .

(Υπογραφή)

. . . . . . . . . . . . . . . .

.....

Δημήτριος Σούντρης Καθηγητής Ε.Μ.Π. Παναγιώτης Τσανάκας Καθηγητής Ε.Μ.Π.

Παύλος Σωτηριάδης Καθηγητής Ε.Μ.Π.

Αθήνα, Ιούλιος 2020

(Υπογραφή)

.....

## Σταύρος Κούβαρης

Διπλωματούχος Ηλεκτρολόγος Μηχανικός και Μηχανικός Υπολογιστών Ε.Μ.Π.

© 2020 – All rights reserved

## ΕΘΝΙΚΟ ΜΕΤΣΟΒΙΟ ΠΟΛΥΤΕΧΝΕΙΟ

## ΣΧΟΛΗ ΗΛΕΚΤΡΟΛΟΓΩΝ ΜΗΧΑΝΙΚΩΝ ΚΑΙ ΜΗΧΑΝΙΚΩΝ ΥΠΟΛΟΓΙΣΤΩΝ ΤΟΜΕΑΣ ΤΕΧΝΟΛΟΓΙΑΣ ΠΛΗΡΟΦΟΡΙΚΗΣ ΚΑΙ ΥΠΟΛΟΓΙΣΤΩΝ ΕΡΓΑΣΤΗΡΙΟ ΜΙΚΡΟΥΠΟΛΟΓΙΣΤΩΝ ΚΑΙ ΨΗΦΙΑΚΩΝ ΣΥΣΤΗΜΑΤΩΝ

© 2020 – All rights reserved Σταύρος Κούβαρης, 2020.

Με επιφύλαξη παντός δικαιώματος.

Απαγορεύεται η αντιγραφή, αποθήκευση και διανομή της παρούσας εργασίας, εξ ολοκλήρου ή τμήματος αυτής, για εμπορικό σκοπό. Επιτρέπεται η ανατύπωση, η αποθήκευση και διανομή για σκοπό μη κερδοσκοπικό, εκπαιδευτικής ή ερευνητικής φύσης, υπό την προϋπόθεση να αναφέρεται η πηγή προέλευσης και να διατηρείται το παρόν μήνυμα. Ερωτήματα που αφορούν τη χρήση της εργασίας για κερδοσκοπικό σκοπό πρέπει να απευθύνονται προς τον συγγραφέα.

## Contents

| Πε          | ρίληψ                              | <i>ι</i> η         |                                                 |  |  |  |  |

|-------------|------------------------------------|--------------------|-------------------------------------------------|--|--|--|--|

| At          | stract                             |                    |                                                 |  |  |  |  |

| Ευχαριστίες |                                    |                    |                                                 |  |  |  |  |

| 1           | Εκτ                                | τεταμι             | ένη Περίληψη10                                  |  |  |  |  |

|             | 1.1                                | Εισο               | αγωγή                                           |  |  |  |  |

|             | 1.2                                | Ανά                | άπτυξη Συστήματος                               |  |  |  |  |

| 2           | Intr                               | oduct              | tion                                            |  |  |  |  |

|             | 2.1                                | Mas                | ss Spectrometry and experimental set-up         |  |  |  |  |

|             | 2.2 FPGA device                    |                    |                                                 |  |  |  |  |

|             | 2.3                                | Thesis Scope       |                                                 |  |  |  |  |

| 3           | Sys                                | tem I              | Development                                     |  |  |  |  |

|             | 3.1                                | Instrument control |                                                 |  |  |  |  |

|             | 3.2                                | Use                | er Interface for waveform generation            |  |  |  |  |

|             | 3.2                                | .1                 | Sweep                                           |  |  |  |  |

|             | 3.2                                | .2                 | FNF                                             |  |  |  |  |

|             | 3.3                                | Syst               | tem level improvements                          |  |  |  |  |

|             | 3.3                                | .1                 | FPGA Communication                              |  |  |  |  |

| 4           | FPO                                | GA ac              | cceleration of waveform generation              |  |  |  |  |

|             | 4.1 Sweep Direct Digital Synthesis |                    | eep Direct Digital Synthesis                    |  |  |  |  |

|             | 4.2                                | Filte              | ered Noise Field (FNF) Direct Digital Synthesis |  |  |  |  |

| 5           | Eva                                | aluatio            | on70                                            |  |  |  |  |

|             | 5.1                                | FPC                | GA Development Board                            |  |  |  |  |

|             | 5.2                                | PC ·               | - FPGA communication results                    |  |  |  |  |

|             | 5.3                                | Dig                | ital waveform generation using FPGA75           |  |  |  |  |

| 6           | Les                                | sons               | learned towards productization                  |  |  |  |  |

| 7           | Conclusion                         |                    |                                                 |  |  |  |  |

| 8           | Bib                                | oliogra            | aphy                                            |  |  |  |  |

## Περίληψη

Η παγίδα ιόντων Omnitrap, της εταιρείας Fasmatech, είναι μία διάταξη που επιτρέπει την παγίδευση και επεξεργασία ιόντων σε φασματομετρικές εφαρμογές. Στην παρούσα πειραματική διάταξη το Omnitrap χρησιμοποιείται ως πρόσθετο εξάρτημα του φασματομέτρου μάζας Q-Exactive, της εταιρείας Thermo Fisher Scientific. Η συγκεκριμένη διπλωματική εργασία αφορά την ανάπτυξη συστήματος FPGA που επιτρέπει τον έλεγχο της λειτουργίας του Omnitrap μέσω προσωπικού υπολογιστή. Ιδιαίτερη έμφαση δίνεται σε μία από τις λειτουργίες του Omnitrap, που είναι η απομόνωση ιόντων συγκεκριμένης μάζας, στο εσωτερικό της παγίδας, με τη χρήση κυματομορφών απομόνωσης Sweep και Filtered-Noise-Field. Για του σκοπούς του πειράματος, υλοποιείται κατάλληλος δίαυλος επικοινωνίας ανάμεσα σε PC και FPGA. Επιπλέον, μέθοδοι για τη γέννηση και παραμετροποίηση των κυματομορφών απομόνωσης υλοποιούνται τόσο στο PC όσο και στο FPGA. Στη συνέχεια συγκρίνονται μεταξύ τους και αξιολογούνται ως προς την καταλληλότητα τους για το συνολικό σύστημα. Τελικά, προκύπτουν συμπεράσματα για την τελική μορφή του συστήματος ελέγχου του οργάνου, με οριστικό στόχο την προϊοντοποίηση.

#### Λέξεις Κλειδία

FPGA, ψηφιακή σύνθεση κυμαρομορφών, κυματομορφές Sweep, κυμαρομορφές Filtered-Noise Field, προϊοντοποίηση, φασματομετρία μάζας, παγίδα ιόντων, omnitrap

#### Abstract

The Omnitrap linear segmented ion trap, developed in Fasmatech company, allows enhanced ion activation and storage in mass spectrometry applications. In the current experimental setup, Omnitrap is connected in series with Q-Exactive mass spectrometer of Thermo Fisher Scientific company. This diploma thesis concerns the development of an FPGA system that allows control of Omnitrap operation via a personal computer. Special emphasis is given on one of the Omnitrap functionalities, which is the isolation of ions of specific mass to charge ratio by means of Sweep and Filtered-Noise-Field isolation waveforms. For the experimental purposes, an effective communication port is developed between PC and FPGA. In addition to that, several methods for waveform generation, both by PC and FPGA, are implemented, compared and evaluated in regard to their efficiency for the overall system. Finally, conclusions are drawn concerning the final instrument design, towards productization.

#### **Keywords**

FPGA, direct digital synthesis, Sweep waveform, Filtered-Noise Field waveform, productization, mass spectrometry, ion trap, omnitrap

## Ευχαριστίες

Η παρούσα διπλωματική εργασία εκπονήθηκε στο Εργαστήριο Μικροϋπολογιστών και Ψηφιακών Συστημάτων (Microlab) στο ΕΜΠ, σε συνεργασία με την εταιρεία Fasmatech Science & Technology SA που στεγάζεται στο Τεχνολογικό Πάρκο Λεύκιππος στο Εθνικό Κέντρο Έρευνας Φυσικών Επιστημών «Δημόκριτος».

Αρχικά θα ήθελα να ευχαριστήσω τον επιβλέποντά μου, καθηγητή του ΕΜΠ Δημήτριο Σούντρη και τον CEO της εταιρείας Fasmatech, Δημήτριο Παπαναστασίου, που συνεργάστηκαν με επιτυχία τόσο μαζί μου όσο και μεταξύ τους για την ολοκλήρωση της συγκεκριμένης διπλωματικής εργασίας. Επιπλέον, θα ήθελα να ευχαριστήσω τον μεταδιδακτορικό ερευνητή του Microlab Γεώργιο Λεντάρη καθώς και τους μηχανικούς της Fasmatech, Ιωάννη Ορφανόπουλο και Αντρέα Μποζατζίδη, για τη βοήθεια που μου προσέφεραν τόσο σε επιστημονικό όσο και σε προσωπικό επίπεδο.

Τέλος, θα ήθελα να ευχαριστήσω τους γονείς μου, Πέτρο και Αργυρώ και την αδερφή μου Ματίνα για την διαρκή στήριξη και κατανόηση τους σε στιγμές αγχώδεις και πιεστικές.

## 1 Εκτεταμένη Περίληψη

## 1.1 Εισαγωγή

Η φασματομετρία μάζας είναι μια ευαίσθητη τεχνική για τον ποιοτικό και ποσοτικό προσδιορισμό χημικών ενώσεων και βρίσκει εφαρμογή σε μια μεγάλη γκάμα επιστημονικών πεδίων όπως βιολογία, χημεία, φυσική, φαρμακευτική, ακόμα και στην εξερεύνηση του διαστήματος. Σημαντικές εφαρμογές της φασματομετρίας μάζας στον σύγχρονο κόσμο, όπως αναδεικνύονται από την μεγαλύτερη εταιρεία ανάπτυξης και πώλησης φασματομετρικών οργάνων, τη Thermo Fisher Scientific, ανήκουν στα ερευνητικά πεδία της πρωτεϊνωματικής (proteomics), της μεταβολισμικής (metabolomics), της περιβαλλοντικής ανάλυσης, της εγκληματολογίας και των κλινικών αναλύσεων και ενδεικτικά κάποιες από αυτές είναι ο προσδιορισμός πρωτεϊνιών δομών, η αναγνώριση ακολουθιών πεπτιδίων, η διάγνωση καρκίνου, ο ποιοτικός έλεγχος του πόσιμου νερού, η ανάλυση υπολειμμάτων εκρηκτικού

Μία φασματομετρική διαδικασία περιλαμβάνει κατά κανόνα τον ιονισμό των μορίων της αναλυτέας ουσίας, το διαχωρισμό τους σύμφωνα με τον λόγο της μάζας προς το φορτίο τους, τον ποσοτικό προσδιορισμό της έντασης της κάθε μάζας στο δείγμα και τελικά χρήση των παραπάνω δεδομένων για τον καθορισμό της δομής και των συστατικών του αναλύτη.

Η παρούσα διπλωματική εργασία βασίζεται στην παγίδα ιόντων **Omnitrap** που αναπτύχθηκε και τελικά κατοχυρώθηκε ως πατέντα από την εταιρεία Fasmatech. Η παγίδα ιόντων είναι μια διάταξη τετραπόλου η οποία επιτρέπει την παγίδευση φορτισμένων σωματιδίων στο κέντρο συμμετρίας της, με την εφαρμογή δυναμικών ηλεκτρικών πεδίων στους τέσσερις πόλους της. Η παγίδα ιόντων μπορεί επίσης να χρησιμοποιηθεί και ως φίλτρο μαζών, δηλαδή ως διάταξη που επιτρέπει τη διατήρηση ιόντων συγκεκριμένου εύρους μαζών στο εσωτερικό της και επομένως την απομάκρυνση των υπολοίπων μαζών. Η συσκευή Omnitrap περιλαμβάνει οκτώ παγίδες ιόντων, Q1 έως Q8, με ελλειψοειδείς πόλους, σε σειριακή διάταξη μεταξύ τους, και παρέχει ένα ευρύ φάσμα δυνατοτήτων ως προς την επεξεργασία των ιόντων πριν την έναρξη της φασματομετρικής διαδικασίας.

Στην πειραματική διάταξη της συγκεκριμένης εργασίας, το Omnitrap αποτελεί μία επέκταση του φασματόμετρου μάζας Q Exactive της Thermo Fisher Scientific. Συγκεκριμένα, παρεμβάλλεται στον κύκλο λειτουργίας του και προσθέτει ένα ακόμα επίπεδο επεξεργασίας των ιόντων πριν φτάσουν στο Orbitrap, δηλαδή στο τμήμα του Q Exactive στο οποίο συντελείται η φασματική μέτρηση. Ένας επιτραπέζιος υπολογιστής χρησιμοποιείται για τον προσδιορισμό της πειραματικής διαδικασίας και για τα δύο όργανα καθώς και για τη λήψη των αποτελεσμάτων. Το είδος αυτό της φασματομετρικής διάταξης που περιλαμβάνει την σειριακή σύνδεση και λειτουργία δύο ή περισσοτέρων συσκευών ανάλυσης μάζας, με σκοπό την βελτίωση των δυνατοτήτων τους στην ανάλυση χημικών δειγμάτων, είναι γνωστό με τον αγγλικό όρο **Tandem Mass Spectrometry.**

Ως προς τις λειτουργίες του Omnitrap, κύρια έμφαση δίνεται στις παγίδες Q2 και Q5 στις οποίες παρέχεται η δυνατότητα εφαρμογής κυματομορφών απομόνωσης. Οι κυματομορφές αυτές είναι σήματα τάσης τα οποία αναπαράγονται στους πόλους της παγίδας και ανάλογα με το συχνοτικό τους

περιεχόμενο, απομακρύνουν ένα εύρος μαζών από το εσωτερικό της παγίδας. Πιο συγκεκριμένα, οι μάζες των οποίων η ιδιοσυχνότητα ταλάντωσης δεν περιλαμβάνεται στο συχνοτικό περιεχόμενο της κυματομορφής απομόνωσης, διατηρούνται στην παγίδα. Αντίθετα, οι υπόλοιπες μάζες ταλαντώνονται, οδηγούνται σε συντονισμό, και τελικά απομακρύνονται, προσκρούοντας στους πόλους της παγίδας. Η διατήρηση μόνο των ιόντων ενδιαφέροντος στην παγίδα συμβάλλει σε μεγάλο βαθμό στη βελτίωση της διακριτικής ικανότητας του φασματόμετρου μάζας.

## Συσκευή FPGA

Για τον έλεγχο των εξαρτημάτων του Omnitrap χρησιμοποιείται μία συσκευή FPGA. Η συσκευή FPGA (Field Programmable Gate Array ή συστοιχία επιτόπια προγραμματιζόμενων πυλών) αποτελείται εσωτερικά από ένα δίκτυο προγραμματιζόμενων ψηφιακών "κυττάρων" (cells) που μπορούν να υλοποιήσουν ψηφιακές συναρτήσεις. Πρακτικά, μια συσκευή FPGA επιτρέπει τη σχεδίαση και υλοποίηση ενός ψηφιακού κυκλώματος στον πραγματικό κόσμο, με τη χρήση λογισμικού. Επιπλέον διαθέτει πόρτες εισόδου – εξόδου για την αλληλεπίδραση του κυκλώματος με εξωτερικά εξαρτήματα. Μία συσκευή FPGA χρησιμοποιείται για τους εξής λόγους:

- Επιτρέπει την επιτάχυνση και βελτιστοποίηση βαρέων υπολογισμών, όπως η ψηφιακή σύνθεση κυματομορφών.

- Περιλαμβάνει πόρτες εισόδου εξόδου, επιτρέποντας άμεσο έλεγχο των περιφερειακών εξαρτημάτων του οργάνου και επομένως σχεδόν μηδενικό χρόνο αντίδρασης σε μεταβολές.

- Συμβάλλει στην απομόνωση του συνολικού συστήματος από εξωτερικές επιρροές και επιτρέπει ντετερμινιστική συμπεριφορά υψηλής χρονικής ακρίβειας, καθώς οι περισσότερες διαδικασίες που συντελούνται στο Omnitrap απαιτούν αξιόπιστο και ακριβή έλεγχο, σε επίπεδο παλμών ρολογιού.

## Στόχοι διπλωματικής εργασίας

Οι στόχοι της παρούσας διπλωματικής εργασίας είναι:

- Η ανάπτυξη ενός πλήρους συστήματος που επιτρέπει τον χαμηλού επιπέδου έλεγχο της συσκευής Omnitrap και παρέχει ευελιξία στον προσδιορισμό της πειραματικής διαδικασίας καθώς το όργανο βρίσκεται ακόμα σε στάδιο ανάπτυξης και νέες τεχνικές για χρήση της παγίδας εξετάζονται συνεχώς.

- Η ανάπτυξη ενός αποτελεσματικού και αξιόπιστου διαύλου επικοινωνίας μεταξύ PC και FPGA, καθώς η συσκευή FPGA αποτελεί το πυρήνα επεξεργασίας των λειτουργιών του Omnitrap.

- Η εξερεύνηση των δυνατοτήτων του FPGA σχετικά με την ψηφιακή σύνθεση κυματομορφών.

- Η παραχώρηση προτάσεων για την τελική μορφή του οργάνου.

Κατά την εκπόνηση της διπλωματικής εργασίας, έγιναν εκτεταμένες προσπάθειες για την επιτάχυνση της μεταφοράς δεδομένων από το PC στο FPGA. Επιπλέον, πραγματοποιήθηκε σύγκριση μεταξύ της σύνθεσης κυματομορφών από το PC έναντι της άμεσης σύνθεσης και αναπαραγωγής τους από το FPGA. Πλεονεκτήματα και μειονεκτήματα και των δύο τεχνικών αναφέρονται και συμπεράσματα προκύπτουν τα οποία βρίσκουν εφαρμογή σε όλα τα σύγχρονα συστήματα που περιλαμβάνουν συσκευές FPGA, και ειδικότερα που αφορούν εργαστηριακό εξοπλισμό και όργανα πειραματικών μετρήσεων.

## 1.2 Ανάπτυξη Συστήματος

## Διεπαφή χρήστη για σύνθεση κυματομορφών

Για τον πειραματισμό και την εφαρμογή κυματομορφών απομόνωσης στην παγίδα Omnitrap, αναπτύχθηκε ο απαραίτητος αλγόριθμος για τη δημιουργία των κυματομορφών καθώς επίσης και το αντίστοιχο περιβάλλον στο PC μέσω του οποίου ο χρήστης μπορεί να παραμετροποιήσει το εκάστοτε σήμα. Οι κυματομορφές αυτές συντίθενται στο PC και στη συνέχεια αποστέλλονται στο FPGA για αναπαραγωγή στους πόλους του αντίστοιχου τετραπόλου. Υπάρχουν δύο είδη σημάτων απομόνωσης, η κυματομορφή Sweep και η κυματομορφή Filtered Noise Field.

<u>Κυματομορφή Sweep:</u> Η κυματομορφή Sweep είναι μία αρμονική συνάρτηση με γραμμικά αυξανόμενη συχνότητα. Το συχνοτικό της περιεχόμενο περιλαμβάνει όλες τις συχνότητες από μία αρχική έως μία τελική τιμή. Ενδεικτικά οι εξισώσεις υπολογισμού της κυματομορφής φαίνονται παρακάτω:

Sweep(n) = sin [Phase(n)],

όπου η φάση <u>Phase(n</u>) υπολογίζεται ως εξής: **Phase(n) = Phase(n - 1) + 2pi \* Ts \* frequency(n),** με Ts: η περίοδος δειγματοληψίας.

Η συχνότητα <u>Frequency(n)</u> αυξάνεται γραμμικά:  $frequency(n) = frequency(n-1) + frequency_step.$

Ο χρήστης, μέσω του λογισμικού δύναται να παραμετροποιήσει την κυματομορφή Sweep ως προς το πλάτος, την αρχική και την τελική συχνότητα.

Για το σκοπό της διατήρησης συγκεκριμένων μαζών στην παγίδα, δίνεται η δυνατότητα στον χρήστη εξαίρεσης από το συχνοτικό περιεχόμενο της κυματομορφής Sweep, ενός εύρους συχνοτήτων, ανάλογα με την εφαρμογή. Όπως έχει ήδη αναφερθεί, οι μάζες των οποίων η συχνότητα ιδιοταλάντωσης δεν περιλαμβάνεται στο συχνοτικό περιεχόμενο του σήματος, παραμένουν στην παγίδα μετά την αναπαραγωγή του Sweep, ενώ οι υπόλοιπες διεγείρονται και απομακρύνονται.

Επιπλέον δυνατότητες ως προς την παραμετροποίηση του Sweep εμφανίζονται στη διεπαφή χρήστη που αναπτύχθηκε, όπως η εξομάλυνση του πλάτους εισόδου και εξόδου καθώς και ο καθορισμός της συνολικής διάρκειας του Sweep.

<u>Κυματομορφή FNF:</u> Η κυματομορφή Filtered Noise Field (FNF) συντίθεται από το άθροισμα ημιτονοειδών συναρτήσεων διαφορετικής συχνότητας. Ομοίως και εδώ, η κυματομορφή χαρακτηρίζεται από μία αρχική και μία τελική συχνότητα, στις οποίες προστίθεται και η παράμετρος του βήματος

συχνότητας. Το βήμα συχνότητας καθορίζει τη διακριτική ικανότητα του συχνοτικού περιεχομένου του FNF σήματος που προκύπτει.

Όπως και στην περίπτωση της κυματομορφής Sweep, έτσι και εδώ ο χρήστης έχει τη δυνατότητα να προσθέσει συχνοτικά κενά στην FNF κυματομορφή. Επιπλέον, υπάρχουν δυνατότητες τροποποίησης του πλάτους καθώς και εφαρμογής τεχνικών διαμόρφωσης φάσης για καλύτερη κατανομή της ισχύος κατά μήκος του σήματος.

Βασική διαφορά του σήματος Sweep με το σήμα FNF είναι το γεγονός ότι στο πρώτο οι συχνότητες αναπαράγονται σειριακά η μία μετά την άλλη, ενώ στο δεύτερο οι συχνότητες αναπαράγονται ταυτόχρονα καθ'όλη τη διάρκεια της κυματομορφής. Πειραματικά κάθε μία χρησιμοποιείται για διαφορετικές εφαρμογές και παρουσιάζει τόσο πλεονεκτήματα όσο και μειονεκτήματα.

## Έλεγχος Συστήματος

Για τον έλεγχο της πειραματικής διαδικασίας του Omnitrap, ο χρήστης καλείται μέσω λογισμικού να συνθέσει μία ακολουθία εντολών. Κάθε εντολή σχετίζεται μία ξεχωριστή ενέργεια του οργάνου ενώ των σύνολο των εντολών προσφέρει δυνατότητες τροποποιήσεων του πειράματος σε χαμηλό επίπεδο. Ενδεικτικά ορισμένες από τις σημαντικότερες εντολές αφορούν δράσεις όπως:

- Διακοπή της πειραματικής διαδικασίας μέχρι τα ιόντα να περάσουν από το όργανο Q Exactive στην παγίδα ιόντων Omnitrap. Το γεγονός αυτό σηματοδοτείται από το θετικό παλμό ενός σήματος trigger που προέρχεται από το Q Exactive και παραλαμβάνεται από το FPGA που ελέγχει το Omnitrap.

- Μετακίνηση του δείγματος ιόντων από μία παγίδα Qx σε μία άλλη παγίδα Qy (υπάρχουν οκτώ παγίδες ιόντων διαθέσιμες, Q1 έως Q8)

- Αναπαραγωγή κυματομορφής απομόνωσης (στα τετράπολα Q2 και Q5). Οι κυματομορφές απομόνωσης διακρίνονται σε δύο είδη, τα σήματα Sweep και τα σήματα Filtered Noise Field (FNF) το κάθε ένα με τα δικά του χαρακτηριστικά.

Για την εκτέλεση του πειράματος, τα δεδομένα της ακολουθίας εντολών κωδικοποιούνται κατάλληλα από το PC και στέλνονται στο FPGA, όπου και αποθηκεύονται σε εσωτερική μνήμη block RAM. Στη συνέχεια, μία custom IP είναι υπεύθυνη για την εκτέλεση των εντολών, όταν ο χρήστης σηματοδοτήσει, από το λογισμικό στο PC, την έναρξη της διαδικασίας.

## Βελτιώσεις Συστήματος

## Επικοινωνία με το FPGA

Για τη συγκεκριμένη διάταξη, τα δεδομένα που χρειάζεται να μεταφέρονται από το PC στο FPGA είναι τα εξής:

- Η κωδικοποιημένη ακολουθία εντολών που καθορίζει την πορεία του πειράματος

- Τα δείγματα των ψηφιακών κυματομορφών απομόνωσης Sweep και FNF

Τα δεδομένα που χρειάζεται να μεταφέρονται από το FPGA στο PC είναι"

• Μετρήσεις τάσεων και θερμοκρασίας που πραγματοποιούνται σε διάφορα σημεία του οργάνου

Για την δημιουργία διαύλου επικοινωνίας μεταξύ PC και FPGA υλοποιήθηκαν και δοκιμάστηκαν τέσσερις διαφορετικές μέθοδοι οι οποίες περιγράφονται περιληπτικά παρακάτω.

<u>USB 2.0 σε πρωτόκολλο UART</u>: Το πρωτόκολλο UART (Universal Asynchronous Receiver/Transmitter) είναι ένα σειριακό ασύγχρονο πρωτόκολλο που επιτρέπει τη μεταφορά δεδομένων μεταξύ δύο ή περισσότερων συσκευών οι οποίες είναι σύγχρονες σε διαφορετικά ρολόγια. Απαιτεί δύο άκρα εισόδου εξόδου για την εγκατάσταση του μεταξύ δύο συσκευών. Κάθε συσκευή οφείλει να διαθέτει ένα άκρο λήψης και ένα άκρο αποστολής δεδομένων.

Για την υλοποίηση της συγκεκριμένης επικοινωνιακής μεθόδου χρησιμοποιήθηκε το ολοκληρωμένο FT2232H της FTDI σε λειτουργία γέφυρας USB 2.0 σε UART. Η εταιρεία παρέχει το απαραίτητο API για την ανάπτυξη desktop εφαρμογών που χρησιμοποιούν το συγκεκριμένο δίαυλο επικοινωνίας. Τα δεδομένα μεταφράζονται από το USB πρωτόκολλο του PC στο απλοποιημένο πρωτόκολλο UART, ώστε να ληφθούν από το FPGA.

Για τη λήψη και διαχείριση των δεδομένων από το FPGA χρησιμοποιήθηκαν κατά κύριο λόγο οι παρακάτω IPs:

- Microblaze soft-core : ο επεξεργαστής που παραχωρείται από την Xilinx για χρήση εσωτερικά του FPGA. Υλοποιείται με τη χρήση πόρων του FPGA.

- AXI UARTlite: ο ελεγκτής πρωτοκόλλου UART που παρέχεται από τη Xilinx.

- Memory Interface Generator: ο ελεγκτής εξωτερικής μνήμης τυχαίας προσπέλασης (DDR) που παρέχεται από τη Xilinx.

Οι IPs εσωτερικά του FPGA επικοινωνούν μεταξύ τους μέσω του AXI bus. Τα δεδομένα από τον δίαυλο UART παραλαμβάνονται από τον Microblaze, ο οποίος είναι υπεύθυνος για την προώθηση τους στον εκάστοτε προορισμό. Επιπλέον, επιστρέφει στο PC ένα byte επιβεβαίωσης το οποίο σηματοδοτεί την επιτυχή ολοκλήρωση της μεταφοράς των δεδομένων. Σε περίπτωση που τα δεδομένα αντιστοιχούν σε σημεία κυματομορφών, ο Microblaze τα προωθεί σε εξωτερική μνήμη DDR3.

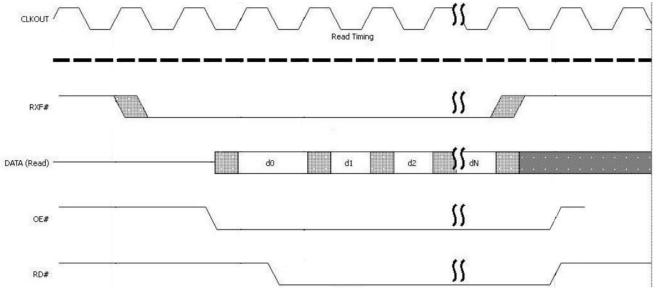

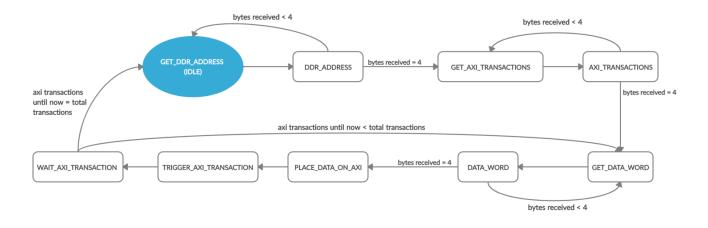

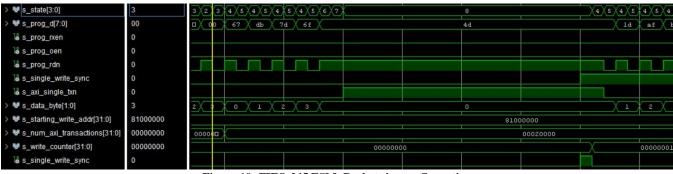

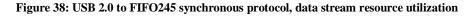

<u>USB 2.0 σε σύγχρονο πρωτόκολλο FIFO 245:</u> Για τη συγκεκριμένη υλοποίηση χρησιμοποιήθηκε ξανά το ολοκληρωμένο FT2232H της FTDI, αυτή τη φορά σε λειτουργία γέφυρας USB 2.0 σε FIFO245. Το πρωτόκολλο FIFO 245 είναι ένα σύγχρονο παράλληλο πρωτόκολλο με μέγεθος λέξης 8 bits. Για τη λήψη των δεδομένων από το FPGA απαιτείται δημιουργία IP καθώς δεν παρέχεται από τη Xilinx. Η επικοινωνία του FPGA με το ολοκληρωμένο πρέπει να είναι σύγχρονη με ρολόι συχνότητας 60 MHz το οποίο παρέχεται από το chip. Σε αυτή την υλοποίηση δεν χρησιμοποιείται ο Microblaze αλλά τα δεδομένα κατευθύνονται στον προορισμό τους μέσω custom IP που δημιουργήθηκε. Με αυτό τον τρόπο αποφεύγονται καθυστερήσεις που οφείλονται στην αρχιτεκτονική του soft-core επεξεργαστή, και οι ανταλλαγές δεδομένων βελτιστοποιούνται.

<u>USB 2.0 με streaming δεδομένων:</u> Η υλοποίηση αυτή επιχειρεί να εξαλείψει τις καθυστερήσεις που προκύπτουν από τη μεταφορά μεγάλων πακέτων δεδομένων από το PC στο FPGA. Για την παρούσα εφαρμογή τα δεδομένα κυματομορφών αποτελούν τέτοιου είδους πακέτα. Χρησιμοποιεί ξανά το ολοκληρωμένο FT2232H σε λειτουργία γέφυρας USB 2.0 σε FIFO 245. Τα δεδομένα κυματομορφών πλέον δεν αποθηκεύονται σε εξωτερική μνήμη. Αντιθέτως, χρησιμοποιούνται ταυτόχρονα με την αποστολή τους από το PC, ενώ η αναπαραγωγή της κυματομορφής στους πόλους της παγίδας ξεκινά μόλις το πρώτο σημείο έχει ληφθεί από το FPGA. Μία FIFO (First In / First Out) εσωτερική μνήμη χρησιμοποιείται για το συγχρονισμό του ρυθμού δειγματοληψίας και της ταχύτητας μεταφοράς των δεδομένων. Η υλοποίηση αυτή είναι εφικτή καθώς η συχνότητα δειγματοληψίας είναι μικρότερη από τη συχνότητα του ρολογιού των 60MHz στο οποίο είναι σύγχρονη η μεταφορά δεδομένων.

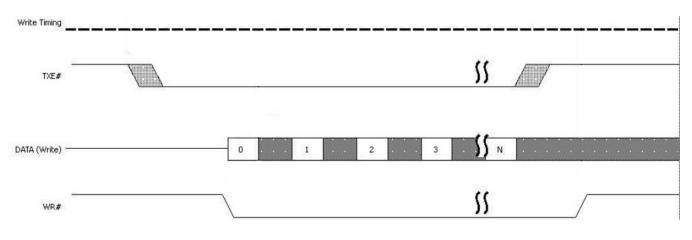

<u>USB 3.0 σε σύγχρονο πρωτόκολλο FIFO 245:</u> Τέλος, στη συγκεκριμένη υλοποίηση γίνεται αναβάθμιση του πρωτοκόλλου από USB 2.0 σε USB 3.0 με σκοπό υψηλότερες ταχύτητες μεταφοράς δεδομένων. Χρησιμοποιείται το ολοκληρωμένο FT601Q της FTDI σε λειτουργία γέφυρας USB 3.0 σε FIFO 245. Η σχετική ψηφιακή λογική για τη λήψη των δεδομένων από το FPGA αναπτύσσεται ενώ τα δεδομένα κυματομορφών αποθηκεύονται σε εξωτερική DDR μνήμη. Η μεταφορά των δεδομένων στην DDR μνήμη πραγματοποιείται με τη χρήση AXI Stream πρωτοκόλλου με στόχο την επίτευξη υψηλότερων ταχυτήτων εγγραφής.

## Επιτάχυνση της παραγωγής κυματομορφών με τη χρήση FPGA

Το γεγονός ότι οι βασικές λειτουργίες του οργάνου Omnitrap ελέγχονται από το FPGA, καθιστά αξιόλογη την ιδέα της υλοποίησης των κυματομορφών απομόνωσης από το ίδιο το FPGA. Παράλληλα, οι διάφορες παραμετροποιήσεις των Sweep και FNF κυματομορφών που παρέχονται στο λογισμικό πρέπει να παραμείνουν διαθέσιμες και στην περίπτωση παραγωγής τους από το FPGA.

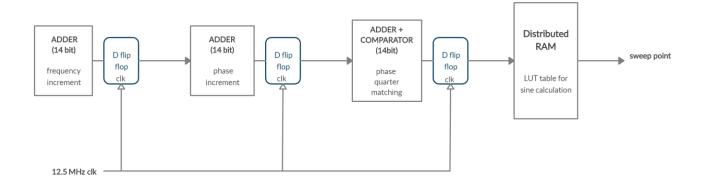

<u>Ψηφιακή σύνθεση κυματομορφής Sweep στο FPGA:</u> Για την παραγωγή της κυματομορφής Sweep από το FPGA χρησιμοποιήθηκε ο ίδιος αλγόριθμος υπολογισμού που υλοποιεί το Sweep στο PC και αναφέρεται σε προηγούμενη ενότητα. Όπως φαίνεται, για τον υπολογισμό του σήματος Sweep απαιτείται ο υπολογισμός της συνάρτησης του ημιτόνου. Για το σκοπό αυτό χρησιμοποιήθηκε η τεχνική του Look-Up Table κατά την οποία το τεταρτημόριο μίας ημιτονικής περιόδου δειγματοληπτείται επαρκώς και τα σημεία αποθηκεύονται σε εσωτερική μνήμη (distributed RAM) του FPGA. Ο αριθμός των δειγματοληπτημένων σημείων καθορίζει το εύρος των ημιτονικών συχνοτήτων που μπορούν να αναπαραχθούν, σύμφωνα με τον θεώρημα δειγματοληψίας Nyquist.

Η πράξη του πολλαπλασιασμού που εμφανίζεται στις εξισώσεις του Sweep εξαλείφεται με κατάλληλη κανονικοποίηση των δεδομένων αρχικοποίησης. Έτσι ο αλγόριθμος υλοποιείται εσωτερικά του FPGA με τη χρήση μερικών αθροιστών, του ημιτονικού Look-Up Table και ενός συγκριτή ο οποίος είναι υπεύθυνος για τον καθορισμό του προσήμου του ημιτόνου κάθε φορά. Το κύκλωμα που πραγματοποιεί τον υπολογισμό Sweep αποτελείται από στάδια, σε pipeline μορφή, για επιτάχυνση των πράξεων. Με την προσθήκη επιπλέον σταδίων pipeline, πριν ή μετά τον βασικό αλγόριθμο, μπορούν να υλοποιηθούν πιο εξειδικευμένες παραμετροποιήσεις του Sweep, όπως τροποποίηση του πλάτους και εφαρμογή συχνοτικών κενών.

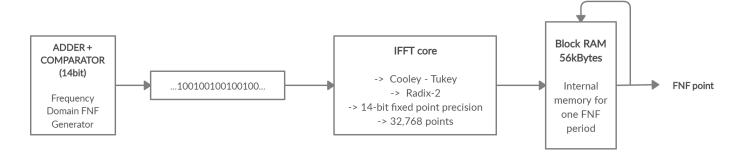

<u>Ψηφιακή σύνθεση κυματομορφής FNF στο FPGA</u>: Μία κυματομορφή FNF μπορεί να υπολογιστεί από το άθροισμα ημιτόνων διαφορετικής συχνότητας, οι οποίες καθορίζονται από το επιθυμητό εύρος συχνοτήτων του FNF σήματος, καθώς και από την επιθυμητή συχνοτική ανάλυση. Για τον υπολογισμό της κυματομορφής FNF χρησιμοποιήθηκε αντίστροφος μετασχηματισμός Fourier. Το σήμα κατασκευάζεται αρχικά στο πεδίο των συχνοτήτων, ορίζοντας ως μηδέν το πλάτος και τη φάση των συχνοτικών τόνων που δε θέλουμε να συμπεριλαμβάνονται στο σήμα. Επίσης για εξοικονόμηση χρόνου και πόρων του FPGA, ο αντίστροφος μετασχηματισμός πραγματοποιείται για μία μόνο περίοδο του FNF σήματος ενώ το τελικό σήμα δημιουργείται από αλληλουχία FNF περιόδων, μέχρι να επιτευχτεί η επιθυμητή διάρκεια.

Για συγκεκριμένη υλοποίηση χρησιμοποιήθηκε η IP Fast Fourier Transform v9.1 που παρέχει η Xilinx. Η συγκεκριμένη IP εκτελεί τον αλγόριθμο Cooley-Turkey για τον υπολογισμό του μετασχηματισμού. Το μέγεθος του IFFT (Inverse Fourier Transform) καθορίζεται από τη μέγιστη περίοδο ενός FNF σήματος η οποία δεν ξεπερνά τα 5 milliseconds. Αφού ο ρυθμός δειγματοληψίας της παρούσας διάταξης ισούται με 12.5 MHz, το μέγιστο απαιτούμενο μέγεθος του μετασχηματισμού ανέρχεται στα 2<sup>16</sup> σημεία.

Προσθέτοντας επιπλέον στάδια στην παρούσα υλοποίηση, σε μορφή pipeline, μπορούν να υλοποιηθούν περεταίρω παραμετροποιήσεις του σήματος, σε αντιστοιχία με αυτές του σήματος Sweep.

#### 2 Introduction

Mass spectrometry is a powerful analytical technique that finds application in a huge variety of different fields like biology, chemistry and physics, but also in clinical medicine and even space exploration. It constitutes one of the most powerful modern physical and chemical methods for identifying compounds and for studying their structure and reactivity. Namely, some of the most common applications of mass spectrometry in the modern world, as pointed out by Thermo Fisher Scientific company, belong to the fields of proteomics (characterization of proteins, sequencing of peptides), metabolomics (cancer screening and diagnosis, biofuels generation and use), environmental analysis (drinking water testing, carbon dioxide and pollution monitoring), forensic analysis (analysis of trace evidence, identification of explosive residues) and clinical purposes (clinical drug development, clinical tests, disease screening) (1).

#### 2.1 Mass Spectrometry and experimental set-up

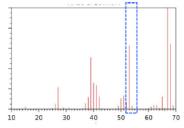

A mass spectrometry experimental procedure includes ionization of the analyte's molecules, separation according to their mass-to-charge ratio, measurement of the detected ions' intensity in the sample and finally use of these data to decide the structure and contents of the analyte of interest. The mass-to-charge ratio of a cation (ion of negative charge) is defined as the mass of the cation divided by its charge. The results of a mass spectrometry experimental process are typically presented in a mass spectrum, a plot of intensity as a function of mass-to-charge ratio. Intensity in general refers to the quantity of different ions inside a chemical substance and is usually expressed in arbitrary values as its nature defers according to the mass spectrometry method that is followed.

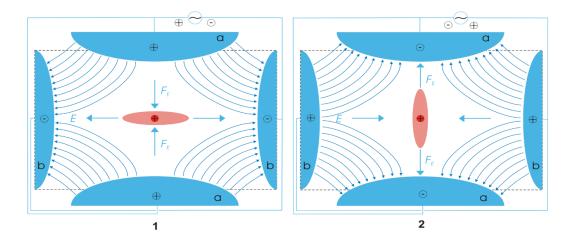

Fasmatech's recent accomplishment is the invention and development of Omnitrap (Figure 2). Omnitrap is a segmented linear quadrupole ion trap which is capable of enhanced ion activation (ionization) and storage (2). A quadrupole ion trap (Figure 1), in general, is a type of ion trap that uses dynamic electric fields to trap charged particles. The linear ion trap uses a set of quadrupole rods to confine ions radially and a static electrical potential on-end electrodes to confine the ions axially. The linear form of the trap can be used as a selective mass filter, or as an actual trap by creating a potential well for the ions along the axis of the electrodes.

Figure 1: Scheme of a Quadrupole ion trap of classical setup with a particle of positive charge (dark red), surrounded by a cloud of similarly charged particles (light red). The electric field E (blue) is generated by a quadrupole of endcaps (a, positive) and a quadrupole of endcaps (a, positive) and a ring electrode (b). Picture 1 and 2 show two states during an AC cycle (3).

Linear ion traps are extremely powerful analytical devices, either deployed as stand-alone mass spectrometers or integrated in hybrid systems. Linear ion traps are also ideal platforms for developing and testing new techniques for manipulating gas phase ions in radio frequency (RF) trapping fields. Omnitrap provides multiple methods for sequential manipulation of ions in multiple trapping regions afforded by fast switching DC electrical potentials for high level control of ion potential energy and transfer between segments.

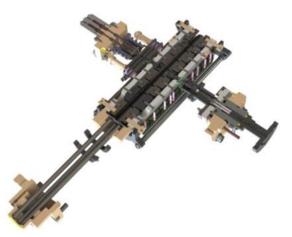

Omnitrap is designed with eight segments, Q1 to Q8, and hyperbolic surface electrodes supported on a stainless-steel structure cell. Differential pumping is provided through gaps between the bottom set of electrode-poles. A two-layer printed circuit board configuration is connected at the top of the Omnitrap and DC, RF and other AC signals are distributed to the electrode poles using spring contacts. A second pulse valve is used to admit fast gas pulses and an additional needle valve is employed to control background pressure.

Figure 2: Omnitrap (4)

Different regions of Omnitrap are configured to support a diverse set of substantially different functions and the length of each segment is optimized accordingly. Each of the segments is connected to an independent switching module capable of switching the DC potential between 8 different levels during the course of an experiment.

Slow heating CID (collisionally activated dissociation, a technique to induce fragmentation of ions in the gas phase) and ion isolation using the Filtered-Noise-Field (FNF) and Sweep method are performed on one of the segments, Q2. Another interesting segment is Q5, which is designed with two apertures on opposite electrode-poles to allow injection of charged particle beams and photons.

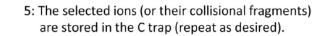

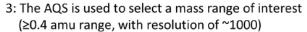

For the application that is developed in the specific diploma thesis, Omnitrap constitutes and external instrument connected to Orbitrap Q Exactive mass analyzer by Thermo Fisher Scientific. Its components and a brief description of their functionality is given, for the sake of completeness, in Figure 3. The Q Exactive mass analyzer includes six main subcomponents: an ion source (1), an ion guide (2), a mass filter (3), an ion trap (5), an HCD cell (4) and the Orbitrap analyzer (6).

4 (optional): Selected masses may be passed to the HCD cell and subjected to fragmentation by energetic collisions

Figure 3: Schematic illustration of the major components of Q Exactive Orbitrap (5)

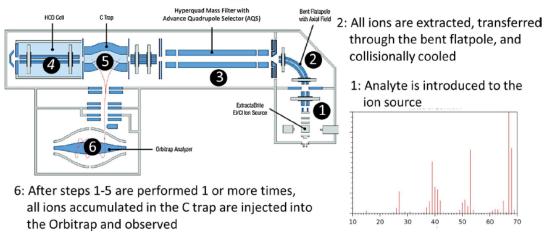

The Omnitrap platform is connected to the Q Exactive instrument in series with the HCD cell. Ions are processed in the Omnitrap platform and products are redirected back to the Q Exactive instrument for measuring mass-to-charge using the Orbitrap mass analyzer, as shown in Figure 4. Both instruments are controlled by the use of a PC which is responsible for both sending configuration data to them and receiving the corresponding experimental measurements, via USB interface. The technique of instrumental analysis where two or more mass analyzers are coupled together using an additional reaction step to increase their abilities to analyse chemical samples, is knows as **Tandem Mass Spectrometry**.

Figure 4: Omnitrap in series with Q Exactive (4)

Strong emphasis is given on the ion isolation methods by the use of Sweep and FNF signals waveforms. Ion isolation is the procedure, which aims to exclude every ion of an ionized analyte inside the ion trap, with the exception of a selected ion type with specified mass-to-charge ratio. Such a task is accomplished by applying voltage waveforms of specific frequency content in the poles of the trap. The frequency content of these waveforms defines the ions that remain in the ion trap and those that are excluded. To be more specific, ions whose resonance frequency is included in the isolation waveform's frequency spectrum, resonate and are consequently excluded from the ion trap. On the other hand, ions that do not resonate remain inside the trap in a stable state. Under this perspective, the main flow of experimental operation is predefined: Omnitrap is responsible for receiving an analyte, applying an ion excitation technique (Sweep or FNF) and afterwards passing the resulting ion substance to Q Exactive for mass spectrometry analysis and evaluation of results.

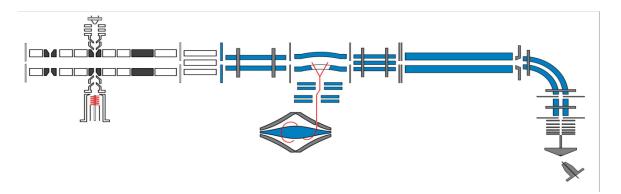

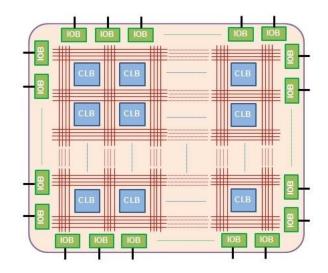

#### 2.2 FPGA device

FPGAs (Field Programmable Gate Arrays) are devices that allow the design and real-world generation of digital circuits, by software. In contrast with microcontrollers, which include an already implemented processing architecture, FPGAs' circuitry has to be designed by scratch, in order to implement a desirable functionality. This fact makes FPGAs extremely customizable in comparison to microcontrollers. In order to program an FPGA and generate a digital logic circuit, hardware description language has to be used, which as implied by its name, is a programming language that is used to describe a circuit by code. In the current thesis, the hardware description language that is used is VHDL and the integrated design environment that is used is the version 18.1 of Vivado Design Suite.

Figure 5: FPGA Configurable Logic Blocks (CLBs) network

An FPGA internally consists of a network of configurable logic blocks (CLBs, Figure 5), which can be programmed to implement specific digital logic functions while memory cells are also available for storage purposes. In some FPGAs, DSP slices are also included. Their name stands for Digital Signal Processing cells which are capable of implementing efficiently signal processing functions. Finally, each FPGA incorporates a prefixed number of Input-Output ports, so that it can interact with external circuitry.

For the purposes of the current project, an FPGA device is chosen on top of a microcontroller (6), because:

- It allows acceleration and optimization of heavy task computations, like digital waveform synthesis.

- It includes Input-Output ports that allow direct contact with hardware components and thus, hardly instant reaction capabilities.

- It contributes to overall system isolation from external interferences and allows deterministic behavior of high timing precision, as most of the Omnitrap functionality demands accurate, reliable and high speed timing control.

### 2.3 Thesis Scope

Omnitrap control by FPGA had been already implemented to some extent before the realization of this diploma thesis. Omnitrap is controlled by PC software and its actions are configurable by means of a series of instrument commands, which are summarily described in the first chapters. However, deficiencies have been present concerning PC – FPGA communication and overall FPGA processing speed. Overcoming this deficit and upgrading the overall instrument design to a more robust and

efficient one has been a major need. Under this perspective, the main goals of this diploma thesis have been:

- The development of a complete system that achieves low-level Omnitrap instrument control and offers high versatility in the experimental process while new techniques of using the linear trap are still being examined.

- Developing an effective communication method among PC and FPGA, as the FPGA device constitutes the center module that controls the main hardware components of Omnitrap.

- FPGA exploration concerning methods of digital signal generation inside the FPGA.

- Ultimately, suggesting a final product design.

Throughout the realization of this thesis, extensive attempts took place concerning FPGA data transfer acceleration. In addition, a comparison took place between software generation of custom digital waveforms by PC against their direct digital synthesis by the FPGA device. Advantages and disadvantages of both techniques are examined and overall conclusions are drawn, which find application in every modern FPGA system, especially concerning applications in scientific instrumentation and equipment

## **3** System Development

| Delay                 | ;                       | # In | struction | iratio<br>[ms] | n            | Exp.Time | [ms]  |

|-----------------------|-------------------------|------|-----------|----------------|--------------|----------|-------|

| Gas Pulse 1 [µs]      |                         |      |           |                |              |          |       |

| Gas Pulse 2 [µs]      |                         |      |           |                |              |          |       |

| Gas Pulse 3 [µs]      |                         |      |           |                |              |          |       |

| solation waveform q2  |                         |      |           |                |              |          |       |

| solation waveform q5  |                         |      |           |                |              |          |       |

| Dipolar Excitation q2 |                         |      |           |                |              |          |       |

| Dipolar Excitation q5 |                         |      |           |                |              |          |       |

| Trigger In            |                         |      |           |                |              |          |       |

| Digital RF [KHz]      |                         |      |           |                |              |          |       |

| Modulate electrons    |                         |      |           |                |              |          |       |

| Gate electrons        |                         |      |           |                |              |          |       |

| Duty cycle [%]        |                         |      |           |                |              |          |       |

| RF Amplitude [V]      |                         |      |           |                |              |          |       |

| States                |                         |      |           |                |              |          |       |

| Normal Q2             |                         |      |           |                |              |          |       |

| Inject to Omni        |                         |      |           |                |              |          |       |

| Confine lons          |                         |      |           |                |              |          |       |

| Transfer to Q5        |                         |      |           |                |              |          |       |

| Eject to HCD cell     | <                       |      |           | _              |              |          | >     |

| Transfer to Store Q8  | <u>Repeat</u><br>Repeat |      | 1 ste     |                | step<br>step | 2        | times |

| Lift to react Q5      |                         |      |           |                |              |          |       |

| Resolving DC Q2       |                         |      |           |                |              |          |       |

| Resolving DC Q5       |                         |      |           |                |              |          |       |

The whole instrument functionality is controlled via PC application. Through software that is

Figure 6: Omnitrap sequence of commands

already developed, Omnitrap user is given a wide variety of possibilities, concerning experiment configuration, depending on the application needs. At the stage of instrument development, before commercial production and sale, low-level instrument control by PC is necessary so that validation testing is efficiently performed by specialized scientists and instrument functionalities are verified. In addition, the invention and trial of new mass spectrometry techniques, using the equipment available, is encouraged.

The main idea for creating a ustomizable while comprehensive and fficient user interface for Omnitrap control as been based on the fact that the whole xperimental process can be expressed by a equence of commands. These commands re linked to pre-specified instrument ctions and, therefore, a sequence of these ommands represents a series of actions that he instrument is ordered to deliver. A lifferent sequence of commands can be enerated each time, depending on the pplication purposes. By splitting the xperiment in smaller sub-parts more recise instrument control is accomplished, nalfunctions are more easily detected and nodifications in the experimental flow are impler to implement.

As already mentioned, the processing core of Omnitrap instrument is an FPGA. The FPGA is intended to receive

the sequence of commands from PC and execute them accordingly. The FPGA can interact with external instrument circuitry via Input / Output ports. Thus, every command corresponds to appropriately controlling the equivalent FPGA IO ports, each time, which are connected to a specific part of the instrument.

#### 3.1 Instrument control

For the purpose of providing low-level instrument control and allow Omnitrap user to create a highly customizable experimental flow, following a different purpose each time, a bank of instrument actions is available through the User Interface. These actions are referred to as commands or instructions and each one of them represents a different experimental step. In Figure 6, a screenshot of the main user interface is presented. There are twenty four commands in total, with the first fourteen representing instrument functionalities and the remaining ten corresponding to ion transition actions, along the segmented ion trap, by the use of DC states manipulation. By clicking on a specific instruction, the corresponding command is added to the instruction list, where its arguments and real time experimental duration (in milliseconds) are shown. The arguments are also editable by the user in most of the commands. A brief description of the available instrument commands is given below:

- **Delay**: stalls the execution of the sequence by N milliseconds. As every action is executed by independent modules inside the FPGA, adding delays between commands is sometimes necessary, especially in cases where moving to the next action demands the completion of the previous command.

- **Gas Pulse 1 to 3:** Generates a helium gas pulse of configurable flux and duration inside the empty space of the ion trap. It is used for pressure management (mainly a gas pulse increases internal pressure) and speed manipulation of ions. There are three different gas pulse modules along the segmented ion trap. The main reason for this, is the fact that every gas pulse module needs a specific amount of time to be available for use again, while there are cases where multiple gas pulses are necessary to occur in close timing intervals.

- **Digital RF (KHz):** Sets the frequency of the rectangular RF signal that is being reproduced on the trap's electrodes. Different frequency values allow trapping of ions with different mass-to-charge ratio (m/z).

- **RF Amplitude (V):** Sets the amplitude of the rectangular RF.

- **Duty Cycle** [%]: Sets the duty cycle of the rectangular RF. Modifications on duty cycle have a determinant impact on the trapping efficiency, depending on the m/z range of the ions of interest.

- Gate/Modulate electrons: Actions that relate to substance ionization process.

- **Trigger IN:** Stall the sequence until a trigger pulse is generated by Q Exactive. This signal plays an important role on synchronizing the two instruments together. A rising edge of the trigger signal, notifies that ions are located inside the HCD cell of Q Exactive, and that they can be received by Omnitrap, if the appropriate DC state is applied.

- **Dipolar Excitation (Q2 or Q5):** Initializes the application of dipolar excitation isolation waveform on the corresponding segment of Omnitrap. This signal is mainly a sine waveform with configurable amplitude and frequency. Depending on the frequency of the dipolar sine wave, ion masses that have matching resonance frequencies are excluded

from the trap. The term <u>excitation</u> derives from the fact that all masses, except only a small mass range, remain inside the trap.

- Isolation Waveform (Q2 or Q5): Initialized the application of isolation waveforms. These are broadband signals which are distinguished in two kinds, the Filtered-Noise-Field and the Sweep signal, each one with different properties. Depending on the frequency content of the isolation waveform, all ion masses except the ones that their resonance frequency is not included in the signal's frequency spectrum are excluded from the trap. The term <u>isolation</u> derives from the fact that only a small range of masses remains inside the trap, while the rest are excluded.

- **DC states:** These commands are used to transfer ions between trap segments. Ions are moving from high to low voltage. Therefore, by applying high voltage to source segment and low voltage to destination segment, ion transfer inside the trap can be accomplished.

Sequence loop capabilities are also provided, in case an experimental process needs to be repetitively executed. An external and an internal loop and their repetition number are customizable through the user interface.

After sequence initialization, commands and their arguments are appropriately encoded to binary form and sent to FPGA, through communication methods that will be extensively examined in the upcoming chapters. These data are stored inside FPGA block RAM and a custom IP takes over their execution. Each command triggers an independent module which is responsible for the corresponding action. Multiple modules can run simultaneously without interfering each other. In this manner, high timing precision is accomplished, which is plays a major role issue in the success of the experiment. Finally, Custom digital logic is also responsible for controlling the loops inside the sequence.

#### 3.2 User Interface for waveform generation

#### **Purpose**

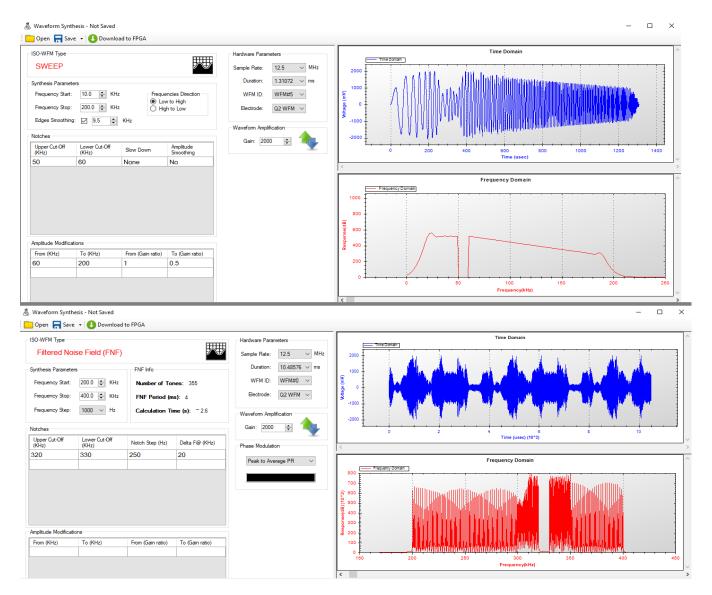

In order to efficiently experiment with isolation waveforms, like Sweep and FNF, convenient software User Interface is necessary. It is essential that software allows user to highly customize excitation waveforms, while UI remains comprehensive and easy to use. In addition to that, code must be robust, efficient and as simple as possible so that, potential future modifications will be easier to implement. Under this perspective, two Windows Forms (see Figure 7) where created to allow Sweep and FNF waveform synthesis. Their implementation and functionality are analytically described below. All code is written in C# programming language and user interface is developed using the Visual Studio environment.

Figure 7: Sweep and FNF user interface

#### 3.2.1 Sweep

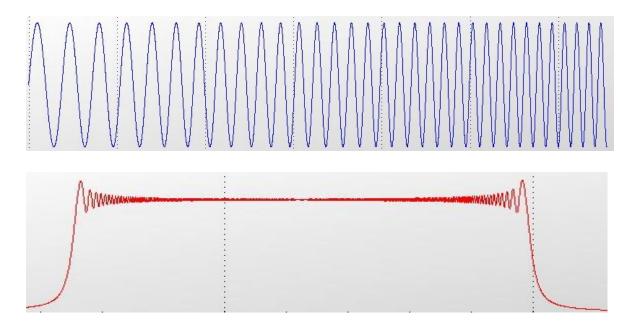

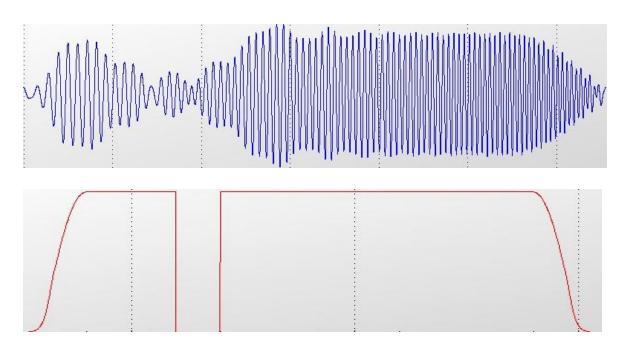

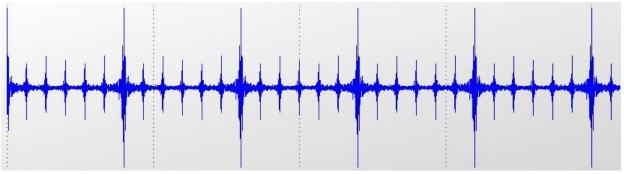

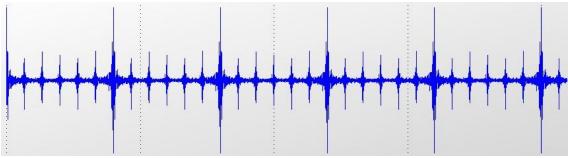

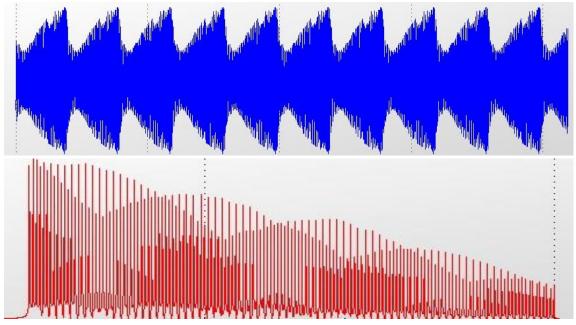

A sweep waveform is a harmonic function with linearly increasing frequency from an initial frequency to some final frequency (7). The foundation of the algorithm that generates such a broadband waveform is described in the following steps and visual representation of the results is also provided. The **blue** color represents the time domain while the **red** color represents the frequency domain:

• Calculation of the sweep signal in the time domain, according to the following mathematical expressions (where parameter *n* refers to discrete time):

Sweep(n) = sin [Phase(n)],

where  $\underline{Phase(n)}$  is calculated by the formula: Phase(n) = Phase(n-1) + 2pi \* Ts \* frequency(n), where Ts is the sampling period.

<u>Frequency(n)</u> is increasing linearly:  $frequency(n) = frequency(n-1) + frequency_step.$

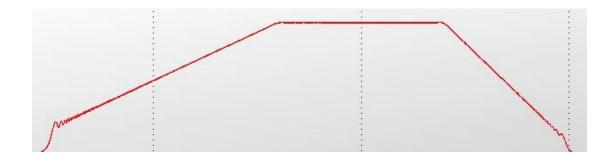

At its initial state, the shape of a sweep waveform is shown below:

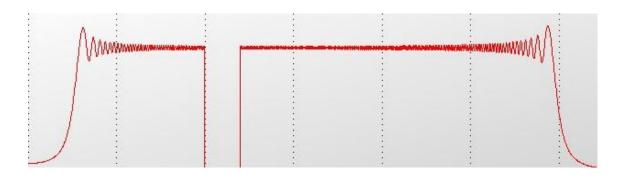

• Sweep function is then transformed into Fourier frequency domain, by means of Fast Fourier Transform. This way, amplitude and phase data are obtained for every discrete harmonic of the Fourier spectra. Objective of this procedure is to remove unwanted frequency components off the original sweep function and to obtain a new signal that does not contain unwanted components, but in other respect looks very similar to the original sweep. The main goal is to remove frequency components that cause resonance to the target isolation masses. Such frequency gaps are referred to the UI as frequency **notches**. In order to create a frequency notch that ranges from a frequency f<sub>1</sub> to a frequency f<sub>2</sub>, the amplitude of the equivalent harmonics in the frequency domain, is set to zero. A notch in the frequency domain, should look like this:

• Then, the signal is transformed back to time domain, by means of Inverse Fourier Transform (IFFT) :

Extra parameterizations of the sweep waveform are available in UI for the purpose of experimenting and optimizing the ion isolation process:

• Edge smoothing:

Some amplitude "spikes" near the starting and ending frequencies of the sweep waveform are obvious by examining the frequency domain plot. Such amplitude spikes are considered to potentially cause unwanted resonances. Thus, smoothing should be applied in the sweep edges by multiplying the sweep waveform with a reducing factor, which is given by the following mathematical expression:

$$factor(n) = \sin \left[\pm 1.57 * \left(\frac{n}{smoothing_{width}}\right)\right],$$

where positive sign is selected for smoothing the starting part of the sweep and negative sign is selected for the ending part. The edge smoothing results are shown below for both time and frequency domain:

Through UI, the length and rate of edge smoothing are both configurable.

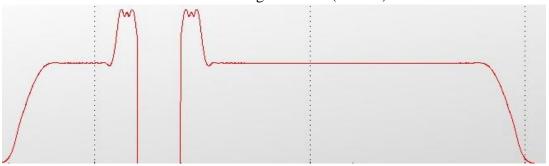

#### • Slow down around notch areas:

Intense and fast changes in frequency content near notch areas are experimentally shown to have negative impact in the isolation process. Therefore, reduction of the frequency change step around notch areas needs to occur. As the sweep duration and frequency range is initially specified, slowing down the frequency sweep in some regions leads to inevitable speed up of frequency sweep in every other waveform part. Through the implemented UI, user can configure the range and rate of the notch slow down as well as whether it occurs before or after entering the notch (or both).

The slowing down, as it occurs by the frequency domain plot above, leads to an increase in the amplitude of the harmonics where the slowdown occurred, and a decrease in the amplitude of the rest harmonics.

#### • Frequency sweep to opposite direction:

In some occasions, scanning of the required frequency range needs to occur in declining

order, from high to low frequencies. Therefore, this capability is also implemented and is configurable by the user.

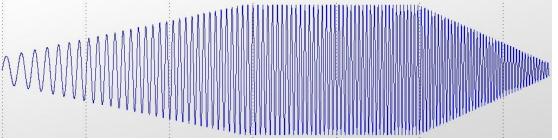

## • Amplitude modifications:

Through the implemented UI, user is given the possibility of generating his own custom amplitude modifications. Starting frequency, ending frequency, starting amplitude and ending amplitude can be configured. Applying an amplitude modification leads to a linear amplitude increase (if starting amplitude > ending amplitude) or decrease (if ending amplitude > starting amplitude) in the specified frequency interval. In the following example, two amplitude modifications are applied and their effect is visualized.

#### • Other configurations:

Sweep waveform generation is also configurable regarding sampling rate, total duration and target quadrupole (Q2 or Q5). Two sampling rates are available, 12.5 and 25 MHz.

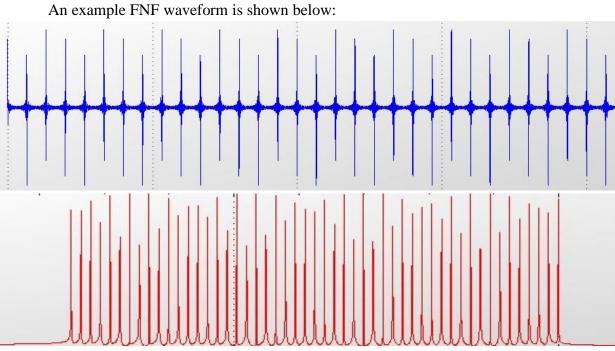

#### 3.2.2 FNF

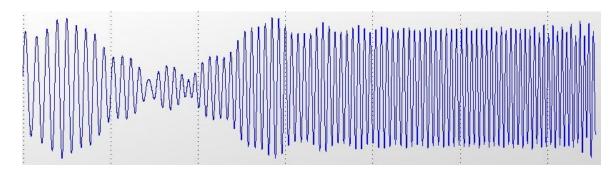

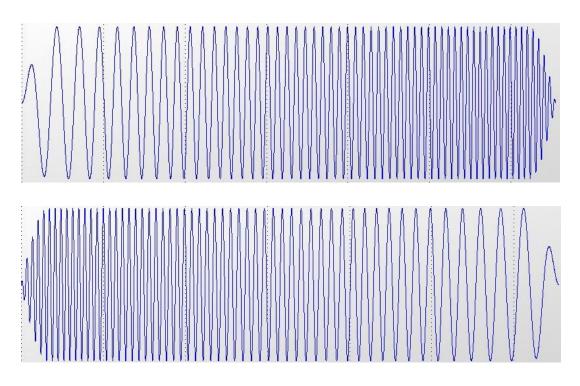

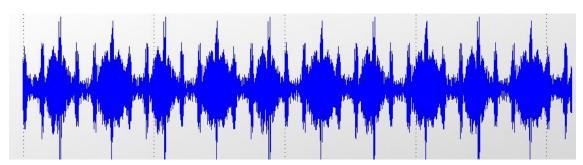

On the other hand, filtered noise field (FNF) waveforms constitute a completely different kind of broadband signals. FNF's basic feature is the fact that it reproduces all frequencies, inside a configurable interval, simultaneously, in comparison to sweep waveform which sweeps from smaller to higher frequencies over time (8). Consequently, its different properties make FNF a quite interesting field of study and experimentation. The steps for calculating an FNF waveform through software are the following:

- Configuring the number of frequency harmonics that the FNF waveform will incorporate. In this stage, harmonics inside desirable frequency notches are removed and thus the notch is created.

- Summing up all remaining harmonics in the time domain.

As it seems, the construction of an FNF waveform is fairly simple and straightforward. However, summing up a relatively large number of sinusoids is not computationally efficient and takes an infeasible amount of time. For this reason, a different approach to this computation is necessary. Finding the fundamental frequency of the FNF and subsequently summing up the frequency tones for only one waveform period is a quite efficient way of saving time and computational resources. The complete FNF waveform then can be calculated by concatenating multiple FNF period waveforms until desirable duration is achieved. Furthermore, the fact that there is no calculating dependence among FNF waveform points makes the calculation easy to be parallelized. By applying such contrivances, FNF calculation time is significantly reduced.

The most important FNF parameters that are configurable in the FNF user interface is the frequency content of the FNF (starting and ending frequency) as well as the frequency step. The division of frequency width with the frequency step provides the number of frequency tones which are incorporated by the FNF waveform. FNF duration, sample rate and target quadrupole are also configurable, similarly to sweep UI.

In comparison to sweep waveforms, this time the frequency domain is not continuous as it only includes some predefined frequency tones. As the configured frequency step decreases, the frequency spectrum of the calculated waveform gets denser and the frequency resolution is increased.

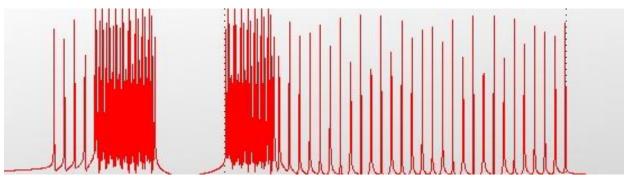

As already mentioned, the notch generation occurs by excluding from the summation, the frequency tones that belong to a desired notch. Apart from that, in most cases higher frequency resolution around notches is necessary, in order to allow more effective ion excitation in the corresponding frequencies. This feature is implemented in the FNF calculation code by modifying the frequency step around these areas. The range of effect as well as the frequency step before and after a notch area is configurable by the user. Visual representation of the incorporation of a notch in the FNF calculation is presented below:

As it seems in the frequency domain above, the frequency resolution around notches is increased while the amplitude of all frequency tones inside the notch is zero. Other available FNF configurations are the following:

#### • Phase modulation:

Adding frequency tones of equal phase results in uneven distribution of voltage levels in the waveform. In order to achieve even power distribution throughout the FNF signal, a phase modulation is necessary. There are unlimited choices regarding the mathematical expression that gives us an effective phase modulation, but the most widely used are the following:

$$\circ \underline{Newman Peak To Average Power Ratio:} \\ phase(n) = mod(n^2 * \frac{pi}{number_{oftones}} - 2pi, pi)$$

• Narahashi Peak To Average Power Ratio:

$$phase(n) = mod(n * (n - 1) * \frac{pi}{number_{oftones}} - 2pi, pi)$$

Besides these two phase modulation techniques, user can specify its own phase modulation expression, which better suits the application. An example before and after phase modulation is presented below:

Both the above FNF waveforms have similar frequency contents but the second one makes a superior power distribution and is experimentally feasible.

#### • Amplitude modifications:

Identical amplitude modification capabilities, as the sweep generation UI, are also available for FNF. A visual example is presented below, where the amplitude of frequency tones is linearly reduced from 100% to 20% of the initial value:

## 3.3 System level improvements

#### 3.3.1 FPGA Communication

While setting up robust digital logic and circuitry inside the FPGA seems as the most essential aspect of a digital design, securing solid communication between software (PC) and hardware (FPGA) is equally important. Data corruption and communication loss with hardware can lead to a series of negative consequences, from misleading experimental results to even instrument damage. Such events, can cause

huge delays to the instrument development process and decrease the overall instrument reliability. In addition, the fact that mass spectrometry analyzers, like Omnitrap, can be used for long periods of time (weeks or months) without shutting down, creates the extra requirement of constant data transaction verification and operation interrupt in case of communication failure. Therefore, the development of a stable communication channel with FPGA and techniques for real time evaluation of the data transfers is an urgent need.

For the current project, the data that need to be transmitted to the FPGA device are:

- The sequence of commands, which define Omnitrap's operational flow.

- **Samples of digital voltage waveforms**, which correspond to 12.5 MHz sample rate. These waveform points are generated and configured by developed PC user interface. These waveforms are intended to be used for ion excitation purposes.

Data that need to be received by the FPGA device are:

• ADC read-back values, which correspond to voltage and temperature measurements.

Nowadays, most products that require an interface to a host computer consider United Serial Bus (USB) as a primary option. USB is an industry standard that establishes specifications for cables and connectors, and protocols for connection, communication and power supply between computers and peripherals. It was firstly released in 1996 and its main purpose was to allow peripheral devices to connect with computers using a standard and common type of connectors. These connectors would make the use of peripherals more immediate while no host restart would be necessary for connecting or disconnecting a slave device.

Until today there have been released the following versions of the USB protocol, from oldest to latest:

- USB 1.0 (1.5 Mbit/s Low Speed, 12 Mbit/s Full Speed)

- USB 2.0 (1.5 Mbit/s Low Speed, 12 Mbit/s Full Speed, 480 Mbit/s High Speed)

- **USB 3.0** (5 Gbit/s SuperSpeed)

- USB 3.1 (10 Gbit/s SuperSpeed+)

- USB 3.2 (20 Gbit/s SuperSpeed+)

- **USB4** (40 Gbit/s SuperSpeed+ and Thunderbolt 3)

A USB interface can be added to an FPGA through USB protocol converter ICs. A USB protocol converter is an external device that incudes USB controller logic and can interact with FPGA, in a higher level than USB signaling, through a match simpler communication protocol. There are many choices available in the market regarding the methods that can be followed, with a variety in performance, ease of configuration, flexibility and time to market length. In the current thesis, some of the well-known FTDI USB bridge ICs are used for USB 2.0 and USB 3.0 connectivity in different

approaches and the results are evaluated.

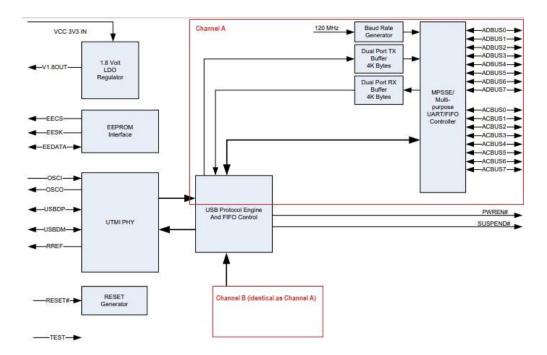

## 3.3.1.1 USB 2.0 to UART

The FPGA development board that is used for the current thesis incorporates the FT2232H chip by FTDI (Figure 8). This chip is a USB 2.0 to UART/FIFO bridge. It has two independent communication channels which can be configured in a variety of industry standard serial or parallel interfaces.

Figure 8: FTDI FT2232H block diagram

The chip can be easily configured through software. The configuration data are saved into the EEPROM interface and the configuration occurs on chip boot up. The functionality of each block is summarily described:

- <u>Multi-Purpose UART/FIFO controller</u>: There are two instances of them inside the chip, one for each channel. These control the UART or FIFO data.

- <u>USB Protocol Engine and FIFO control</u>: It controls and manages the interface between UTMI PHY and the FIFO memories. It is also responsible for power management and USB protocol specification

- <u>Dual Port FIFO TX Buffer</u>: Data coming from the Host PC are stored here until the channel master is available to receive them (maximum size: 4kBytes per channel)

- <u>Dual Port FIFO RX Buffer</u>: Data coming from the FPGA master are stored here until USB interface of PC is ready to receive them (maximum size: 4kBytes per channel)

- <u>RESET Generator</u>: Provides a reliable reset circuitry for the chip. External reset is also available if needed.

- <u>Baud rate Generators</u>: There are two of them, one for each channel. They are independent so that each channel can be configured in a different baud rate.

- <u>UTMI PHY</u>: Its name stands for Universal Transceiver Macrocell Interface. This block handles the USB SERDES (serialise deserialise) circuitry, which is compatible to USB 2.0 and backwards compatible to all other USB versions. It also provides the clocks for the rest of the chip.

Among the different available modes of the chip, the **USB 2.0 to RS232 UART** is chosen for the first implementation of the current project. In this mode of operation the chip functions as a protocol converter, which converts USB to dual wire UART (Rx and Tx wires) interface, to be handled by the FPGA. The term RS232 refers to the configuration circuitry of the chip and the appropriate voltage levels to operate.

## UART protocol

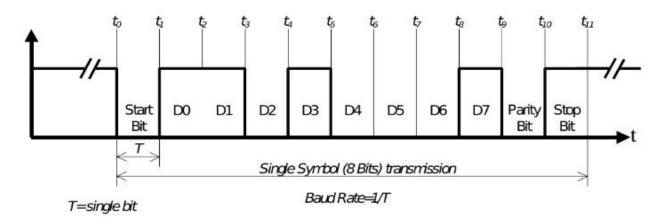

UART (Universal Asynchronous Receiver/Transmitter, Figure 9) is a serial asynchronous communication protocol and a circuit that allows data transfer between two (or more) devices that can be synchronous to different clocks. UART is widely used, due to its simplicity of implementation, practical ease of use and its general application capabilities.

UART's asynchronous communication takes place via a wired single bit connection, between the receiver (RxD), which drives the signal, and the transmitter (TxD) which samples and examines it (9). The data to be sent are usually whole bytes (8 bits) and are transmitted serially, bit by bit, from the least significant to the most significant bit. As there is no clock to synchronize the communication between the two devices, in asynchronous communication the data is preceded by a recognizable **start bit**. This signifies the receiver for the beginning of the communication. In a similar way, the transmission of a byte and the end of the communication is signified by the **stop bit**.

If needed, the UART bus can be customized so that it also incorporates a **parity bit**. The parity bit precedes the stop bit and includes information relative to the number of logic ones in the byte word that was sent. It is set to logic one by the transmitter, if the number of logic ones in the transmitting byte is even, and to logic zero if the number is odd.

Figure 9: UART protocol

In order to ensure that no data is lost or multiplied in the UART protocol, the transmitter and the receiver have to agree in advance regarding the sampling rate of the communication channel. This sampling rate is expressed in bauds, where each baud is equal to 1 bit per second. The configuration of baud rate is not part of the protocol and is done at a higher level. The standard and most commonly used baud rates are the following: 110, 150, 300, 1200, 2400, 4800, 9600, 19200, 38400, 57600, 115200, 230400, 460800 and 921600.

For a bidirectional communication system between two devices, which use UART protocol, two wires are needed, one for each data direction.

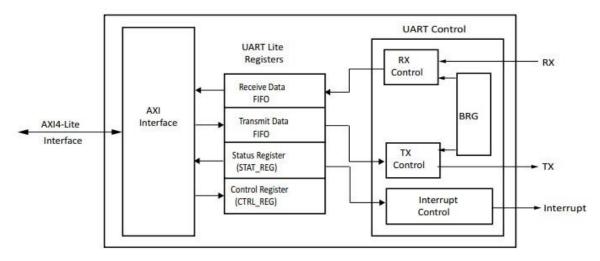

For the FPGA to interact with the UART bus, two I/O pins are necessary, a receiver (Rx) and a transmitter (Tx). Rx pin is used for data reception from USB to FPGA, while Tx pin is used for data transmission from FPGA to USB. Internal FPGA logic is also necessary. For this purpose, **AXI UARTlite** is used. It is a Xilinx Intellectual Property core which is capable of interacting with UART interfaces while communicating with FPGA's Programmable Logic (PL) via an **AXI4 Lite** slave interface.

### FPGA Design

#### AXI BUS

AXI, which stands for Advanced eXtensible Interface, is an interface protocol defined by ARM as part of the AMBA standard (10). AMBA is an open standard for SoC (System-on-Chip) design created by ARM to allow for high performance, modular, and reusable designs that are reliable while minimizing both power and silicon. In the current project the AXI4 version of AXI is used (which responds to AMBA 4.0 version). There are three types of AXI4-interfaces:

• **AXI4 (Full AXI4)**: It is used for memory- mapped data transfer. In this communication protocol, for every data transfer, an address is required, which is followed by the transaction data. Data size can vary from 1 to 256 words while data word size ranges

from 32 to 128 bits. The AXI4 Full can interconnect multiple master to multiple slaves that correspond to the same bus protocol.

- **AXI4-Lite**: This protocol is a simplified version of AXI4 Full. It is also a memorymapped protocol but it does not allow transactions of multiple data words (burst transactions). Thus, for each data word transfer, a data address is required. The data word size ranges from 32 to 128 bits. The implementation of this bus needs less resources, which is its major advantage in comparison to AXI4 Full

- **AXI4-Steam**: Is not a memory-mapped protocol. It is used for very fast data transfer from a single master to a single slave. It supports burst transactions of unlimited size and it is the fastest of the three AXI4 protocols.

# IP cores

## **AXI UARTlite**

This Xilinx Intellectual Property core is shown in Figure 10. It executes serial to parallel data conversion for data that come from UART interfaces and parallel to serial data conversion for data that come from AXI4 Lite interfaces. It can be configured to manage data words of 5, 6, 7 or 8 bits. Furthermore, a parity bit is available if needed. It incorporates a transmit and a receive FIFO, each one of 16 data words depth. In case receive FIFO is full, data from UART interface are not received. Respectively, if transmit FIFO is full, AXI data are rejected and an AXI bus error is generated so that it notifies PL that the transaction failed. Finally the core can accept and assert interrupt signals (11).

Figure 10: AXI UartLite block diagram

Two registers are available to give information about the status of the IP and offer IP control capabilities. More specifically the status register provides the status of the receive and transmit data

FIFOs and asserts error bits if an error occurs. On the other side, control register contains the enable interrupt bit and the reset bit for the receive and transmit FIFOs.

Using the appropriate input clock, the IP can be configured to support all standard UART protocol baud rates from 110 to 921600. Block diagram of UARTlite IP core is shown above.

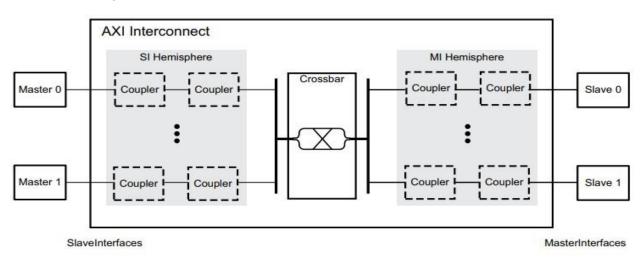

## **AXI Interconnect**

As mentioned above, AXI Interconnect is a Xilinx Intellectual Property core which is used for connecting one or multiple master to one or multiple slave interfaces (12). The block diagram of the IP core is shown in Figure 11.

Figure 11: AXI Interconnect block diagram

The core constitutes of three sub-cores, the slave interface (SI), the master interface (MI) and the crossbar IP. AXI4 Master Interfaces are connected to SI while AXI4 Slave interfaces are connected to MI. Through SI masters can issue transaction read or write commands and wait for the related slaves to respond.

The AXI Interconnect implementation is automatically configured based on the number and kind of master and slave interfaces that are connected to it. The implementation kinds are the described below:

• Pass through (1 to 1):

In case only one master and one slave of identical protocol are connected, the AXI Interconnect IP does not need to implement protocol conversion or pipelining functionalities. Subsequently, the two interfaces are connected directly and the core does not occupy hardly any resources.

• Conversion only (1 to 1): In case a data width conversion, a clock rate conversion, an AXI4-Lite slave adaption or pipelining needs to occur, the implementation only omits the circuitry that is responsible for arbitration, decoding and command fetching.

## • N-to-1 Interconnect:

In case multiple masters are connected to a unique slave, arbitrary circuitry is implemented so that each time only one master has access to that slave. In addition, protocol conversion circuitry is included if needed.

## • 1-to-N Interconnect:

In case one master has access to multiple slaves there is no need for arbitrary logic. However, circuitry which decodes and issues the commands each time to the corresponding slave, is necessary.

## • N-to-M Interconnect (Crossbar Mode):

In case multiple masters are connected to multiple slaves, the AXI Interconnect implements intermediate logic manages the transaction commands, even multiple commands at a time.

## • N-to-M Interconnect (Shared Access Mode):

Same as crossbar mode, except in this mode commands are issued one at a time. Subsequently, this implementation consumes fewer resources but the AXI transactions are slower.

## Microblaze

Microblaze is the processing core that Xilinx offers to be used for 7-Series FPGA architectures. It is a soft core which means that it is implemented by the FPGA LUT (Logic Unit Table) cell resources (13). It incorporates 32bit RISC architecture with pipelining capabilities and it is highly customizable. Furthermore, it can be customized so that it responds to different kinds of events like resets, interrupts and exceptions.

Microblaze communicates with others IP cores through the AXI4 bus. For this purpose, AXI Interconnect IP core is a precious tool as it can connect multiple masters (one of them is obviously Microblaze) with multiple slaves that correspond to different kinds of AXI4 protocols.

## **Memory Interface Generator**

The Memory Interface Generator constitutes a Xilinx Intellectual Property core. It is a combined preengineered controller for interfacing 7 series FPGA user designs and AXI4 slave interfaces, to DDR3 and DDR2 SDRAM devices (14). This core is used in our design as a memory controller which allows robust communication from our custom FPGA logic to the DDR3 memory, through AXI4 protocol bus. It also includes internal logic for monitoring the DDR3 temperature and keeping its functionality within safety limits.

## **Block Design**

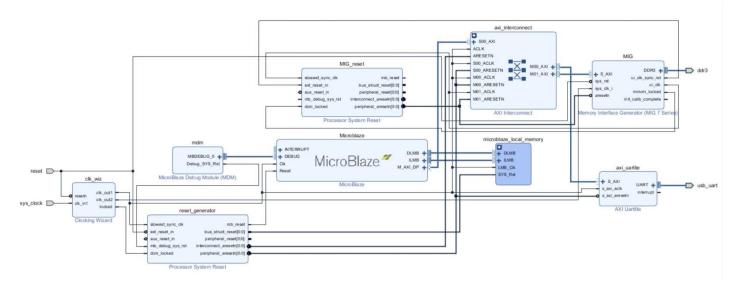

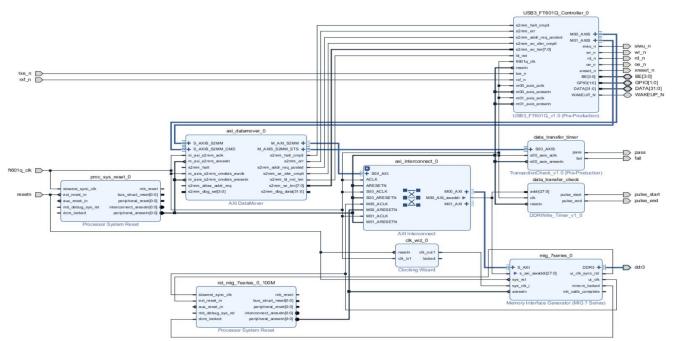

The purpose of this FPGA design is to set up a communication channel between PC software and FPGA hardware which will serve the waveform data download and some extra functionality like setting up ADC values and reading back DAC values. Creating the FPGA design for this purpose is fairly straightforward and does not demand custom IP generation. The Xilinx IP cores mentioned above are enough for our current demands. The FPGA design is shown in Figure 12.

Figure 12: Implementation of PC-FPGA communication based on UART protocol

In this block design, a clock wizard is responsible for creating two clocks, clk\_out1 of 75 MHz and the clk\_out2 of 200 MHz, from the input system clock of 100 MHz. The clock of 75 MHz is the input clock for AXI UARTlite IP. Such a clock frequency is selected as it allows configuration of the UART channel in maximum baud rate of 921600. Microblaze is also clocked at 75MHz.

On the other hand, the 200MHz clock rate is used as the input clock of MIG controller. The MIG controller is responsible for executing every DDR3 transaction that an AXI4 master requests. Microblaze soft-core possesses the only AXI4 master interface in the design so it is the only IP that can initiate DDR3 transactions.

For the purpose of supporting multiple functionalities in the same data channel, it is obvious that some common rules between software and hardware need to be established. In our case, a convenient way of achieving this is by setting up a group of identifier bytes. The idea is that the PC through software will transmit bytes from an "identifier bytes bank" and the hardware will reply by executing the corresponding action every time. The identifier bytes that are used and a brief description of the action they are linked to are presented below:

• **CONNECT** (0xFD): Opens a connection port between the software (PC) and the hardware (FPGA).

- **DISCONNECT** (0xFE): Closes an already opened connection port between the PC and the FPGA.

- **EXECUTION\_START** (0x1D): Starts the execution of the commands sequence.

- **EXECUTION\_STOP** (0x1E): Stops the execution of the commands sequence.

- **READ\_SEQUENCE\_STATUS** (0x3A or 0xF6): Returns the status of the command sequence (Idle or Running)

- **READ\_LOOP\_COUNTER** (0x3B): Returns the number of times that the command sequence has been executed

- **DOWNLOAD\_SEQ** (0x1C): Initializes the command sequence download. This means that the next bytes that are sent to the FPGA represent command sequence data.

- **READ\_RTD\_X** (0xF7 or 0x2F or 0xF9 or 0xFA): Returns the measurement of resistance thermometer X after averaging it in a window of size 16. Four resistance thermometers are available so integer X can range from values 1 to 4.

- **SET\_RF\_I** (0xF8): Set the current (I) value of the RF (radio frequency) Power Supply Unit.

- **READ\_RF\_V** (0x3D): Returns the voltage value of the RF Power Supply Unit.

- **READ\_RF\_I** (0x2E): Returns the current value of the RF Power Supply Unit.

- **DOWNLOAD\_WFM** (0xFC): Initializes a waveform data download process. This means that the next bytes which are sent to the FPGA represent waveform data.

- **UPLOAD\_WFM** (0xFB): Read the waveform data saved to DDR3 (mainly used for evaluation purposes)

This set of predefined identifier bytes are considered known for both the transmitter (PC) and the receiver (FPGA), while Microblaze is responsible for executing each functionality. Using Xilinx Software Development Kit (SDK) a loop process is written in C code, for the Microblaze to execute by the time the FPGA is powered on. This process is a polling function which waits for data to be available in the UART channel. When the first byte is available, Microblaze receives it and acts accordingly. By the time an action is complete, Microblaze is polling until the next request.

This process can be also implemented using interrupts. Each time data are available in UART interface, an interrupt occurs. Microblaze accepts the interrupt and realizes the equivalent operation, according to the identifier byte that is received. In this manner, Microblaze is not polling when UART data are missing and can be used for further operational load. As in our design, Microblaze functionality is limited to UART demands serve, interrupt logic is excluded so that minimum FPGA resources are occupied.

For the purpose of executing the actions mentioned above, like triggering execution start or saving data to DDR3, Microblaze (PS) (programmable Software - Microblaze) needs to communicate with PL (Programmable Logic - IPs). This communication occurs through AXI4 bus. In order for Microblaze master to set reading or writing requests to a target slave, functions Xil\_In and Xil\_Out are used accordingly. These functions are already implemented in the board support package, which can be automatically generated by Vivado SDK tool for every FPGA design. They can perform input or output

operations of 8, 16, 32 and 64 bits for AXI4 memory mapped registers. More specifically, Xil\_In function takes, as its unique parameter, the AXI4 slave address and returns the corresponding data word. On the other hand, Xil\_Out takes as variables the AXI4 target slave address and the data word to be written.

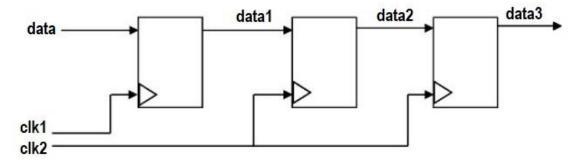

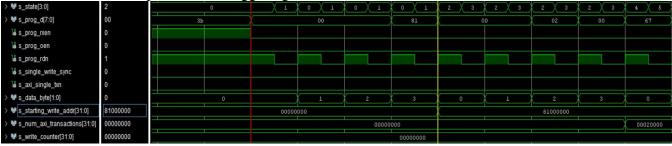

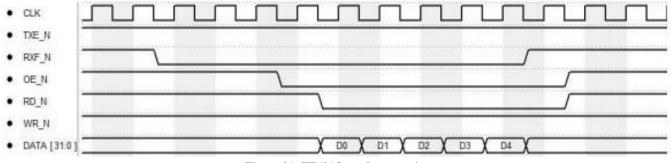

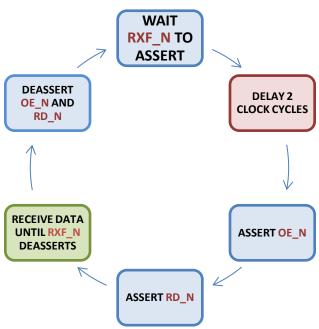

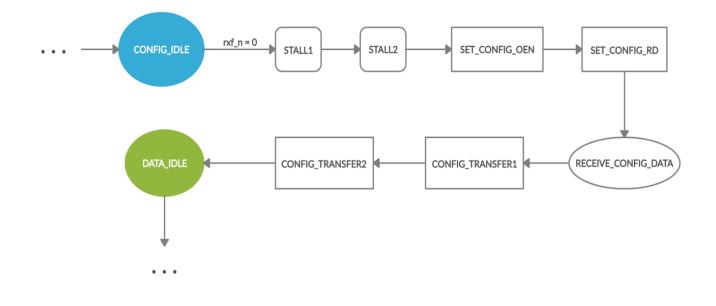

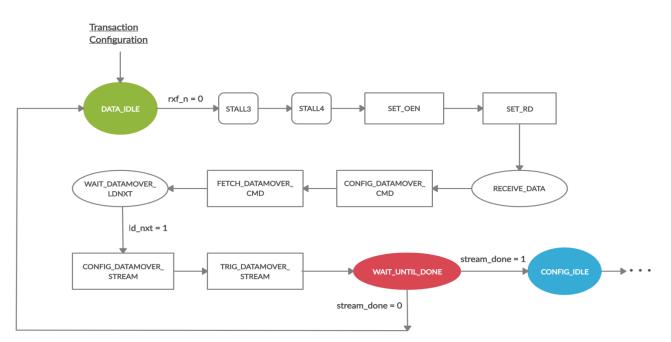

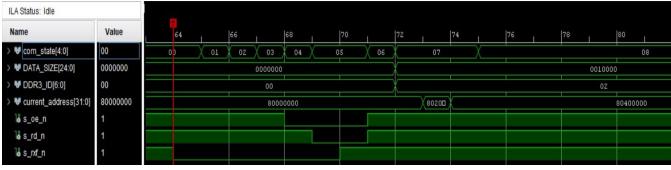

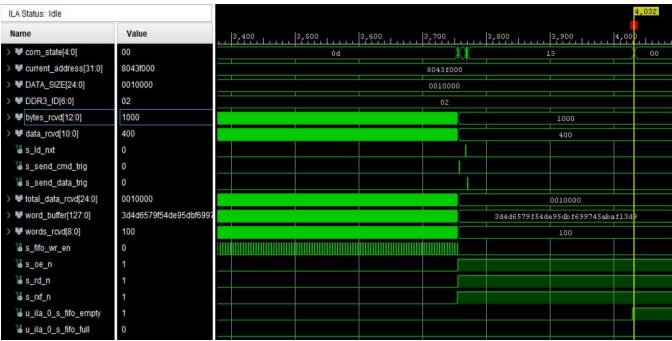

## 3.3.1.2 USB 2.0 to FIFO245 Synchronous