#### ΕΘΝΙΚΟ ΜΕΤΣΟΒΙΟ ΠΟΛΥΤΕΧΝΕΙΟ ΣΧΟΛΗ ΗΛΕΚΤΡΟΛΟΓΩΝ ΜΗΧΑΝΙΚΩΝ ΚΑΙ ΜΗΧΑΝΙΚΩΝ ΥΠΟΛΟΓΙΣΤΩΝ ΤΟΜΕΑΣ ΤΕΧΝΟΛΟΓΙΑΣ ΠΛΗΡΟΦΟΡΙΚΗΣ ΚΑΙ ΥΠΟΛΟΓΙΣΤΩΝ

#### ΔΙΠΛΩΜΑΤΙΚΗ ΕΡΓΑΣΙΑ

# Memory Management in Hybrid DRAM/NVM Systems using LSTMs $\,$

# Κωνσταντίνος Γ. Σταυρακάκης A.M. : 03116155

Επιβλέπων : Δημήτριος Ι. Σούντρης Καθηγητής ΕΜΠ

> Αθήνα Φεβρουάριος 2022

ΕΘΝΙΚΟ ΜΕΤΣΟΒΙΟ ΠΟΛΥΤΕΧΝΕΙΟ ΣΧΟΛΗ ΗΛΕΚΤΡΟΛΟΓΩΝ ΜΗΧΑΝΙΚΩΝ ΚΑΙ ΜΗΧΑΝΙΚΩΝ ΥΠΟΛΟΓΙΣΤΩΝ ΤΟΜΕΑΣ ΤΕΧΝΟΛΟΓΙΑΣ ΠΛΗΡΟΦΟΡΙΚΗΣ ΚΑΙ ΥΠΟΛΟΓΙΣΤΩΝ

ΔΙΠΛΩΜΑΤΙΚΗ ΕΡΓΑΣΙΑ

## Memory Management in Hybrid DRAM/NVM Systems using LSTMs

# Κωνσταντίνος Γ. Σταυρα<br/>κάκης Α.Μ. : 03116155

Επιβλέπων : Δημήτριος Ι. Σούντρης Καθηγητής ΕΜΠ

Τριμελής Επιτροπή Εξέτασης

(Υπογραφή)

(Υπογραφή)

(Υπογραφή)

Δημήτριος Σούντρης Παναγιώτης Τσανάχας Γεώργιος Γκούμας Καθηγητής Καθηγητής Αναπληρωτής Καθηγητής ĖМП

ЕMП

ĖМП

Ημερομηνία Εξέτασης: 18 Φεβρουαρίου 2022

Copyright © - All rights reserved Σταυραχάχης Κωνσταντίνος, 2022. Με επιφύλαξη παντός διχαιώματος.

Απαγορεύεται η αντιγραφή, αποθήκευση και διανομή της παρούσας εργασίας, εξ΄ ολοκλήρου ή τμήματος αυτής, για εμπορικό σκοπό. Επιτρέπεται η ανατύπωση, αποθήκευση και διανομή για σκοπό μη κερδοσκοπικό, εκπαιδευτικής ή ερευνητικής φύσης, υπό την προϋπόθεση να αναφέρεται η πηγή προέλευσης και να διατηρείται το παρόν μήνυμα. Ερωτήματα που αφορούν τη χρήση της εργασίας για κερδοσκοπικό σκοπό πρέπει να απευθύνονται προς τον συγγραφέα.

Οι απόψεις και τα συμπεράσματα που περιέχονται σε αυτό το έγγραφο εκφράζουν τον συγγραφέα και δεν πρέπει να ερμηνευθεί ότι αντιπροσωπεύουν τις επίσημες θέσεις του Εθνικού Μετσόβιου Πολυτεχνείου.

(Υπογραφή)

\_\_\_\_\_

#### Σταυρακάκης Κωνσταντίνος

Διπλωματούχος Ηλεκτρολόγος Μηχανικός και Μηχανικός Υπολογιστών Ε.Μ.Π. ©2022 - All rights reserved.

# Περίληψη

Είναι πλέον ευρεία η ενσωμάτωση των τεχνολογιών ετερογενών μνημών στα σύγχρονα υπολογιστικά συστήματα προκειμένου να αντιμετωπιστεί η συνεχώς αυξανόμενη ανάγκη των αναδυόμενων εφαρμογών για όλο και μεγαλύτερο μέγεθος κύριας μνήμης. Αυτές οι νέες τεχνολογίες παρουσιάζουν αρκετές διαφορές μεταξύ τους όσον αφορά το μέγεθος, την καθυστέρηση πρόσβασης αλλά και το εύρος ζώνης. Αυτή η γενικότερη ετερογένεια των νέων συστημάτων καθώς και οι ίδιες οι ιδιαιτερότητες των νέων εφαρμογών καθιστούν ανεπαρκείς τις σύγχρονες πρακτικές διαχείρισης μνήμης.

Σε αυτή τη διπλωματική σχεδιάσαμε και αξιολογήσαμε έναν δρομολογητή, ο οποιος έξυπνα τοποθετεί τα δεδομένα των εφαρμογών, σε επίπεδο Σελίδων Μνήμης, στα διάφορα στοιχεία μνήμης του συστήματος χρησιμοποιώντας Τεχνητά Νευρωνικά Δίκτυα. Ο δρομολογητής που προτείνουμε συνδυάζει τη χρήση LSTM Δικτύων με τις υπάρχουσες μεθόδους διαβάθμισης των δεδομένων που στηρίζονται στο Ιστορικό των δεδομένων αυτών. Ο δρομολογητής μας έξυπνα χρησιμοποιεί μηχανική μάθηση μόνο για ένα υποσύνολο σελίδων, οι οποίες αν μετακινηθούν στο σωστό χρόνο θα επιτευχθεί σημαντική αύξηση της απόδοσης. Ακόμα χρησιμοποιώντας την τεχνιχή K-Means για τον χωρισμό του Πεδίου Διευθύνσεων σε Συστάδες, ο χρονοδρομολογητής ενισχύει το πλήθος των πληροφοριών με βάση το οποίο θα παίρνονται οι αποφάσεις για την απομάχρυνση δεδομένων απο τη DRAM. Έτσι βλέπουμε ότι επιτυγχάνεται κατά μέσο όρο μια αύξηση της απόδοσης περίπου 10% σύμφωνα με τη διαδικασία αξιολόγησης που ακολουθήσαμε. Επίσης, επιβεβαιώσαμε ότι ο προτεινόμενος δρομολογητής μπορεί να γεφυρώσει ιχανοποιητικά το χάσμα απόδοσης μεταξύ των σύγχρονων λύσεων και ενός δρομολογητήμάντη με a priori γνώση της συμπεριφοράς των δεδομένων. Και τέλος, αξιολογώντας ενεργειακά τον δρομολογητή που σχεδιάσαμε προκύπτει ότι θα μπορούσε να είναι μια αξιόλογη πρόταση για συστήματα τα οποία ειναι σχεδιαστικά προσανατολισμένα στη χαμηλή κατανάλωση ενέργειας.

**Λέξεις Κλειδιά** — Συστήματα Ετερογενών Μνημών, Μηχανική Μάθηση, Νευρωνικά Δίκτυα, LSTM, K-Means, NVM, Επαναληπτικά Νευρωνικά Δίκτυα, Δρομολόγηση Σελίδων, DRAM

## Abstract

Heterogeneous memory technologies have been widely used in effort to address the ever-increasing demands of modern applications for larger main memory capacity. The new technologies showcase vastly greater differences in terms of capacity, latencies and bandwidth. This heterogeneity along with the the greater irregularity of emerging workloads, render state-of-the-art memory management solutions insufficient; thus calling for more intelligent methods.

In this diploma Thesis, we design and evaluate a scheduler which intelligently places application data, on a Page granularity, across hybrid memory components using Artificial Neural Networks. The proposed Scheduler combines intelligent page placement decisions leveraging LSTM networks with existing history-based data tiering methods. The scheduler focuses the machine learning on a page subset whose timely movement will reveal most application performance improvement, while being mindful of computation resources. K-Means address space clustering is also utilized to augment the eviction policy used by the proposed scheduler in order to provide application performance boost. That boost is on average 10% according to our evaluation process. Our performance evaluation also indicates that the proposed Scheduler significantly reduces the performance gap between existing solutions and an oracle scheduler with a priori knowledge of the page access patterns, while being a potential candidate for designing low-power oriented Hybrid Memory Systems as well.

**Keywords** — Heterogeneous Memory Systems, Machine Learning, Long Short Term Memory Networks, K-Means, Non Volatile Memory, Recurrent Neural Networks, Page Scheduling, DRAM

# Ευχαριστίες

Αρχικά, ευχαριστώ θερμά τον καθηγητή μου, κ. Δημήτριο Σούντρη, για την εμπιστοσύνη που μου έδειξε από την πρώτη μας επικοινωνία μέχρι και σήμερα. Επίσης, ένα μεγάλο ευχαριστώ στους υποψήφιους διδάκτορες κ.κ. Μασούρο και Κατσαραγάκη για την εξαιρετική συνεργασία μας και την ακούραστη καθοδήγηση που μου προσέφεραν. Τέλος, ευχαριστώ απο καρδιάς τους γονείς μου, τον αδερφό μου, και τους φίλους μου για την απεριόριστη στήριξη και ώθηση που μου έδωσαν καθ΄ όλη την ακαδημαϊκή μου πορεία.

## Contents

| Περίληψη                                                  | 5                          |  |  |  |  |

|-----------------------------------------------------------|----------------------------|--|--|--|--|

| Abstract                                                  |                            |  |  |  |  |

| Ευχαριστίες 9                                             |                            |  |  |  |  |

| Contents                                                  | 11                         |  |  |  |  |

| Εκτεταμένη Περίληψη<br>Εισαγωγή                           | 17<br>19<br>22<br>24<br>27 |  |  |  |  |

| 1       Introduction         Thesis Topic                 | 32<br>33                   |  |  |  |  |

| 2 Related Work Hardware Solutions                         | 35                         |  |  |  |  |

| 3 Persistent Memory & Memory Management Persistent Memory | 42<br>43<br>44             |  |  |  |  |

|          | Page Migration Challenges                     | 47        |

|----------|-----------------------------------------------|-----------|

|          | Implementation Overhead                       | 47        |

|          | Data Retrieval                                | 48        |

|          | Page Movement                                 | 49        |

| 4        | Machine Learning & Deep Neural Networks       | 51        |

|          | Machine Learning Background                   | 51        |

|          | Types of Machine Learning                     | 51        |

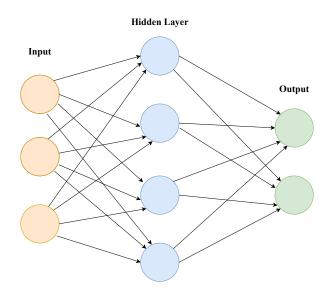

|          | Artificial Neural Networks                    | 53        |

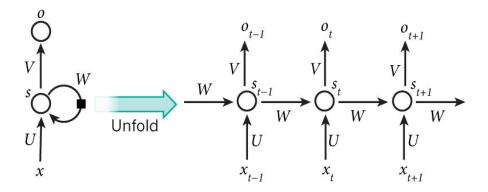

|          | Recurrent Neural Networks                     | 60        |

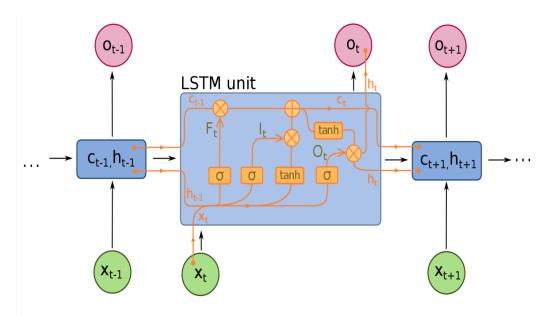

|          | LSTMs                                         | 61        |

|          | Page Scheduling as a Machine-Learning problem | 63        |

|          | Reinforcement Learning Approach               | 63        |

|          | Recurrent Neural Network Approach             | 63        |

|          | Neural Network Input                          | 65        |

|          | Deltas Prediction                             | 65        |

|          | Per Page Prediction Approach                  | 68        |

| <b>5</b> | Proposed Page Scheduler Architecture          | <b>71</b> |

|          | Critical Metrics                              | 71        |

|          | Page Scheduler Overview                       | 74        |

|          | Page Scheduler Components                     | 76        |

|          | Page Selector                                 | 76        |

|          | Access Count Predictors                       | 79        |

|          | DRAM Eviction Policy                          | 80        |

| 6        | Technical Implementation                      | 83        |

|          | Benchmark workloads                           | 83        |

|          | Collecting Memory Access Traces               | 85        |

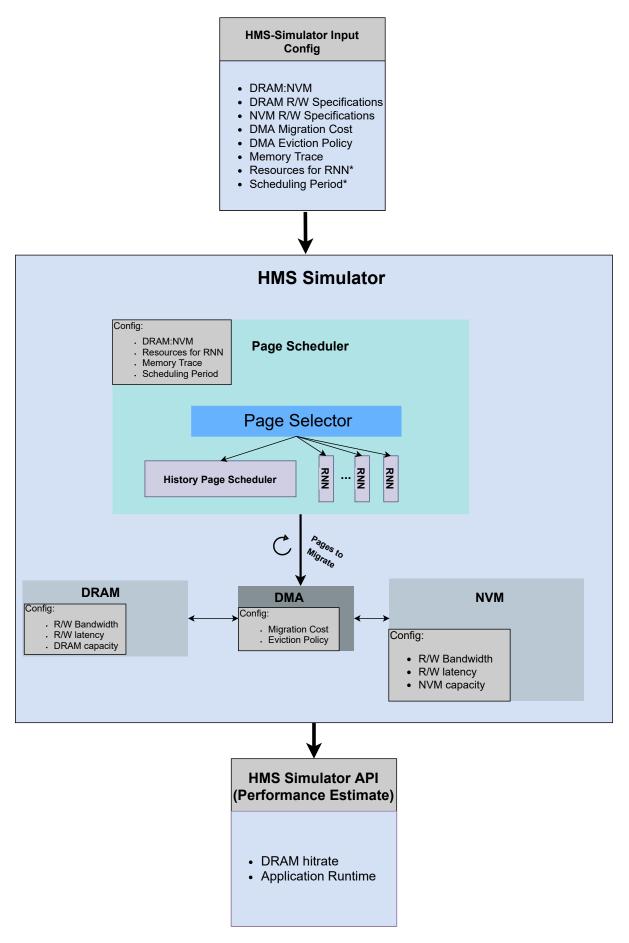

|          | Hybrid Memory System Simulator                | 86        |

|          | Recurrent Neural Networks Details             | 86        |

|          | Neural Network Input                          | 86        |

|          | Neural Network Configuration                  | 89        |

| 7        | Experimental Evaluation                       | 91        |

|          | RNN Prediction Accuracy                       | 91        |

|          | Application Performance                       | 93        |

|          | Eviction Policy                               | 95        |

|          | Energy Consumption                            | 96        |

|          |                                               |           |

| 8 | Conclusions    | 105 |

|---|----------------|-----|

|   | Thesis Summary | 105 |

|   | Future Work    | 106 |

## Εκτεταμένη Περίληψη

## Εισαγωγή

Τα τελευταία χρόνια παρατηρείται εκτεταμένη διείσδυση της Μηχανικής Μάθησης σε κάθε κλάδο. Η Μηχανική μάθηση αποτελεί παράγοντα καινοτομίας σε ένα μεγάλο φάσμα εφαρμογών που περιλαμβάνει απο εμπορικά προϊόντα έως και ιατρικές εφαρμογές. Η ευρύτητα αυτού του φάσματος, σε συνδυασμό με το γεγονός ότι η απόδοση των μοντέλων που αναπτύσσονται με τεχνικές μηχανικής μάθησης είναι αρκετά καλή μοντελοποιώντας εφαρμογές που παραδοσιακά θα ήταν αρκετά περίπλοκο να μοντελοποιώντας εφαρμογές που παραδοσιακά θα ήταν αρκετά περίπλοκο να μοντελοποιώντας εφαρμογές που παραδοσιακά θα ήταν αρκετά περίπλοκο να μοντελοποιήθούν, ωθούν στην ραγδαία ανάπτυξη της. Ταυτόχρονα, στον κλάδο της αρχιτεκτονικής υπολογιστών η προόδος που προβλέπεται απο το νόμο του Μοορε φαίνεται ότι σταδιακά παύει να ακολουθεί το εκθετικό μοτίβο αύξησης που ακολουθούσε έως τώρα, ενώ το χάσμα επιδόσεων μεταξύ μνήμης και επεξεργαστή δεν εχει γεφυρωθεί ακόμα. Οι δύο αυτές τάσεις, δηλαδή η εξέλιξη της Μηχανικής Μάθησης και τα ίδια τα προβλήματα που υπάρχουν στην Αρχιτεκτονικής τοι ώστε η μηχανική μάθηση να υποστηρίζεται αλλα κυρίως να υποστηρίζει την αρχιτεκτονική.

Είναι γνωστό ότι τα σύγχρονα υπολογιστικά συστήματα σχεδιάζονται χρησιμοποιώντας ετερογενή συστατικά μνήμης. Αυτές οι μνήμες συχνά είτε εξυπηρετούν στην αύξηση της χωρητικότητας της κύριας μνήμης, δηλαδή σαν επέκταση της DRAM, είτε αξιοποιούνται ως κρυφές-μνήμες (caches) της κύριας μνήμης. Αυτά τα υβριδικά συστήματα μνήμης συνοδεύονται εκ φύσεως με κάποιους σχεδιαστικούς συμβιβασμούς. Συνήθως η μακρύτερη στην ιεραρχία μνήμη, δηλαδή μνήμη που βρίσκεται πιο μακρία απο την Επεξεργαστική Μονάδα, έχει μεγαλύτερη χωρητικότητα αποθήκευσης αλλά ταυτόχρονα έχει και μεγαλύτερη καθυστέρηση πρόσβασης (latency) και μειωμένο εύρος ζώνης (bandwidth).

Στη συγκεκριμένη διπλωματική εργασία θα περιοριστούμε σε υπολογιστικά συστήματα τα οποία αξιοποιούν την Persistent Memory ως επέκταση της κύριας μνήμης. Για το σχεδιασμό αυτών των συστημάτων είναι ιδιαίτερα σημαντικό να ληφθούν υπόψιν το μεγαλύτερο latency και το μειωμένο bandwidth που παρουσίαζει αυτή η μνήμη σε σχέση με τη DRAM. Στη συγκεκριμένη περίπτωση αυτό που μας ενδιαφέρει είναι η αποδοτική υλοποιήση ενός Χρονοδρομολογητή Σελίδων Μνήμης (Page Scheduler), δηλαδή η αποδοτική υλοποίηση της μονάδας που αναλαμβάνει

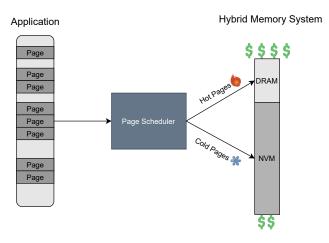

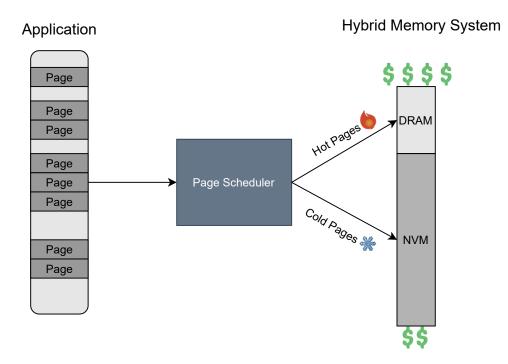

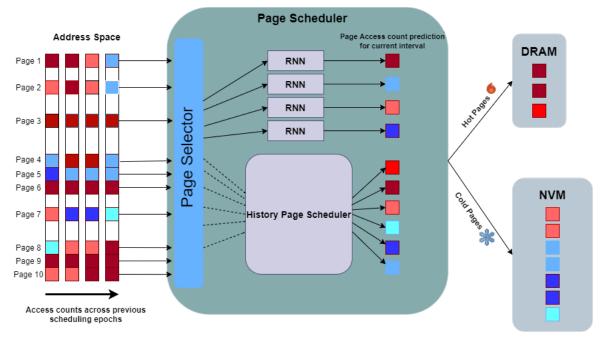

τη διαχείριση της μνήμης του λειτουργικού συστήματος αλλά και των εν εκτελέση προγραμμάτων. Ο χρονοδρομολογητής σελίδων θα είναι υπεύθυνος για τη μεταφορά σελίδων μνήμης απο και προς τα διάφορα ετερογενή συστατικά μνήμης που απαρτίζουν το σύστημα μας. Κύριο σκοπό θα έχει οι σελίδες μνήμης που θεωρούνται hot, δηλαδή προσπελαύνονται συχνά, να βρίσκονται στα υψηλής απόδοσης στοιχεία μνήμης που διαθέτει το σύστημα μας, δηλαδή στη DRAM, ενώ λιγότερο σημαντικές σελίδες μνήμης cold να βρίσκονται στην Persistent Memory. Μια διαγραμματική επεξέγηση του πρόβληματος που προσπαθούμε να αντιμετωπίσουμε σε αυτή τη διπλωματική φαίνεται στο διάγραμμα 1.

Ειχόνα 1: Χρονοδρομολογητής Σελίδων σε ένα Hybrid Memory System

## Κίνητρο και συναφείς προσεγγίσεις

Πολλοί ερευνητές έως τώρα έχουν αποπειραθεί να δώσουν μια λύση στο πρόβλημα της κατηγοριοποίησης των σελίδων μνήμης και στην κατάλληλη τοποθέτηση τους στα διάφορα ετερογενή στοιχεία μνήμης. Πρόκειται σίγουρα για μία δύσκολη διαδικασία καθώς πρέπει να ληφθούν υπόψιν και το μοτίβο προσπέλασης μνήμης που ακολουθεί μία εφαρμογή όσο και οι παράμετροι εκτέλεσης της εφαρμογής (μέγεθος του input, strong/weak scaling κλπ). Οι περισσότεροι ερευνητές έχουν προτείνει λύσεις στο παραπάνω πρόβλημα που μπορούν να ενσωματωθούν στο επίπεδο του hardware, των Compilers, του Λειτουργικού Συστήματος και του περιβάλλοντος εκτέλεσης [1, 2, 3, 4, 5, 6, 7]. Συχνά οι ερευνητές σε αυτές τις προσεγγίσεις χρησιμοποιούν πληροφορίες που σχετίζονται μονάχα με το ιστορικό προσπέλασης των σελίδων μνήμης. Συγκεκριμένα οι σύγχρονες τεχνικές που χρησιμοποιούν την πρόσφατη παρατηρούμενη συμπεριφορά των σελίδων προχειμένου να παρθούν αποφάσεις την μελλοντική τοποθέτηση τους.

Σε αυτή τη διπλωματική εργασία θα ακολουθηθεί η συλλογιστική πορεία των άρθρων Learning Memory Access Patterns [8] και Kleio: A hybrid Memory Page Scheduler [9]. Σκοπός μας είναι η μελέτη και κατασκευή ενός Χρονοδομολογητή Σελίδων Μνήμης χρησιμοποιώντας Μηχανική Μάθηση, ο οποίος θα επιτυγχάνει καλύτερη απόδοση απο τις σύγχρονες μεθόδους οι οποίες στηρίζονται αποκλειστικά στην ιστορική παρατήρηση προσβάσεων στη μνήμη των εφαρμογών. Θα προσπαθήσουμε να απαντήσουμε σε ερωτήσεις που αφορούν το πως θα πετύχουμε μια αποδοτική λύση, δηλαδή πως θα καταφέρουμε να τοποθετήσουμε όσο πιο ιδανικά γίνεται τα σωστά δεδομένα σε επίπεδο σελίδων (4 KiB [10]) στα σωστά στοιχεία μνήμης. Ενώ ταυτόχρονα αναζητούμε και μια εφικτή λύση, χρησιμοποιώντας περιορισμένους επεξεργαστικούς πόρους για την κατασκευή των μοντέλων μηχανικής μάθησης που θα χρειαστούμε.

## Persistent Memory και Διαχείριση Μνήμης

Η Persistent memory (NVMM) είναι μια σχετικά νεο-αφιχθήσα στον χώρο των υπολογιστικών συστημάτων μη πτητική μνήμη, η οποία προσφέρει διευθυνσιοδότηση σε επίπεδο byte και είναι άμεσα προσπελάσιμη από τον επεξεργαστή όπως η DRAM. Διάφορες τεχνολογίες μπορούν να ενταχθούν στην κατηγορία της Persistent Memory όπως η Phase Change Memory (PCM) [11], η Spin-Transfer Torque RAM [12], και η 3D-XPoint. Η Persistent Memory έχει υψηλή πυκνότητα και χαμηλό κόστος ανά bit, ενώ παράλληλα η καθυστέρηση πρόσβασης (access latency) είναι στην ίδια τάξη μεγέθους με τη DRAM, αισθήτα όμως μεγαλύτερη. Ιδιαίτερο χαρακτηριστικό της Persistent Memory είναι η ασυμμετρία στην κα-θυστέρηση πρόσβασης μεταξύ των αιτημάτων διαβάσματος και γραψίματος. Τα αιτήματα γραψίματος είναι αισθητά πιο αργά και παράλληλα φαίνεται να είναι πεπερασμένα και περιοριστικά για το χρόνο ζωής της μνήμης (finite write endurance). Ακόμα αξιοσημείωτο χαρακτηριστικό της είναι και η μικρή κατανάλωση ενέργειας όταν βρίσκεται σε αδράνεια συγκριτικά με την DRAM, πράγμα που την καθιστά καλή επιλογή για τον σχεδιασμό low-power συστημάτων.

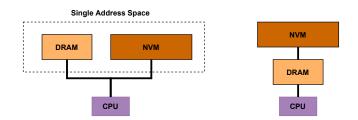

Η μνήμη αυτή βρίσκεται στο ίδιο επίπεδο ιεραρχίας με την DRAM και χρησιμοποιείται είτε ως επέκταση της κύριας μνήμης είτε ως κρυφή μνήμη της DRAM όπως φαίνεται στην εικόνα 2. Εμείς θα ασχοληθούμε μόνο με το πρώτο σενάριο.

Εικόνα 2: NVM σαν επέκταση κύριας μνήμης και σαν κρυφή μνήμη της DRAM

Πρακτικά στο πρώτο σενάριο το σύστημα βλέπει ένα διευρυμένο Address Space το οποίο αποτελείται, σε hardware και από DRAM αλλά και απο NVM. Ωστόσο

αυτά τα δύο είδη μνήμης δεν έχουν τα ίδια τεχνικά χαρακτηριστικά. Για αυτό το λόγο η διαχείριση μνήμης σε αυτά τα συστήματα είναι ιδιαιτέρη, και παρουσίαζει ιδιαίτερη ομοιότητα με τη διαχείριση μνήμης που απαιτείται στα συγχρονα υπολογιστικά συστήματα που διαθέτουν NUMA nodes. Αυτό που επιθυμούμε σε αυτά τα συστήματα είναι κατα τη διάρκεια της εκτέλεσης των προγραμμάτων να μπορούν να παρθούν αποφάσεις για τη μεταφορά Σελίδων Μνήμης απο και προς τα διαφορετικά συστατικά μνήμης, με σκόπο να εκμεταλλευτούμε το γεγονός ότι η DRAM είναι αρκετά ταχύτερη από την NVM ώστε να αυξηθεί η συνολική απόδοση του συστήματος. Αυτό που προτείνεται στη βιβλιογραφία ως λύση μέχρι αυτή τη στιγμή είναι η χρήση ενός Χρονοδρομολογητή ο οποίος θα στηρίζεται αποκλειστικά στο Ιστορικό των σελίδων [13] (History Page Scheduler). Σύμφώνα με αυτήν την προσέγγιση παρατηρείται η συμπεριφορά της σελίδας στο πρόσφατο παρελθόν (π.χ. στα τελευταία 5 δευτερόλεπτα ή στην τελευταία Περίοδο Χρονοδρομολογησης), και με βάση αυτήν την συμπεριφορά αποφασίζεται σε ποιο συστατικό μνήμης πρέπει να τοποθετηθεί η σελίδα. Η υλοποίηση αυτής της προσέγγισης σε επίπεδο συστήματος είναι σχετικά εύκολη και συνήθως χρησιμοποιείται το system call move\_pages(), έτσι ώστε οι σελίδες που ο History Page Scheduler χρίνει ότι θα είναί hot στο μέλλον τοποθετούνται στη DRAM μέχρι αυτή να γεμίσει. Προφανώς για να είναι αποτελεσματικός ο History Page Scheduler θα πρέπει να ελπίζουμε ότι κάθε σελίδα που χαρακτηρίστηκε ως hot με βάση την προηγούμενη Εποχή Χρονοδρομολόγησης θα παραμείνει hot και στο μέλλον.

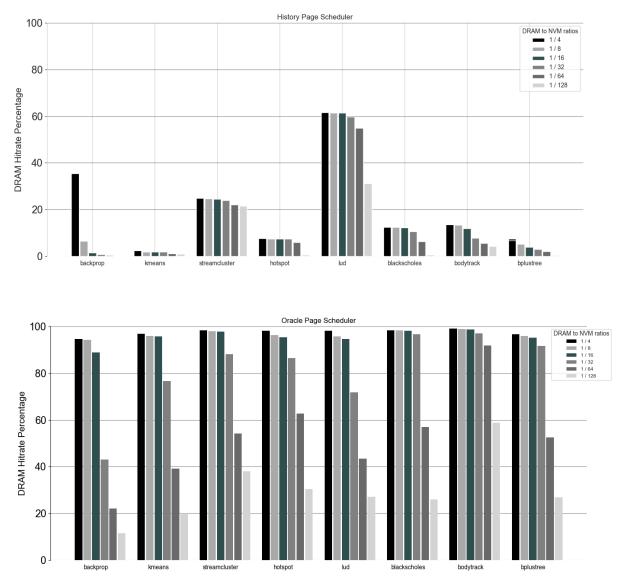

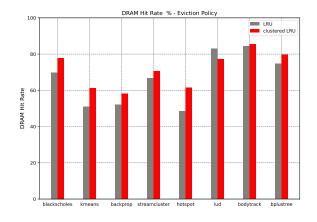

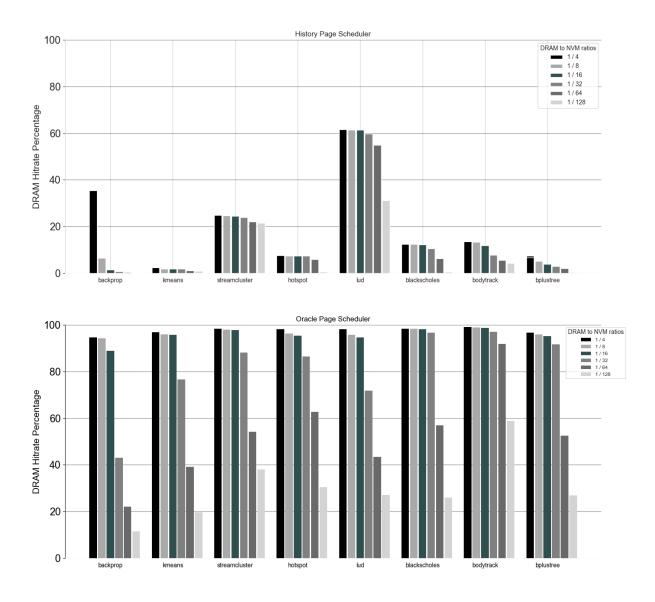

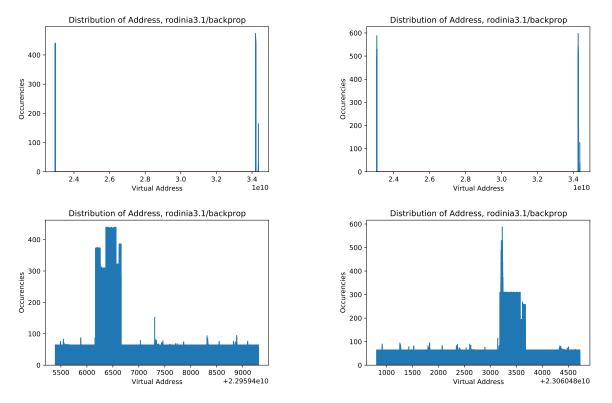

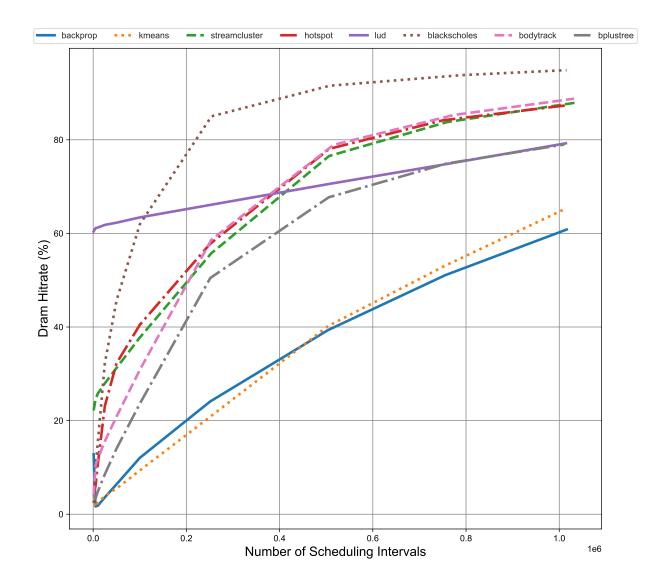

Συγκρίνουμε τον History Page Scheduler με έναν Χρονοδρομολογητή-Μάντη (Oracle Page Scheduler) ο οποίος έχει a priori γνώση για τη συμπεριφορά κάθε σελίδας για διάφορες εφαρμογές για πολλαπλές αναλογίες DRAM:NVM. Πρακτικά ο Χρονοδρομολογητής-Μάντης είναι η μέγιστη επίδοση που μπορεί ρεαλιστικά να επιτευχθεί, πρόκειται για τον ιδανικό Χρονοδρομολογητή Σελίδων. Η σύγκριση έγινε με βάση το DRAM hit-rate, δηλαδή πόσα αιτήματα κατά την εκτέλεση του προγράμματος εξυπηρετήθηκαν απο την DRAM. Προφανώς όσο μεγαλύτερο είναι αυτό το ποσοστό τόσο το καλύτερο. Η σύγκριση φαίνεται στην εικόνα 3 όπου γίνεται ξεκάθαρο το χάσμα στην απόδοση μεταξύ του τι θα μπορούσε ιδανικά να επιτευχθεί από άποψη απόδοσης (κάτω γραφική παράσταση) και τι επιτυγχάνει ο History Page Scheduler (επάνω γραφική παράσταση).

Αυτές οι δυο γραφικές παραστάσεις μας οδηγούν στην ανάγκη να βρούμε τρόπους να γεφυρώσουμε αυτό το χάσμα απόδοσης μεταξύ της απλοϊκής προσέγγισης του History Page Scheduler και του ιδανικού Oracle Page Scheduler. Κύριος λόγος της ανεπαρκούς απόδοσης του πρώτου υποπτευόμαστε ότι ειναι οι λανθασμένες προβλέψεις που κάνει όσον αφορά την εκτίμηση του hotness κάθε σελίδας. Το γεγονός ότι στηρίζεται αποκλειστικά και μόνο σε πρόσφατες πληροφορίες για την συμπεριφορά των σελίδων είναι αυτό που οδηγεί στην ανικανότητα του να εντοπίσει πιο σύνθετα μοτίβα προσβάσεων μνήμης. Στηριζόμενοι σε αυτήν

Εικόνα 3: History and Oracle Page Schedulers DRAM hitrate. Για κάθε εφαρμογή έχει υπολογιστεί το DRAM hitrate για διάφορες αναλογίες DRAM προς NVM. Δηλαδή η συμπεριφόρα αν η DRAM μπορούσε να φιλοξενήσει το x% των συνολικών Σελίδων μνήμης και η NVM τις υπόλοιπες.

την παρατήρηση αλλά και στην αντίστοιχη δουλεία των [8, 9] θα ενσωματώσουμε τεχνικές μηχανικής μάθησης στη διαδικασία της Χρονοδρομολόγησης ώστε να μπορούν να εντοπιστούν οι πιο σύνθετες συμπεριφορές ορισμένων σελίδων που αδυνατεί να εντοπίσει ο History Page Scheduler. Η μηχανική μάθηση μας προσφέρει μηχανισμούς χειρισμού χρονικών δεδομένων, όπου εντοπίζονται εξαρτήσεις τόσο μακροπρόθεσμες όσο και βραχυπρόθεσμες.

## Χρονοδρομολόγηση και Μηχανική Μάθηση

Για το πρόβλημα μας υπάρχουν διάφορες τεχνικές Μηχανικής Μάθησης που θα μπορούσαμε να εξετάσουμε. Στη συγκεκριμένη διπλωματική περιοριστήκαμε στην

εξέταση δύο εναλλακτικών, στην χρήση Ενισχυτικής Μάθησης, και στη χρήση Βαθειών Τεχνητών Νευρωνικών Δίκτύων.

## Ενισχυτικη Μάθηση

Σε μια πρώτη ματιά η ενισχυτική μάθηση, δηλαδή η χρήση ενός agent ο οποίος μαθαίνει μέσα απο τις αποφάσεις που παίρνει σε ένα καλά ορισμένο περιβάλλον ώστε να μεγιστοποιήσει μια συνάρτηση κέρδους μοιάζει να ταιριάζει στο πρόβλημα μας. Θα μπορούσε ως agent να θεωρηθεί ο Χρονοδρομολογητης ο οποίος θα μαθαίνει το μοτίβο προσβάσεων στη μνήμη, θα παίρνει αποφάσεις για την τοποθέτηση των σελίδων με σκοπό να ελαχιστοποιήσει το runtime μέσω της επίτευξης υψηλού DRAM hit-rate. Γρήγορα όμως απορρίψαμε αυτήν την προσέγγιση διότι αποδείχθηκε μη εφαρμόσιμη. Έστω ότι μια εφαρμογή έχει N σελίδες και δύο συστατικά μνήμης, ο Agent-Scheduler πρέπει να διαλέξει ανάμεσα σε  $2^N$  τρόπους να τοποθετήσει αυτές τις σελίδες. Βλέπουμε υπάρχει εκθετική αύξηση του πεδίου το προβλήματος με την αύξηση των σελίδων.

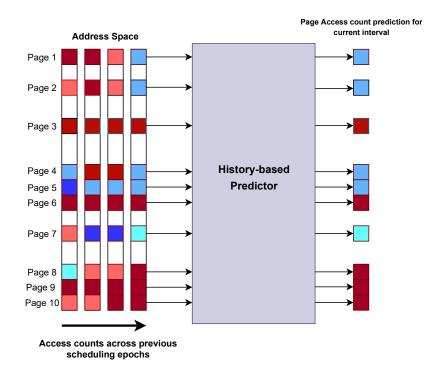

## Επαναληπτικά Νευρωνικά Δίκτυα

Μετά την εγκατάλειψη της ίδεας της Ενισχυτικής Μάθησης προτού καν εφαρμοστεί πρακτικά, προχωρήσαμε στην εξέταση του κατα πόσο θα μπορούσαμε να χρησιμοποιήσουμε Επαναληπτικά Νευρωνικά Δίκτυα για το πρόβλημα μας. Διαπιστώσαμε πως τα Επαναληπτικά Νευρωνικά Δίκτυα (Recurrent Neural Networks - RNNs) λόγω της ικανότητας τους να βρίσκουν μακροχρόνιες και βραχυχρόνιες εξαρτήσεις μεταξύ των δεδομένων αλλά και κυρίως λόγω της γραμμικής αύξησης του πεδίου του προβλήματος (αντί για εκθετική) με την αύξηση των σελίδων μνήμης, είναι κατάλληλα για την επίλυση του προβλήματος μας. Ο χρονοδρομολογητης θα μπορούσε να χρησιμοποιεί ένα Επαναληπτικό Νευρωνικό Δίκτυο ώστε να προβλέπει μελλοντικές προσβάσεις μιας σελίδας μνήμης, χρησιμοποιώντας για την εκπαίδευση του τις προηγούμενες προσβάσεις στη μνήμη. Με βάση τώρα αυτές τις προβλέψεις που αφορούν την μελλοντική συμπεριφορά των σελίδων θα μπορούσαν αυτές να διαταχθούν και να τοποθετηθούν ανάλογα είτε στη DRAM είτε στην NVM.

## Είσοδος Νευρωνικού Δίκτυο

Πέρα απο την επιλογή της τεχνικής που αποφασίσαμε να ακολουθήσουμε, ένα από τα πιο σημαντικά σχεδιαστικά βήματα είναι η επιλογή της εισόδου που θα δοθεί στο Νευρωνικό Δίκτυο. Προφανώς ως είσοδος θα χρησιμοποιηθούν δεδομένα που αφορούν τις προσβάσεις μνήμης μιας Σελίδας, αλλά πως ακριβώς αυτή θα διαμορφωθεί θα επηρεάσει σημαντικά τόσο την ακρίβεια των προβλέψεων όσο και τον χρόνο εκπαίδευσης του Νευρωνικού Δικτύου. Σε αυτό το σημείο εξετάσαμε

δύο επιλογές ως προς την τροποποιήση των δεδομένων εισόδου του Νευρωνικού αλλά και την επιλογή για το ποια θα είναι η ίδια η πρόβλεψη που αυτό καλείται να κάνει.

#### Πρόβλεψη Deltas

Η πρώτη προσέγγιση η οποία είναι και η πρώτη που μας περνά απο το μυαλό είναι να τροφοδοτηθεί ως είσοδος το ίχνος προσβάσεων στη μνήμη (memory access trace) ως έχεί όπως στο Hashemi et al.[8]. Σε αυτήν την προσέγγιση το Νευρωνικό προσπαθεί να κάνει προβλέψεις για το ποιες σελίδες μνήμης θα προσπελαστούν μελλοντικα. Έτσι το πρόβλημα το χειριζόμαστε σαν πρόβλημα κατηγοριοποίησης παρόμοια με αυτά στον τομέα της Επεξεργασίας Φυσικής Γλώσσας (π.χ. κάνε μία πρόβλεψη για την επόμενη λέξη μέσα από ένα λεξικό). Ωστόσο το γεγονός ότι ένα σύγχρονο σύστημα έχει  $2^{64}$  θέσεις μνήμης και επειδή σε αυτά τα προβλήματα το διάνυσμα εξόδου είναι συνήθως ίσο με το μέγεθος του λεξικού μας οδηγεί στη χρήση των deltas αντί για τις πραγματικές τιμές των θέσεων μνήμης. Ως delta τη χρονική στιγμη N ορίζουμε τη διαφορά μεταξύ της διευθύνσεως μνήμης τη χρονική στιγμή N με τη διεύθυνση μνήμης τη στιγμή N - 1.

#### $Delta_N = Addr_N - Addr_{N-1}$

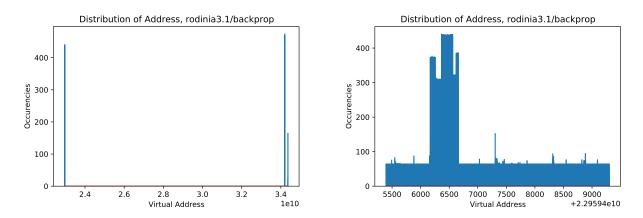

Όμως προέχυψαν αρχετά ουσιαστιχά προβλήματα με αυτήν την προσέγγιση τα οποία την καθιστούν μάλλον ανέφικτη. Αρχικά ακόμα και με τη χρήση των deltas το μέγεθος του ίχνους εισόδου με βάση το οποίο θα εκπαιδευτεί το Νευρωνικό Δίκτυο είναι τεράστιο, φτάνει μέχρι και την τάξη των μερικών δισεκατομμυρίων. Αυτό κάνει την διαδικασία της εκπαίδευσης απαγορευτικά μεγάλη. Ακόμα, το πιο σημαντικό πρόβλημα αυτής της προσέγγισης μάλλον θα πρέπει να θεωρηθεί η χαμηλή αχρίβεια στις προβλέψεις. Το ότι το μέγεθος εξόδου είναι τόσο μεγαλό καθιστά το μοντέλο ανίκανο να πραγματοποιήσει σωστές προβλέψεις. Το άλλο βασικό τεχνικό πρόβλημα αυτής της υλοποιήσης είναι η χαμηλή ακρίβεια προβλέψεων εξαιτίας της κανονικοποιήσης των δεδομένων εισόδου. Είναι σύνηθες προτού τα δεδομένα δωθούν στο μοντέλο για εκπαίδευση αυτά να κανονικοποιούνται. Ωστόσο επειδή μιλάμε για διευθύνσεις μνήμης που μπορούν να πάρουν τιμές απο 0 έως 264 και επειδή συνήθως οι εφαρμογές δεν απλώνονται σε ολόκληρο το address space, η μονή αχρίβεια χινητής υποδιαστολης 32-bit οδηγούν σε σημαντικά δεδομένα να θεωρούνται ως θόρυβος. Με αποτέλεσμα το τελικό μοντελο που έχει εχπαιδευτεί σε αυτά τα δεδομένα να μην μπορεί να πραγματοποιήσει σωστές προβλέψεις. Ενώ αν προσπαθήσουμε να αντιμετωπίσουμε αυτό το πρόβλημα μέσω clustering του address space όπως προτείνεται και στο [8] πρέπει να αντιμετωπίσουμε το πρόβλημα από τη χρήση ASLR (Address Space Layout Randomization). Όταν μαζεουούμε ίχνη προσβάσεων στη μνήμη ακόμα και για τις ίδιες εφαρμογές αυτά έχουν διαφορετικό layout στην virtual memory με αποτέλεσμα το εκπαιδευμένο μοντέλο να μην μπορεί να κάνει ακριβείς προβλέψεις.

#### Πρόβλεψη ανά Σελίδα

Η άλλη προσέγγιση που τελικά επιλέχθηκε είναι η πραγματοποιήση προβλέψεων ανά σελίδα. Αποφεύγουμε το πρόβλημα του ποια σελίδα θα προσπελαστεί (λόγω όλων των δυσκολιών που αναφέρθηκαν). Αντιθέτως διαλέγουμε το Νευρωνικό να απαντάει στην ερώτηση πότε θα προσπελαστεί η σελίδα μνήμης. Θα προβλέπει πόσες φορές θα προσπελαστεί μια σελίδα σε μια περίοδο χρονοδρομολόγησης. Για κάθε σελίδα που μας ενδιαφέρει θα εκπαιδεύουμε ένα Νευρωνικό Δίκτυο στο οποίο θα τροφοδοτούμε την αλληλουχία παρελθοντικών προσβάσεων που αφορούν αυτήν την σελίδα και το Νευρωνικο θα προβλέπει πόσες φορές αυτή η σελίδα θα προσπελαστεί στην επόμενη Εποχή/Περίοδο χρονοδρομολόγησης. Βλέπουμε λοιπόν ότι αυτή η προσέγγιση ταιριάζει με την περιγραφή του προβλήματος μας και πράγματι θα μας δώσει λύση σε αυτά που ζητάμε. Επίσης, με τη χρήση ενός νευρωνικού ανά σελίδα μειώνεται σημαντικά το μέγεθος του πεδίου του προβλήματος με αποτέλεσμα να οδηγηθούμε σε ακριβείς προβλέψεις. Και τέλος, επειδή μπορούμε να διαλέξουμε για ποιες σελίδες θέλουμε να εκπαιδεύσουμε Νευρωνικά Δίκτυα, μπορούμε να μειώσουμε αισθητά το overhead της διαδικασίας της εκπαίδευσης.

## Σχεδίαση

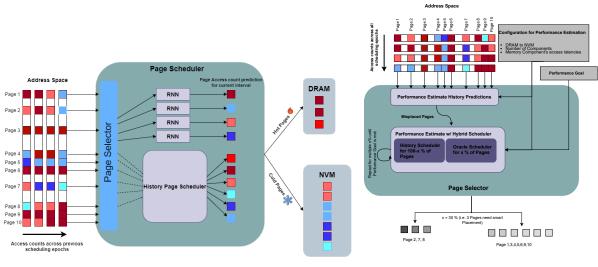

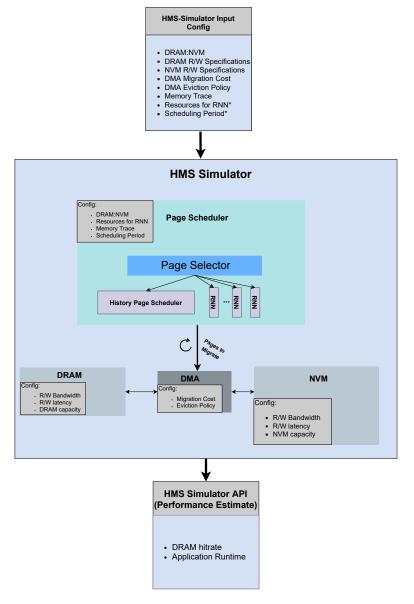

Ο χρονοδρομολογητής σελίδων (σχήμα 4) που σχεδιάσαμε σε κάθε Εποχή Χρονοδρομολόγησης (Scheduling Epoch) θα καλείται να κάνει ορισμένες ενέργειες.

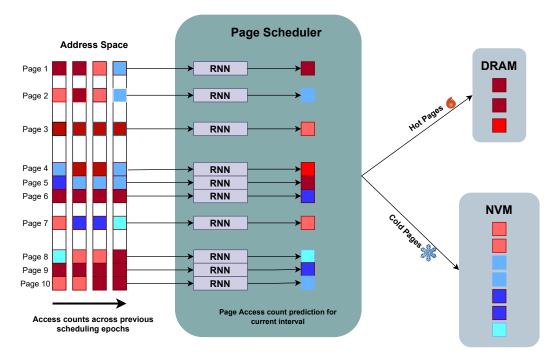

- Με τη χρήση του Επιλογέα Σελίδων (σχήμα 5) θα εντοπίζονται οι σελίδες που επηρεάζουν περισσότερο την απόδοση.

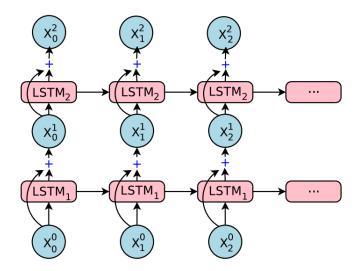

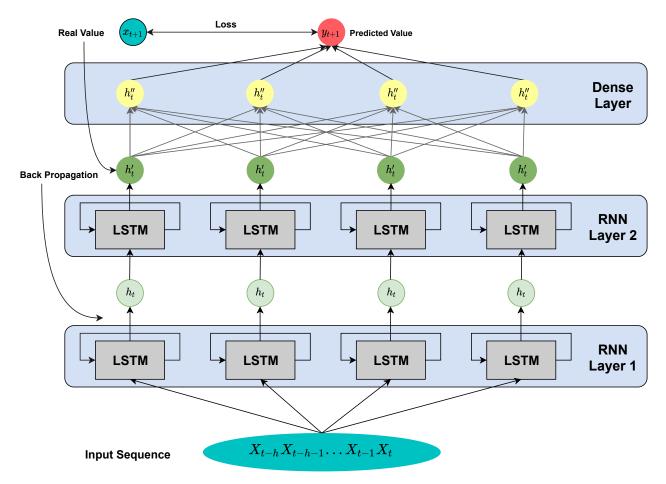

- Έπειτα απο αυτήν την επιλογή οι Σελίδες θα έχουν χωριστεί σε δύο υποσύνολα. Στο πρώτο ανήκουν αυτές που απαιτούν ιδιαίτερη/έξυπνη διαχείριση και επηρεάζουν σημαντικά τη συνολική απόδοση και στο δεύτερο οι υπόλοιπες. Για κάθε σελίδα που ανήκει στο πρώτο υποσύνολο θα εκπαιδευέται ένα Επαναληπτικό Νευρωνικό Δίκτυο (stacked LSTM) το οποίο θα κάνει προβλέψεις για το πόσες φορές θα προσπελαστεί η εκάστοτε Σελίδα στην επόμενη Εποχή. Για τις σελίδες του δεύτερου υποσυνόλου θα χρησιμοποιηθεί ο History Page Scheduler.

- Εφόσον τώρα έχουμε για κάθε σελίδα έχουμε τις εκτιμώμενες φορές που θα προσπελαστεί στην επόμενη περίοδο δρομολόγησης μπορούμε να τις διατάξουμε κατα φθίνουσα σειρά και να τις τοποθετήσουμε στην DRAM μεχρι να γεμίσει και τις υπόλοιπες στην πιο αργή NVM.

Ο χρονοδρομολογητής που σχεδιάσαμε πρακτικά αποτελείται απο τρία βασικά συστατικά. Το πρώτο είναι ο Επιλογέας Σελίδων (εικόνα 5), τα μέσα πρόβλεψης

Ειχόνα 4: Page Scheduler Overview

Εικόνα 5: Page Selector Overview

του αριθμού των μελλοντικών προσπελάσεων των Σελίδων (History Page Scheduler και Επαναληπτικά Νευρωνικά Νευρωνικά Δίκτυα), και η DRAM eviction policy δηλαδή ποιες σελίδες που βρίσκονται στη DRAM θα φύγουν για να μπουν άλλες στη θέση τους.

## Επιλογέας Σελίδων

Ο Επιλογέας Σελίδων (σχ. 5) χρησιμοποιείται για να βρεθεί ποιες σελίδες απαιτούν χρήση Μηχανικής Μάθησης και ποιες όχι. Για να βρεθεί αυτό για κάθε Σελίδα λαμβάνονται υπόψιν τα εξής δύο. Πρώτον πόσες φορές προσπελάστηκε μία Σελίδα γιατί προφανώς οι Σελίδες που προσπελάστηκαν πολλές φορές θα είναι και αυτές που θα επηρεάσουν τη συνολική απόδοση. Δεύτερον για κάθε σελίδα βλέπουμε πόσο καλά μπορεί να τη διαχειριστεί ο History Page Scheduler. Προφανώς αν μία σελίδα μπορεί να τη διαχειριστεί σωστά βρίσκοντας το μοτίβο προσβάσεων της δεν χρειάζεται να εκπαιδευτεί ένα Νευρωνικό Δίκτυο για αυτή τη σελίδα. Αντίθετα αν ο History Page Scheduler τοποθετεί μια σελίδα στην NVM ενώ αυτή ιδανικά θα έπρεπε να βρίσκεται στη DRAM λέμε ότι αυτή η Σελίδα έγινε *misplace* και μάλλον θα πρέπει να αναλάβει τη διαχείριση της ένα RNN. Τα παραπάνω συνοψίζονται στις εξής σχέσεις που προσδιορίζουν ακριβώς το πως λαμβάνει τις αποφάσεις ο Επιλογέας Σελίδων. Για κάθε Σελίδα Χ υπολογίζεται το εξής για τις Περιόδους 0...Ν

$$Profit(x) = \sum_{i=0}^{N} Accesses_i(x) * Misplacement_i(x)$$

(1)

$Misplacement_i(x)$  παίρνει την τιμή 1 αν Σελίδα X τοποθετήθηκε λάθος απο τον History Page Scheduler την περίοδο ι, ενώ αν τοποθετήθηκε σωστά παίρνει την τιμή 0. Και  $Accesses_i(x)$  είναι οι φορές που προσπελάστηκε η Σελίδα X την περίοδο ι και υπολογίζεται ως εξής:

$$Accesses_i(x) = 3 * Writes_i(x) + Reads_i(x)$$

<sup>(2)</sup>

## Μέσα Πρόβλεψης

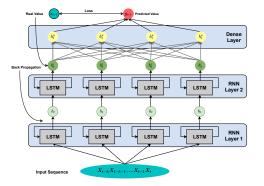

Όπως ειπώθηκε ήδη ως μέσα πρόβλεψης για τον αριθμό προσπελάσεων μια Σελίδας στο άμεσο μέλλον θα χρησιμοποιηθούν για κάποιες Σελίδες Επαναληπτικά Νευρωνικά Δίκτυα και για κάποιες ένας History Page Scheduler. Τη λειτουργία του History Page Scheduler είναι εύκολο να την αντιληφθεί κανείς, καθώς έχει ήδη αναφερθεί. Σε αυτό το σημείο θα δούμε μια αφηρημένη εικόνα για τη δομή των RNNs. Για κάθε σελίδα που επιλέγει ο Επιλογέας Σελίδων θα εκπαιδεύτεται ένα Επαναληπτικό Νευρωνικό Δίτκυο που θα έχει 2 LSTM layers τα οποία ενώνονται με ένα Dense Layer απο το οποίο θα προέρχεται και η μία έξοδος-πρόβλεψη.

## Πολιτική Αδειάσματος DRAM

Όσον αφορά τώρα το Eviction Policy επιλέχθηκε να μην χρησιμοποιηθεί μια απλή ουρά LRU. Εκμεταλλευόμενοι την ιδεά για Address Space Clustering από το Hashemi et al. [8], υλοποιούμε μια ενισχυμένη LRU πολιτική αδειάσματος τηςDRAM, όπου θα λαμβάνεται υπόψιν και το cluster στο οποίο ανήκει κάθε σελίδα. Οπότε σε περιόδους όπου ένα cluster είναι ιδιαίτερα ενεργό, θα αποφεύγεται να αδειάζει η DRAM απο Σελίδες που φέρουν το clusterID του συγκεκρμένου cluster. Αντίθετα θα προτιμούνται να απομακρύνονται απο τη DRAM σελίδες που δεν προσπελάστηκαν πρόσφατα και ανήκουν σε άλλα clusters του Address Space.

## Υλοποίηση

Για την αξιολόγηση της υλοποίησης του Χρονοδρομολογητή που σχεδιάσαμε χρειάστηκε να μαζέψουμε ίχνη προσβάσεων στη μνήμη απο διάφορες εφαρμογές. Οι εφαρμογές που εξετάστηκαν φαίνονται στον πίνακα 1. Για να συλλεχθούν τα ίχνη προσβάσεων στην κύρια μνήμη αυτών των εφαρμογών χρησιμοποιήθηκε το binary instrumentation εργαλείο Intel Pin 3.13-98189 [14]. Αφότου κατασκευάσαμε ένα pintool το οποίο χρησιμοποιεί ένα Cache Simulator που προσομοιώνει ένα πραγματικό σύστημα μπορέσαμε για κάθε εφαρμογή να πάρουμε ένα ίχνος απο Last Level Cache Misses το οποίο είχε την εξής μορφή.

#### Thread ID , Timestamp , Operation , Virtual Address

Για κάθε Virtual Address που υπάρχει στο trace καθε εφαρμογής που συλλέχθηκε μπορούμε να βρούμε σε ποια Σελίδα Μνήμης (4KB) αυτή αντιστοιχεί. Χρησιμοποιώντας τώρα αυτά τα traces θέλουμε να ελέγξουμε πως θα συμπεριφερόταν έναν Σύστημα με διαφορετικά είδη μνήμης σε μια ορισμένη αναλογία αν χρησιμοποιούσε τον Χρονοδρομολογητη που σχεδιάσαμε. Πρακτικά αυτό που θέλουμε να κάνουμε είναι profiling του trace που συλλεχθηκε. Για αυτό το λόγο κατασκευάστηκε ένας Profiler ο οποίος θα παίρνει ως είσοδο το trace και διάφορες

| Workload      | Benchmark Suite | Domain             |

|---------------|-----------------|--------------------|

| streamcluster | PARSEC          | Data Mining        |

| lud           | Rodinia 3.1     | Linear Algebra     |

| backprop      | Rodinia 3.1     | Machine Learning   |

| kmeans        | Rodinia 3.1     | Data Mining        |

| bplutstree    | Rodinia 3.1     | Graph Theory       |

| bodytrack     | PARSEC          | Computer Vision    |

| blackscholes  | PARSEC          | Finance            |

| hotspot       | Rodinia 3.1     | Physics Simulation |

Πίναχας 1: Workloads

άλλες παραμέτρους, όπως π.χ. αναλογία DRAM προς NVM, και θα μπορεί να μας δώσει πληροφορίες για το πως θα ανταποκρινόταν το Προσομοιωμένο συστήμα με τη συγκεκριμένη είσοδο. Θα μπορεί να μας δώσει πληροφορίες για το πόσο πολυ χρησιμοποιήθηκε η DRAM και πόσο η NVM. Μέσα σε αυτόν τον Profiler κατασκευάσαμε και τον δικο μας Χρονοδρομολογητή για να τον αξιολογήσουμε. Ο profiler/simulator αυτός φαίνεται στην εικόνα 7.

Όπως φαίνεται και από την εικόνα ο Χρονοδρομολογητής μας έχει ενσωματωθεί μέσα στο γενικότερο κατασκεύασμα του Profiler. Βασικό χαρακτηριστικό της υλοποιήσης του Χρονοδρομολογητή μας είναι τα Νευρωνικά Δίκτυα. Όπως έχει ήδη ειπωθεί στο Σχεδιασμό κατασκευάσουμε ένα Νευρωνικό ανα-Σελίδα. Η είσοδος αυτού του νευρωνικού συνδυάζει σε αντίθεση με το [9] πληροφορίες που αφορούν τόσο την ίδια τη Σελίδα όσο και κοντινές σε αυτήν σελίδες. Αυτό γίνεται επειδή υπάρχει σημαντική πληροφορία στην τοπικότητα των δεδομένων που θα βοηθήσει στο να πετύχουμε υψηλότερη ακρίβεια στα μοντέλα. Συγκεκριμένα η είσοδος για το Νευρωνικό Δίκτυο μιας Σελίδας Χ προκύπτει απο τον εξής τύπο

$$\text{Input}_{i}(x) = \sum_{j=-4}^{4} \frac{1}{|j+1|} * Accesses_{i}(x+j)$$

(3)

Δηλαδή για την είσοδο του Νευρωνικού αξιοποιούμε πληροφορίες για τους 8 κοντινότερους γείτονες μια σελίδας, ώστε να εκμεταλλευτούμε ότι για ακριβείς

Ειχόνα 6: 2-Layer LSTM Neural Network Overview

προβλέψεις καλο είναι να χρησιμοποιήσουμε πληροφορίες σχετικές και με το Program Counter αλλά και με το Address Delta όπως έδειξαν και στο [8]. Όσον αφορά τώρα την έξοδο του Νευρωνικού, αυτό θα προβλέπει πόσες φορές θα προσπελαστεί η Σελίδα για την οποία έχει εκπαιδευτεί, στην επόμενη περίοδο δρομολόγησης. Στο τεχνικό κομμάτι τώρα το κάθε Νευρωνικό Δίκτυο έχει μορφή σαν αυτή της εικόνας 6. Χρησιμοποιήθηκαν 2 LSTM layers με **256** νευρώνες το κάθε ένα. Το history length ορίστηκε στα **20**, ένω τα 3/4 του συνόλου των δεδομένων χρησιμοποιήθηκε για την εκπαίδευση. Χρησιμοποιήθηκε ο **Adam Optimizer** ενώ το learning rate ορίστηκε στο **0.01**. Η διαδικασία της εκπαίδευσης σταματούσε αν το loss για τα δεδομένα επαλήθευσης δεν άλλαζει για **30** συνεχόμενες εποχές.

Ειχόνα 7: Access Trace Profiler

## Αξιολόγηση

Χρησιμοποιώντας τώρα όσα κατασκευάσαμε προχωρήσαμε στην αξιολόγηση του Χρονοδρομολογητή. Αυτό που θέλουμε να δούμε είναι πόσο καλά κάνει την τοποθέτηση των Σελίδων Μνήμης ο Χρονοδρομολογητής μας για τα ίχνη που συλλέξαμε. Αυτό θα το δούμε με τη χρήση του Profiler που κατασκευάσαμε.

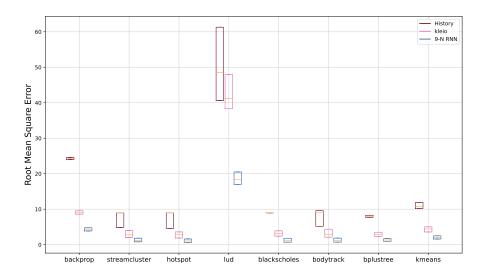

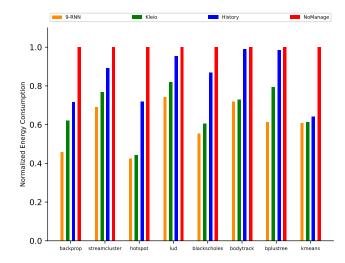

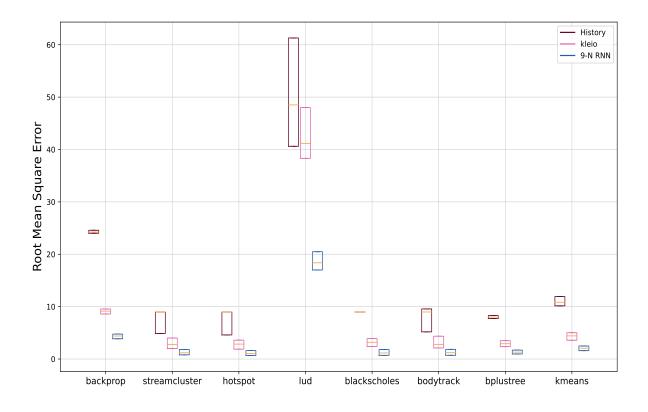

Πρώτο στάδιο της αξιολόγησης είναι να δούμε πόσο καλές είναι οι προβλέψεις που κάνουν τα Νευρωνικά Δίκτυα. Υποθέτουμε ότι οσο καλύτερες είναι οι προβλέψεις σε τοσο καλύτερες τοποθετήσεις Σελίδων θα οδηγηθούμε. Παρατηρώντας την γραφική παράσταση 8 καταλαβαίνουμε ότι η υλοποίηση μας κάνει λιγότερα λάθη στις προβλέψεις (οδηγούμαστε σε χαμηλότερο μέσο Root Mean Square Error) της σε σύγκριση με έναν History-Predictor αλλά και με την υλοποιήση που προτείνεται στο kleio [9].

Eιχόνα 8: Prediction Accuracy of the number of access counts across the scheduling intervals for the selected trained pages. History, kleio's RNNs and our RNNs are used as Access Count Predictors

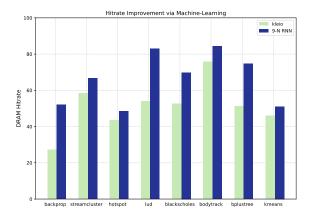

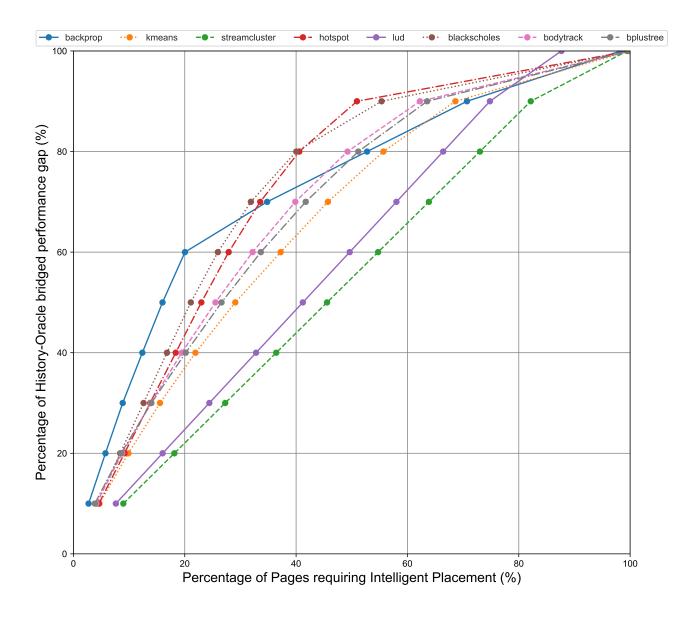

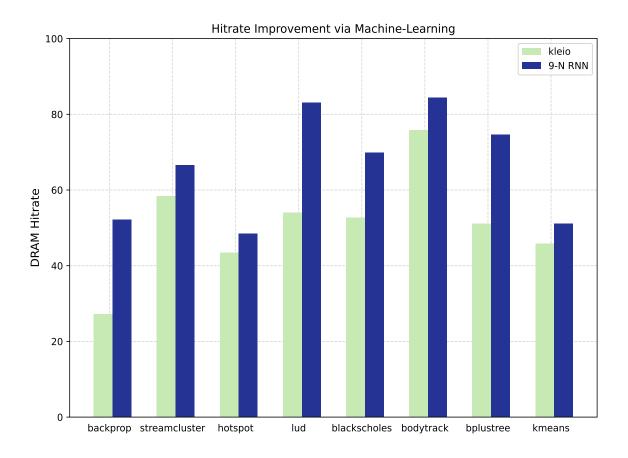

Είδαμε στο πρώτο στάδιο ότι οδηγούμαστε σε χαμηλότερο σφάλμα προβλέψεων. Θέλουμε τώρα να δούμε αν αυτό μεταφράζεται και σε μεγαλύτερη απόδοση του Συστήματος. Για αυτό στο δεύτερο στάδιο της αξιολόγησης προχωρήσαμε στη μελέτη του κατά πόσο γεφυρώνεται το χάσμα μεταξύ του History Page Scheduler και του Oracle Page Scheduler. Μέσω του Profiler συγκρίναμε το DRAM hit-rate του Χρονοδρομολογητή μας με αυτό του kleio (Εικόνα 9 ο Χρονοδρομολογητής είναι ο μπλε και το kleio το πράσινο). Αυτό που παρατηρούμε είναι ότι η υλοποιήση μας φαίνεται να υπερτερεί προσφέροντας μεγαλύτερο DRAM hit-rate δηλαδή περισσότερα αιτήματα εξυπηρετήθηκαν από την DRAM σε σχέση με το kleio. Ακόμα, μπορεί με ασφάλεια να εξαχθεί ως συμπερεσμά ότι το χάσμα μεταξύ

Eιχόνα 9: DRAM hit-rate for kleio and our Scheduler, normalized between 0% for History and 100% for Oracle Page Scheduler, RNNs for 100 pages and 1:8 DRAM to NVM ratio

Eιχόνα 10: DRAM hit-rate for LRU and enhanced-LRU, normalized between 0% for History and 100% for Oracle Page Scheduler, RNNs for 100 pages and 1:8 DRAM to NVM ratio

του History και του Oracle γεφυρώνεται ικανοποιητικά για τις περισσότερες εφαρμογές.

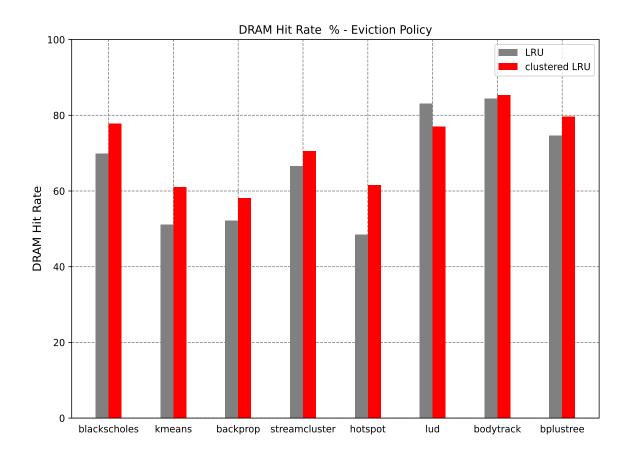

Το τρίτο στάδιο της αξίολογησης μας ήταν η επιλογή της διαφορετικής πολιτικής αδειάσματος (Eviction Policy) της DRAM. Θέλαμε να δούμε αν με το να δίνουμε προτεραιότητα να παραμένουν στη DRAM Σελίδες που ανήκουν σε ενεργά ανά την περίοδο clusters θα οδηγηθούμε σε μεγαλύτερο DRAM hitrate και κατέπέκταση καλύτερο performance. Τα αποτελέσματα της αξιολόγησης όπως φαίνονται απο την εικόνα 10 μας δείχνουν ότι υπάρχει μια αύξηση στην επίδοση για τις περισσότερες εφαρμογές, ωστόσο η πολυπλοκότητα της διαδικασίας του Address Clustering ίσως αντισταθμίζει το όποιο πλεονέκτημα (σε DRAM hitrate) μπορούμε να πάρουμε από αυτήν την σχεδιαστική επιλογή.

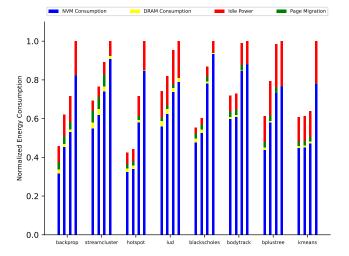

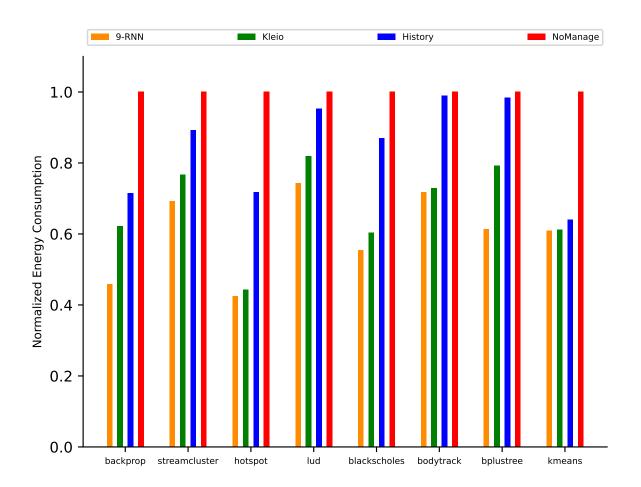

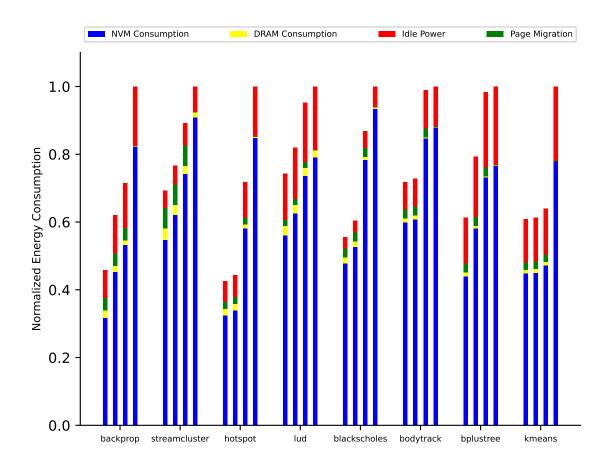

Το τελευταίο χομμάτι της αξιολόγησης αφορά την ενεργειαχή απόδοση της υλοποίησης μας. Χρησιμοποιώντας τα μοντέλα που προτάθηχαν στο [15], συγχρίναμε μεριχά διαφορετιχά Συστήματα. Στο πρώτο δεν χρησιμοποιείται καμία τεχνιχή Χρονοδρομολόγησης σελίδων. Οι σελίδες τοποθετούνται στην αρχή της εχτελέσης της εφαρμογής στα διάφορα συστατιχά μνήμης χαι δεν αλλάζουν θέση μέχρι το πέρας της. Στο δεύτερο χρησιμοποιείται ένας History Page Scheduler, στο τρίτο χρησιμοποείται ένας Δρομολογητής όπως αυτός που περιγράφεται στο kleio [9], ενώ στο τέταρτο χρησιμοποιείται ο δρομολογητής που χατασχευάσαμε εμείς. Να σημειωθεί ότι οι εφαρμογές διαφέρουν η χάθεμια ως προς την αναλογία Read χαι Write. Κάποιες είναι write-intensive, άλλες είναι read-intensive, ενώ άλλες είναι ισορροπημένες. Επίσης πρέπει να σημειωθεί ότι επειδή η μελέτη μας έγινε για ίχνη μιχρού memory footprint η χατανάλωση ενέργειας από τη μνήμη θα επηρεαστεί χυρίως από τα NVM Read/Write operations χαι όχι τόσο από την ενέργεια αδρανειας της DRAM. Αυτό προχύπτει επειδή ο όρος IdlePower =  $451 * \frac{mW}{GB} * T$  για μιχρές τιμές memory footprint είναι συγχρίσιμος ή μιχρότερος

Ειχόνα 11: Energy Comparison between No-Manage, History, Kleio and Our Scheduler

Εικόνα 12: Energy Consumption details for No-Manage, History, Kleio and Our Scheduler

με τον όρο που αφορά τα NVM operations  $(E_{NVM} = 418.6 * W + 80.41 * R)$ , όπου W,R ο συνολικός αριθμός των Writes και Reads αντίστοιχα.

Παρατηρώντας την εικ. 11 όπου συγκρίνονται αυτά τα 4 Συστήματα καταλαβαίνουμε ότι η υλοποιήση μας οδηγεί σχεδόν σε όλες τις περιπτώσεις σε χαμηλότερη κατανάλωση ενέργειας. Αρκετά κοντά στην υλοποιήση μας είναι και ο Χρονοδρομολογητής του kleio, ενώ βλέπουμε οτι ο History Page Scheduler στις περισσότερες εφαρμογές έχει κατανάλωση ενέργειας κοντά σε αυτή του NoManage, δηλαδή του συστήματος που δεν φέρει δρομολογητή. Εξηγήσεις για το πως επιτεύχθηκαν οι μειώσεις στην ενέργεια μπορούν να αντληθούν απο την εικ. 12 όπου όπως περιμέναμε με την αύξηση του DRAM hitrate (και την ταυτόχρονη μειωση των operations που διεκπεραιώνει η NVM), οδηγηθηκαμε σε μικρότερη κατανάλωση ενέργειας από την NVM, ενώ σημαντικό είναι και το γεγονός ότι η ενέργεια που καταναλώνεται για να μεταφερθούν οι Σελίδες μεταξύ NVM και DRAM (Migration Cost) φαίνεται να μην εκτοξεύουν τη συνολική καταναλισκόμενη ενέργεια. Δηλαδή τα ωφέλη που αποκομοίζουμε από τη διαδικασία του Migration δεν αντισταθμίζονται απο το ενεργειακό κόστος που υπεισέρχεται με αυτό.

## Σύνοψη και Μελλοντική Δουλειά

Τα δεδομένα των εφαρμογών συνεχώς αυξάνονται, ενώ το μοτίβο προσβάσεων στη μνήμη γίνεται όλο και πιο σύνθετο. Οι παραδοσιακές τεχνολογίες μνήμης δεν μπορούν να ανταπεξέλθουν σε αυτήν την αύξηση για αυτό νέες τεχνολογίες ενσωματώνονται στα υπολογιστικά συστήματα για να επιτευχθούν οι απαραίτητες αυξήσεις στην επίδοση. Έτσι έχει δημιουργηθεί μια ετερογένεια στα συστήματα μνήμης. Φαίνεται πως υπάρχει ένα χάσμα μεταξύ του σύγχρονου τρόπου χειρισμού της διαχείρισης των πόρων στα συστήματα που φέρουν ετερογενείς μνήμες, και του τι θα μπορούσε να επιτευχθεί ιδανικά. Αυτό το χάσμα προσπαθήσαμε να γεφυρώσουμε σε αυτή τη διπλωματική χρησιμοποιώντας τεχνικές Μηχανικής Μάθησης.

Προτείναμε την κατασκευή ενός Χρονοδρομολογητή Σελίδων Μνήμης ο οποίος θα μπορεί να εντοπίσει ένα μιχρό υποσύνολο σελίδων το οποίο αν το διαχειριστούμε με τη χρήση μηχανικής μάθησης αντι για μία συμβατική reactive προσέγγιση, θα οδηγηθούμε σε αυξημένες επιδόσεις των εφαρμογών. Για κάθε μια από αυτες τις σελίδες θα εκπαιδευτεί ένα Νευρωνικο Δίκτυο το οποίο θα μαθαίνει το μοτίβο πρόσβασης μνήμης της σελίδας. Για τις σελίδες που δεν ανήχουν σε αυτό το υποσύνολο θα χρησιμοποιείται η reactive προσέγγιση ενός History Page Scheduler. Έτσι είδαμε ότι το χάσμα που θέλαμε να γεφυρώσουμε πράγματι σε αρκετές περιπτώσεις γεφυρώθηκε σε ποσοστό 70% και ότι η κατανάλωση ενέργειας μειώνεται σημαντικά. Ενώ ακόμα παρατηρήσαμε ότι η πρόταση να χρησιμοποιηθεί μια ενισχυμένη πολιτική αδειάσματος της DRAM με τη χρήση της τεχνικής του clustering οδήγησε σε 10% κατα μέσο όρο αύξηση του DRAM hitrate σε σύγκριση με μια συμβατική LRU πολιτική. Σαν μελλοντική δουλειά προτείνουμε την επέκταση της μελέτης του Χρονοδρομολογητη για Huge Pages (2 MB) αντί για τις συνηθισμένες σελίδες μεγέθους 4 (KB). Ακόμα θα μπορούσε κανείς να προσπαθήσει να επεκτείνει αυτή τη δουλειά μελετώντας data objects μίας εφαρμογής, και κατα πόσο θα μπορούσαμε να εκμεταλλευτούμε τις σελίδες που ανήκουν στο ίδιο data object. Ακόμα ένα μονοπάτι σκέψης για μελλοντική μελέτη θα μπορούσε να είναι η χρήση τεχνικών μηχανικής μάθησης για διαχείριση μονάδων αποθήκευσης.

# Chapter 1

## Introduction

There seems to be a constantly increasing trend of introducing machine-learning based solutions in almost every single domain of human activities. Machine learning has been a key contributor to achieving innovations in a wide spectrum of applications ranging from simple commercial products to more complex medical applications. This wide spectrum of applications and the incredible ability of Machine Intelligence to model many traditionally complex problems seem to be the primary drivers of the growth spurt observed in the Artificial intelligence field. At the same time, the progress observed in the Computer Architecture field tends to stop following the exponential growth pattern described by Moore's law, and the performance gap between CPU and Memory Units does not seem to stop growing any time soon. These two trends, the Machine Intelligence advancements and these persistent problems in Computer Architecture, push towards a synergistic utilization of methods and techniques, in such a manner that Machine Intelligence and Computer Architecture design will mutually assist each other.

#### Thesis Topic

This thesis is solely dedicated to the use of Machine Intelligence, specifically the utilization of Neural Networks, in an attempt to provide improvements upon Page Scheduling techniques. We will focus primarily on hybrid memory systems, meaning modern computer systems that are comprised of both conventional DRAM and Persistent Memory components.

It is well established that modern systems are frequently designed using heterogeneous memory components. These memories are mainly used for one of two reasons. They are leveraged for either extending the capacity of main memory or for caching purposes. A system comprising of heterogeneous memory components comes with some natural trade-offs. Typically memory components which are deeper in the memory hierarchy (further from the Computing Unit) have higher storing capacity albeit at larger latency and reduced bandwidth. In this thesis we will restrict ourselves to only working with systems that leverage the Persistent Memory for extending the main memory capacity. An important artifact of not only those systems but heterogeneous memory systems in general is addressing the limitations of increased latency and decreased bandwidth. In our case, we are mainly interested in designing an efficient pagescheduler in one HMS scenario. A page scheduler is the memory management layer of operating and runtime systems. It is responsible for the page migration across heterogeneous memory components. A well designed page scheduler insures that pages that are frequently accessed (*hot pages*) are readily available on the high performing memory modules of our system (DRAM), whereas the least important pages, those that are rarely accessed (*cold pages*) remain on the slower Persistent Memory. The use of the page scheduler module we are trying to construct is depicted in figure 1.1.

Figure 1.1: Page Scheduler tiering hot and cold pages to improve performance of and application.

#### Motivation

Many researchers have tried to address the challenge of tiering application pages and placing them into the memory components of a system accordingly. This is an undeniably intricate task, since the complex combination of access pattern of application pages and the runtime parameters of the application (input size, strong/weak scaling etc.) should be taken into consideration. Many researchers have considered solutions whose implementation can be integrated in the hardware-, compiler-, Operating system-, and runtime-level [1, 2, 3, 4, 5, 6, 7]. There are a lot of similarities among these approaches. One of them is that they rely exclusively on historic information about page accesses. Specifically, the state-of-the-art in system level dynamic page management solution for Heterogeneous Memory Systems utilize the immediate observed behavior to make decisions on the best future page placement. However, as we can imagine and will prove later on this thesis, this naive policy is far from ideal when it comes to capturing the complex access pattern of modern applications.

## **Approach and Contributions**

As far as this thesis is concerned, we will follow a similar thought process to the ones presented in the articles *Learning Memory Access Patterns* [8] and *Kleio:* A Hybrid Memory Page Scheduler [9]

The main goal of thesis is to study and construct a Page Scheduler specifically designed for a Hybrid Memory System utilizing Machine Intelligence. Our primary goal is to bridge the performance gap between the current state-of-theart **History** and the ideal but infeasible **Oracle Page Scheduler**<sup>1</sup>. Briefly, our objective is to deliver a near-optimal data placement across the heterogeneous memory components on a page granularity (4KB in Linux based systems). We will try to address important questions concerning how to achieve a both practical and efficient solution. To be specific, we aim to find a solution which reasonably uses computational resources for the typically compute-intensive machine intelligence processing tasks without compromising on the efficacy to properly classify the application pages.

The specific topics we will try to address throughout this thesis are the following

- Performance gap in current solutions. Due to the recent arrival of the Persistent Memory technology, there has not been enough time to develop many algorithms applicable to this specific problem. As a result, the state-of-the-art history-based approach is relatively naive from an algorithmic perspective and does not seem capable of capturing complex access patterns.

- Scheduling interval/epoch selection. Using memory trace collection of several applications, we will try to find out how different scheduling intervals, meaning the amount of time between two data migration events, affect performance. A small scheduling interval means that the page scheduler is frequently called to make decisions about migrating the application pages.

$<sup>^{1}</sup>$ Oracle Page Scheduler uses a priori knowledge of the access pattern of the pages, meaning that it can migrate the indeed *hot pages* into the DRAM until capacity is full

- Machine Intelligence based scheduling. We will soon identify Recurrent Neural Networks as an effective and practical technique for the page scheduling problem, as it is also documented in the articles [8, 9]. We will try to make necessary adaptations to our problem so that we can achieve high accuracy leveraging RNN models, howbeit without neglecting the spatial and computational complexity of our approach. We will find out that training a Recurrent Neural Network on a per-page granularity can lead to high accuracy and significant performance improvements even when applied to a relatively small subset of application pages.

- Page Scheduler design. We design a Page scheduler after taking into consideration several performance metrics. The page-scheduler's approach will combine both the state-of-the-art history-based policy and Machine Intelligence, implemented using RNNs and more specifically LSTMs. We will try to quantify the performance improvements achieved, using a range of workloads from popular suites such as *Rodinia 3.1* [16] and *PARSEC* [17]. We will evaluate our Page-Scheduler compared to the current state-of-the-art implementations found in modern Hybrid Memory systems. Evaluation will revolve around both actual performance and energy consumption.

## Thesis Overview

This thesis is organized in 8 chapters. In the second chapter we briefly summarize existing work related to our research. In the third chapter an informational background concerning Non-volatile Memory and Page Migration in modern Computer Systems is provided. The fourth chapter is dedicated to explaining briefly several types, techniques and use cases of Neural Networks and then we focus mainly on how Recurrent Neural Networks can be leveraged to provide solutions for our problem. In the fifth chapter, a detailed description of the implemented Page Scheduler is laid out, after outlining the important performance metrics that should be considered. In the sixth chapter there are the details when it comes to basic ideas, tools and design choices made concerning the actual implementation of the Page Scheduler. The seventh chapter is solely dedicated to presenting the results of the simulation and its performance evaluation. Finally, before conclusion is drawn, in the eighth chapter we clearly portray the contribution of this thesis and propose future research ideas.

## Chapter 2

## **Related Work**

Over the last years, a considerable amount of research has been carried out in order to address the resource management challenges present in Hybrid Memory Systems, and an array of interdisciplinary approaches have been employed for that purpose; many with noteworthy success. In this chapter, we summarize the recent advances in various aspects of hybrid memory management and we reference systems that use Machine Learning for the purpose of resource management.

#### Hardware Solutions

In this section, we reference memory management solutions in hybrid memory systems that are implemented by custom specialized hardware.

The authors of [18] introduce custom counters to monitor data accesses and enable threshold based data migration triggers. In addition, custom memory controller hardware is also proposed to enable support for page migration in non-volatile memories [19]. In [20], authors design a clustered architecture, which transparently manages hybrid memories configured in a combination of cache and flat organization, that outperforms prior work.

Apart from the purely hardware-level solutions a lot of researchers propose specialized hardware that assist existing software-level solutions by reducing critical resource overheads. A lot of operating system-level solutions [21, 22, 19] are suggesting hardware-assisted page hotness tracking.

#### Software Solutions

In this section, we summarize recent work revolving around the resource management of hybrid memory systems whose implementation is software based and spans either on Application Middleware or Operating System -level. Obviously, the amount of Software oriented work conducted is much more extensive due to the fact that actual Hybrid Memory Systems have reached the market just recently.

Starting on the top of the stack, inside applications themselves, recent work optimizes the algorithmic design to perform more efficiently over the underlying hardware. The authors of [23] direct data placement for conjugate gradient, Fast Fourier Transform (FFT) and LU decomposition of a matrix by utilizing algorithm features and structures and common numerical operations. In addition, a lot of solutions proposed in recent work [24, 2, 7] highly suggest the development of custom data allocations APIs, that require application source code modifications, to improve not only the initial but the dynamic data placement of user-identified critical regions as well.

As far as the recent contributions at the user library-level are concerned, the most significant is probably Memkind [25]. It is a user extensible heap manager that can be leveraged by middleware solutions to improve performance over System with heterogeneous memory components. Various middleware-level solutions [2, 24] rely on application profiling of data access behaviors. Data tiering is optimized based on data movement cost models. Finally, Piccoli *et.* al [26] propose compiler analyses and code generation methods to migrate pages and improve data locality.

To conclude, operating system-level solutions rely on page access information available on kernel's page tables. This way, frequently accessed pages are identified and then are periodically migrated. These solutions create significant resource overheads, and often seem impractical. However, these overheads could be potentially reduced through hardware-assisted solutions. Most System-level solutions leverage existing NUMA-based page migration support or extend the NUMA-based data balancing policy [21, 19, 9, 27]. Another approach is the one proposed by the authors of [28], where a user interface, a user space library and a kernel space service is introduced to accelerate page migrations across heterogeneous memories.

#### Machine Learning Solutions

In this section we describe some of the machine intelligence approaches used in the system's community, focusing either on other relevant problems or just other aspects of data management.

There has been a lot of research regarding the usage of RNNs in the system software stack or in hardware. First, it was popularized by Hashemi *et. al* [8], which had a huge impact on the introduction of Machine Learning into the Computer Architecture field. Hashemi *et. al* [8] proposed leveraging Recurrent Neural Networks for the purpose of memory prefetching. The authors of [29] utilize Recurrent Neural Network to learn I/O block level access patterns in order to optimize the performance of flash storage usage. The usage of RNNs have also been explored in Supercomputing environments. They are deployed in order to predict node failures and make decisions about timely migrating tasks on live nodes [30]. Finally, this thesis is heavily influenced by *kleio* [9] which pioneered the idea of utilizing Machine Learning to improve resource management in Hybrid Memory Systems. *Kleio* utilized Recurrent Neural Networks to timely migrate pages in Hybrid Memory Systems. Unlike *Kleio*, we deploy and train RNNs differently utilizing information that is essential for achieving high prediction accuracy and extend some of the Page Scheduling components to provide performance enhancements.

## Chapter 3

# Persistent Memory & Memory Management

Before engaging on the topic of efficient page migration across heterogeneous memory components in modern computer systems, there are several essential terms and concepts that should be carefully defined. This chapter provides an introductory overview of hardware and software technologies. We start by presenting the characteristics of non-volatile hardware, with primary focus on the Persistent memory module developed by Intel (Intel Optane Persistent Memory Module). Then we present a few concepts concerning general memory paging and page movement across different memory components on system level. This chapter concludes with the demonstration of several implementation challenges and difficulties that should be definitely be taken into consideration.

#### **Persistent Memory**

Typically, modern computer systems are design for a strict bifurcation of devices into memory and storage devices

Storage devices offer the highest capacity and lowest cost-per-bit for persistent storage. They are frequently implemented as block devices and thus cannot be accessed by CPU using Load/Store instructions. As a consequence storage devices are too slow for direct access and data has to be buffered into the main memory to accelerate application execution. A common technique in this context is page caching. The goal of page caching is to minimize data access to slower secondary storage devices by storing recently used pages in unused main memory. Whenever data from secondary storage is requested, the operating system first checks whether the requisite data is in the page cache. If that is not the case, the page containing the requested data has to be read from the slower storage device and is added to the page cache afterwards. When modifying data residing in the page cache, the whole memory page is marked as dirty. Periodically, all dirty marked pages are written back to the disk. Therefore, small changes create a large I/O overhead as the whole page has to be written back to the secondary storage. For reference, the typical linux page is 4 KiB [10].

Memory on the other hand, is directly accessible by the CPU, but has smaller capacity and is more expensive that storage. Moreover, it only provides volatile storage, which means that data stored in memory is lost in the event of a power outage or a system crash.

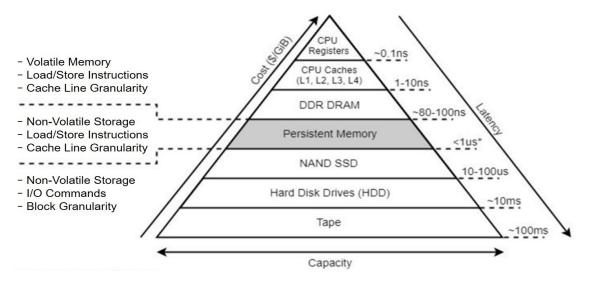

Non-volatile main memory (NVMM) aims to bridge the gap between memory and storage by offering fast, persistent, byte-addressable memory. Various technologies can be considered as persistent memory hardware, such as Phase Change Memory (PCM) [11], Spin-Transfer Torque RAM (STT-RAM) [12], and 3D XPoint. All of them have in common that they offer a high density and low cost-per-bit while also being byte-addressable and achieving latency close to DRAM. The updated storage hierarchy, which now includes persistent memory is depicted in the following figure

Figure 3.1: Pyramid of storage hierarchy with focus on latency capacity and cost. Persistent Memory closes the gap between Non-Volatile Memory and Volatile Memory.

The first scalable commercially available non-volatile memory hardware is Intel Optane DC Persistent Memory Module, which is based on the aforementioned 3D XPoint technology. We refer to it as DCPMM on the throughout the remainder of this chapter. The modules are available in three different capacities : 128GB, 256GB and 512GB per module.

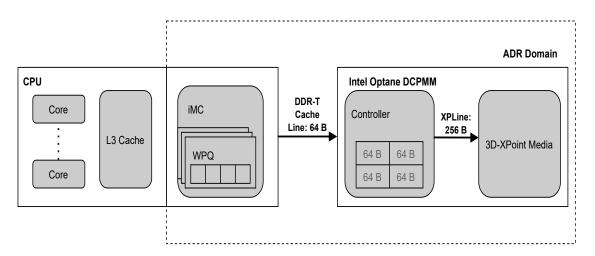

Like conventional memory, DCPMMs are directly connected to the CPU's integrated Memory Controller (iMC) via the memory bus. A single iMC can support up to three DCPMMs. Hence, one processor can employ up to six DCPMMs across its two iMCs. The iMC is located inside the asynchronous DRAM Refresh Domain (ADR), which guarantees that data reaching this domain will survive a power failure. Internally, the iMC maintains read and write

pending queues for each DCPMM, ensuring that data is flushed to media on power failure. It should be emphasized that the ADR does not include the processor's caches. Sotres are consequently only persistent once they reach the iMC [31]. However, there is ongoing research in the area of enhanced ADR (eADR), which also includes the CPU caches [32].

To communicate with the DCPMM, the iMC uses a proprietary DDR-T protocol [33], which has a lot in common with the DDR4 standard but has been adapted to the peculiarities of non-volatile applications. Just like DDR4 (with ECC), the interface for DDR-T uses a 72-bit data bus and transfers data in cache line (64B) granularity between iMC and DCPMM [34]. Starting with Cascade Lake processor family, Intel added CPU support for the DDR-T protocol and consequently for DCPMM. Therefore, DCPMM support is not available on prior Intel CPU generations.

The DCPMM itself contains an onboard controller that coordinates the accesses to the 3D Xpoint media by performing wear-leveling and bad-block management. As the physical media access granularity of 3D Xpoint is 256B (XPLine) [31], the controller includes a small write-combining buffer in the size of 256B, coalescing adjacent 64B DDR-T writes into larger 256B media writes. As a result, the optimal access size for DCPMM is 256B [?, 34]. The communication between the iMC and DCPMM is depicted in the following figure.

Figure 3.2: Communication Structure between CPU and DCPMM.

Latency and bandwidth are key memory technology parameters. Yang et. al [31] demonstrate in their evaluation of the DCPMM that the average read latency is two to three times higher than DRAM. Since both DRAM and DCPMM use the iMC to commit data to media, they perform similarly in terms of write latency [31]. Regarding the performance characteristics of a single Intel DCPMM DIMM, Intel specifies the sequential bandwidth for reads with 7.6 GB/s and for writes with 2.3 GB/s. As for the random bandwidth, Intel quan-

tifies the bandwidth with 2.4 GB/s for reads and 0.5 GB/s for writes. Several publications verify these numbers as well [31, 34].

When looking at the performance numbers, two things stand out: First the random bandwidth which is significantly lower compared to sequential bandwidth. Second, the performance of read and write operations is asymmetrical, with writes being the slower of the two. From this, it can be deduced that data structures with primarily random writes and a high write amplification should be avoided when working with DCPMMs. Before DCPMM became available commercially researchers used emulation to validate and test their non-volatile memory applications. These emulations often inject latency to data accesses and limit the overall bandwidth. However, the previously mentioned empirical analysis by Yang et al [31] indicates that these emulations have failed to reflect the distinctive properties of DCPMM. Characteristics like the internal 256B granularity and the asymmetrical performance of read/write operations were not incorparated into the prior emulations, resulting in less meaningful insights.

The DCPMM has two memory modes: Memory Mode and App Direct Mode [35]. In Memory Mode, the hardware acts as a larger volatile main memory. In this mode, DCPMM is transparent to the operating system and applications. To hide the longer latency and lower bandwidth, DRAM is frequently used as L4 Cache.

In App direct mode the DCPMM is directly exposed as non-volatile memory device separated from DRAM. For the operating system, the DCPMM and the DRAM appear as individual entities. Applications can now use the nonvolatile memory either as an accelerated block device (Storage over App Direct Mode) or access it directly using CPU instructions on memory-mapped files (App Direct Mode).

In this thesis, we will solely use DCPMM in the first mode, the memory mode without focusing on its persistent capabilities.

### Page Migration

Before diving into our scenario of interest, it would be really beneficial to obtain information about the techniques used in problems similar to ours. Therefore, we will first describe the Page Migration process in general Non-Uniform Memory Access (NUMA) systems and then move on to the more specific Heterogeneous Memory Systems comprised of both DRAM and NVM modules. When we refer to Page Migration, we mean the movement of the physical location of pages between nodes in a system while the process is running. This means that the virtual addresses of the executing process do not change. However, the system rearranges the physical location of those pages.

#### Page Migration across NUMA-nodes

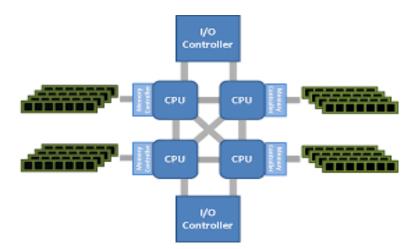

Non-uniform memory access (NUMA) is a computer memory design used in multiprocessing, where the memory access time depends on the memory location relative to the processor. Under NUMA, a processor can access its own local memory faster than non-local memory (memory local to another processor or memory shared between processors). The benefits of NUMA are limited to particular workloads, notably on servers where the data is often associated strongly with certain tasks or users. An example of NUMA-System is depicted in the following figure.

Figure 3.3: Architecture of NUMA system with 4 CPU nodes

NUMA Systems have been prevalent in the High Performance Computing field for many years. Most servers' architecture is NUMA based due to the overall speed increase and general performance improvements NUMA provides. However, the fact that every CPU node has different memory access latency depending on if the requisite data resides in local or remote memory module, entails several design challenges. As it is fairly obvious, an application will generally perform best when the threads of its processes are accessing memory on the same NUMA node as the threads are scheduled. Therefore, there is a need for *load balancing* across NUMA nodes. There are two ways that we can achieve the desired load balancing. We can either move tasks (which can be threads or processes) closer to the memory they are accessing, or we can move application data to memory closer to the tasks that reference it. Hence, we understand that in modern NUMA systems page migration across NUMA nodes is a fundamental aspect of achieving high performance.

Load balancing in NUMA systems occurs on the system level and is handled by the kernel. The most common implementation of load balancing consists of the following three steps :

- A task scanner periodically scans a portion of a task's address space and marks the memory to force a page fault <sup>1</sup> when the data is next accessed.

- The next access to the data will result in a NUMA Hinting Fault. Based on this fault, the data can be migrated to a memory node associated with the task accessing the memory.

- To keep a task, the CPU it is using and the memory it is accessing together, the scheduler groups tasks that share data.

The unmapping of data and page fault handling incurs overhead. However, commonly the overhead will be offset by threads accessing data associated with the CPU.

#### Page Migration in Hybrid Memory Systems

There is a clear similarity between NUMA systems and our field of interest, the Hybrid Memory Systems. Page migration in NUMA systems takes place in order to minimize the amount of Page Accesses of CPU-node to remote higher latency Memory modules. On the same note, in hybrid memory systems pages are migrated from the slower NVM to DRAM and vice versa in order to achieve a reduced average runtime latency. However there is a distinctive difference between the two, that forces us to think of different more intelligent solutions when it comes to the Hybrid Memory System (HMS) scenario.

A considerable amount of research concerning load balancing in NUMA systems revolves around moving threads or processes closer to the memory they are trying to access [36, 37]. However, in the HMS scenario, this approach is fundamentally inapplicable. Both Persistent Memory and DRAM have the same relative location to the CPU. The only load balancing technique left to exploit is the migration of pages across NVM and DRAM.

Following what is currently predominantly used in NUMA systems, most state-of-the-art Page Migration policies proposed by researchers rely on the use of historic information alone [13]. The page behavior is observed, and according to this immediate behavior a decision is being made on the best future page placement. The implementation of this policy on System-level is pretty straightforward, and this is probably the key reason that contributed to its popularity. A History-Page scheduler would periodically migrate pages, probably using the move\_pages()<sup>2</sup> system call, such that those that are hot in the current scheduling epoch/interval, are allocated to DRAM until capacity is

$<sup>^1\</sup>mathrm{A}$  page fault occurs when a program attempts to access a block of memory that is not stored in the physical memory, or RAM.

$<sup>^{2}</sup>$ move\_pages - move individual pages of a process to another node

full. Of course, for this solution to be considered efficient we hope that these hot pages will remain hot in the next scheduling interval as well.

We compare the History Page scheduler implementation with an Oracle page scheduler, which uses a priori knowledge to periodically migrate application pages such that those that are indeed highly accessed, in the next scheduling epoch are placed in DRAM until capacity is full (Fig. 3.4). We observe that the there is a significant gap in the obtained versus the attainable application performance.

The main metric used to assess the performance of those two is the DRAM hitrate percentage. In other words, using several workloads (that will be thoroughly described later on) we measured how many main memory requests are going to be served by DRAM if a System utilizes a History Page Scheduler or an Oracle Page Scheduler. We used several DRAM to NVM ratios to assess the performance each time. We tested each workload in 8 different HMS scenarios (Table 3.1) in order to gain insight about how close or far is the performance (DRAM hit-rate) obtained by a History Page Scheduler and an Oracle Page scheduler. This examination was necessary. If we found out that the performance gap between the History Scheduler and the Oracular was insignificant, there would not be a need to come up with new Page Scheduling proposals.

For instance, we used the backprop workload and examined this application's behavior in case it is executed in the following simulated Hybrid Memory Systems:

| Page Scheduler | DRAM:NVM                                               |

|----------------|--------------------------------------------------------|

| History        | 1:4 i.e. only $1/4$ of memory footprint fits in DRAM   |

| Oracle         | 1:4 i.e. only $1/4$ of memory footprint fits in DRAM   |

| History        | 1:8 i.e. only $1/8$ of memory footprint fits in DRAM   |

| Oracle         | 1:8 i.e. only $1/8$ of memory footprint fits in DRAM   |

| History        | 1:16 i.e. only 1/16 of memory footprint fits in DRAM   |

| Oracle         | 1:16 i.e. only 1/16 of memory footprint fits in DRAM   |

| History        | 1:32 i.e. only $1/32$ of memory footprint fits in DRAM |

| Oracle         | 1:32 i.e. only $1/32$ of memory footprint fits in DRAM |

| History        | 1:64 i.e. only $1/64$ of memory footprint fits in DRAM |

| Oracle         | 1:64 i.e. only 1/64 of memory footprint fits in DRAM   |

#### Table 3.1

Obviously we expected performance drops (lower DRAM hitrate) as DRAM to NVM ratio decreases even for an Oracle Page Scheduler, due to the fact that not many applications pages fit in DRAM at a given time. An important point is also clearly illustrated. There are workloads that historic information is enough to achieve an acceptable data placement across the different memory modules. However, in most cases a Page scheduler based solely on historic in-

Figure 3.4: History and Oracle Page Schedulers DRAM hitrate for different workloads across variable DRAM to NVM ratios

formation is limited in the performance opportunities they can provide running on Hybrid Memory Systems. It is obvious that the gap between what a historic page scheduler achieves versus what is actually attainable is quite significant (Even 80-90% in some workloads). Constructing a scheduler that performs exactly as the oracle is of course unrealistic. A more realistic solution would likely require augmenting the state-of-the-art scheduler with more intelligent, predictive mechanisms.

#### Machine Intelligence based solution

As we mentioned above, it is clear that the immediately observed memory access behavior is not sufficient to capture the necessary information that allows correct future behavior predictions for making clever placement decisions. Yet, we suspect that a larger window of accesses would probably allow the ability to capture historic information (long term access) while also leveraging recent accesses (short term access) for effective data placement.

There are a few design possibilities when it comes to augmenting the current state-of-the-art history page scheduler. For instance, we can use simple methods as Markov chains for handling the temporal aspect. Markov chains are among the most important stochastic processes. They are stochastic processes for which the description of the present state fully captures all the information that could influence the future evolution of the process. This approach is followed in this paper [38]. Another approach would be to utilize advanced techniques of machine intelligence. Machine intelligence provides mechanisms to handle temporal data, capturing both short and long term data dependencies. It seems to be a good fit to our problem, since there is a lot of ongoing research around techniques in Reinforcement Learning and Deep Neural network field, that would allows us to capture page access patterns.

### Page Migration Challenges

Before designing and implementing a Page Scheduler, it is of utmost importance to highlight briefly the challenges that make the construction of an oracular one intricate. After taking into consideration the challenges and the difficulties, it would be much easier to conceive and evaluate a realistic technique of migrating pages.

#### Implementation Overhead

The most common techniques that are currently used in the context of migrating pages across memory components, are relatively easy to implement but are somewhat restricted when it comes to making accurate predictions. On the other hand, more enhanced techniques would require a considerable amount of metadata. These enhanced techniques are often based on Machine Learning models which can either reside in memory, or they can be implemented on-chip. Either way, using machine intelligence for achieving higher prediction accuracy comes with the cost of occupying a substantial chunk of our system's resources. Apart from that, a machine intelligence and generally a more complex scheduling approach would require some extra processing cycles, since inferring prediction models, in most cases, require some data processing, and thus the time and processing resources needed are probably non trivial.

#### Data Retrieval

An efficient and fully functioning Page Scheduler in Hybrid Memory Systems requires the acquisition and storage of essential data. In most cases, the Last Level Cache (LLC) Misses are processed and utilized to make design decisions. However, collecting data concerning LLC Misses is not trivial. Heretofore there is not hardware support to retrieve that data. There are a few approaches that researchers seem to take when the acquisition of such data is needed.

A relatively simple approach is to utilize the Page Table Entry Protection and Status bits.

| Function                                       |

|------------------------------------------------|

| Page is resident in memory and not swapped out |

| Page is resident but not accessible            |

| Set if the page may be written to              |

| Set if the page is accessible from user space  |

| Set if the page is written to                  |

| Set if the page is accessed                    |

|                                                |

Table 3.2: Page Table Entry Protection and Status Bits.

Using a polling technique on the \_PAGE\_ACCESSED bit allows us to retrieve information about pages that are accessed by an application. Acquiring the data needed using this technique would require to periodically check the PTE status bit for the whole address space of a process, which is obviously unrealistic and incurs substantial overhead. This technique could be more lightweight, if used only for just a fraction of the address space, with the obvious consistency compromises that this entails. Apart from that, the other key problem with this technique is that the system's cache structure is not taken into consideration. Data collected this way might prove to be unreliable and unsafe to base our whole design analysis on.

Another approach is to use binary instrumentation. Binary instrumentation is the technique of modifying a binary program. Instructions are added, modified or deleted. By using dynamic code injection techniques, no special preparation or recompilation of the executable is necessary, since the instrumentation code is generated during the execution of the application. Many researchers prefer this approach due to the support of the development community and the high versatility that instrumentation offers. The resource overhead of binary instrumentation is certainly non negligible. However, the consistency of the results that this technique provides and the absence of actual hardware support are certainly the main contributors to binary instrumentation's popularity. The main instrumentation tool used to obtain memory accesses is Intel Pin [39]. We will elaborate on Intel Pin and its use later on this Thesis.

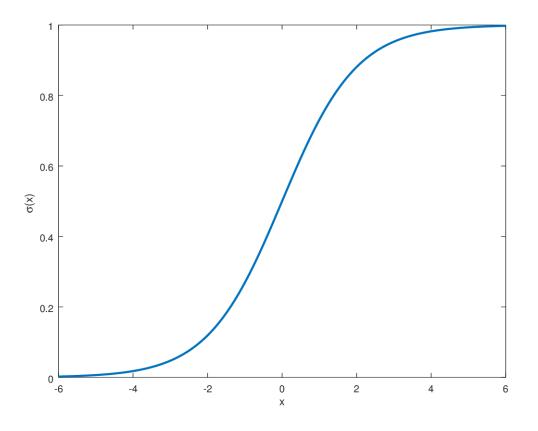

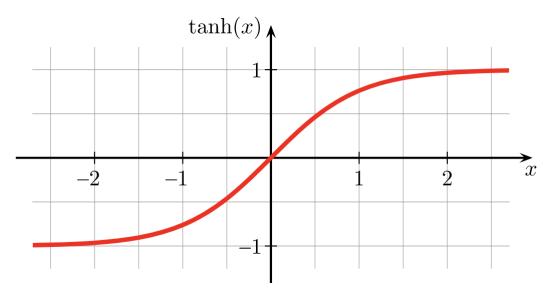

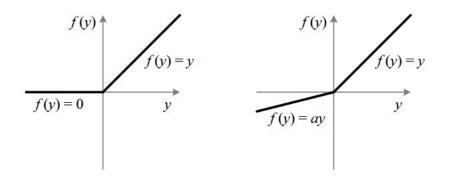

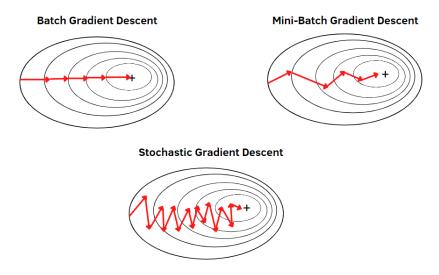

### Page Movement