# Εθνικό Μετσοβίο Πολυτέχνειο

ΣΧΟΛΗ ΗΛΕΚΤΡΟΛΟΓΩΝ ΜΗΧΑΝΙΚΩΝ ΚΑΙ ΜΗΧΑΝΙΚΩΝ ΥΠΟΛΟΓΙΣΤΩΝ ΤΟΜΕΑΣ ΤΕΧΝΟΛΟΓΙΑΣ ΠΛΗΡΟΦΟΡΙΚΗΣ ΚΑΙ ΥΠΟΛΟΓΙΣΤΩΝ ΕΡΓΑΣΤΗΡΙΟ ΜΙΚΡΟΫΠΟΛΟΓΙΣΤΩΝ ΚΑΙ ΨΗΦΙΑΚΩΝ ΣΥΣΤΗΜΑΤΩΝ

# HW/SW Co-Design and Preprocessing for Accelerating Star Trackers on SoC FPGA

$\Delta$ ιπλωματική Εργασία

του

Παπαλουκά Εμμανουήλ

Επιβλέπων: Δημήτριος Σούντρης

Καθηγητής Ε.Μ.Π.

ΕΡΓΑΣΤΗΡΙΟ ΜΙΚΡΟΫΠΟΛΟΓΙΣΤΩΝ ΚΑΙ ΨΗΦΙΑΚΩΝ ΣΥΣΤΗΜΑΤΩΝ  $A\vartheta \acute{\eta} \nu \alpha, \ Io\acute{\upsilon} \lambda \iota \varsigma < 2022$

# HW/SW Co-Design and Preprocessing for Accelerating Star Trackers on SoC FPGA

### $\Delta$ IΠΛΩΜΑΤΙΚΉ ΕΡΓΑΣΙΑ

του

#### Παπαλουκά Εμμανουήλ

Επιβλέπων: Δημήτριος Σούντρης Καθηγητής Ε.Μ.Π.

Εγκρίθηκε από την τριμελή εξεταστική επιτροπή την 30η Ιουνίου 2022.

| (Υπογραφή)                   |

|------------------------------|

|                              |

| © 2022 – All rights reserved |

|                              |

|                              |

Εθνικό Μετσόβιο Πολυτεχνείο Σχολή Ηλεκτρολόγων Μηχανικών και Μηχανικών Υπολογιστών Τομέας Τεχνολογίας Πληροφορικής και Υπολογιστών Εργαστήριο Μικροϋπολογιστών και Ψηφιακών Συστημάτων

Copyright © –All rights reserved Παπαλουκάς Εμμανουήλ, 2022. Με επιφύλαξη παντός δικαιώματος.

Απαγορεύεται η αντιγραφή, αποθήκευση και διανομή της παρούσας εργασίας, εξ ολοκλήρου ή τμήματος αυτής, για εμπορικό σκοπό. Επιτρέπεται η ανατύπωση, αποθήκευση και διανομή για σκοπό μη κερδοσκοπικό, εκπαιδευτικής ή ερευνητικής φύσης, υπό την προϋπόθεση να αναφέρεται η πηγή προέλευσης και να διατηρείται το παρόν μήνυμα. Ερωτήματα που αφορούν τη χρήση της εργασίας για κερδοσκοπικό σκοπό πρέπει να απευθύνονται προς τον συγγραφέα.

# Ευχαριστίες

Θα ήθελα να ευχαριστήσω πρωτίστως τον επιβλέποντα καθηγητή μου κ. Δημήτρη Σούντρη που με εμπιστεύθηκε για την εκπόνηση της διπλωματικής μου εργασίας. Έπειτα, θα ήθελα να ευχαριστήσω ξεχωριστά το μεταδιδακτορικό ερευνητή Γιώργο Λεντάρη και τον υποψήφιο διδάκτορα Βασίλη Λέων για την αδιάλειπτη βοήθεια και την πολύτιμη καθοδήγηση που μου προσέφεραν. Ακόμη, θα ήθελα να ευχαριστήσω ιδιαίτερα το Γιάννη Στρατάκο για τις καίριες συμβουλές και παρεμβάσεις του πάνω σε πιο πρακτικά ζητήματα.

Επιπλέον, ευχαριστώ θερμά το Μάνο Κουμαντάκη και την εταιρεία του Infinite Orbits για την παροχή τεχνογνωσίας, απ΄ την οποία κατέστη δυνατή η ενασχόλησή μου με το συγκεκριμένο θέμα.

Θα ήθελα επιπροσθέτως να ευχαριστήσω την οιχογένειά μου για την υπομονή, την υποστήριξη και την εμπιστοσύνη που μου έδειξε καθόλη τη διάρκεια της φοίτησής μου. Τέλος, θέλω να ευχαριστήσω ιδιαίτερα τους φίλους μου για τις στιγμές που μοιραστήκαμε και για τους οποίους νοιώθω ευγνωμοσύνη για τη δύναμη και το πάθος που μου δίνουν να ακολουθήσω τα όνειρά μου.

# Περίληψη

Οι διαστημικές εφαρμογές απαιτούν ταχεία και ακριβή μέτρηση του προσανατολισμού ενός δορυφόρου, κάτι που μπορεί να επιτευχθεί μόνο με τη χρήση ανιχνευτών αστέρων. Το όργανα αυτά αποτελούνται από ένα ψηφιακό αισθητήρα εικόνας που καταγράφει τον ουρανό, καθώς και από ψηφιακό υλικό το οποίο ανιχνεύει τα αστέρια στην εικόνα και τα αντιστοιχίζει σε γνωστούς αστερισμούς καταλόγου ώστε να προσδιορίσει τη θέση του δορυφόρου στο αδρανειακό σύστημα. Η ανίχνευση αστέρων είναι υψηλής πολυπλοκότητας και απαιτεί μεγάλους χρόνους εκτέλεσης, ιδίως εάν χρησιμοποιούνται συμβατικοί μικροεπεξεργαστές. Συνεπώς, η ανάγκη για ανιχνευτές αστέρων υψηλής απόδοσης οδήγησε στην αυξανόμενη χρήση εμπορικών συσκευών υλικού «από το ράφι» σε διαστημικές εφαρμογές.

Στην παρούσα διπλωματική εργασία αναπτύσσουμε σε ένα ενσωματωμένο σύστημα SoC FPGA τα στάδια προεπεξεργασίας δεδομένων της προγραμματιστικής ροής ενός ανιχνευτή αστέρων τα οποία αφορούν την ομαδοποίηση εικονοστοιχείων για μείωση του όγκου δεδομένων, και την ανίχνευση συστάδων που χρησιμοποιούνται για τον υπολογισμό κεντροειδών. Επιπλέον, υλοποιείται μια λογισμική προσέγγιση που εκτελείται στον επεξεργαστή της πλατφόρμας και συγκρίνεται με το ενσωματωμένο HW/SW σύστημα όσον αφορά την απόδοση. Η αρχιτεκτονική υποστηρίζει την επικοινωνία μεταξύ των PS και PL στοιχείων του SoC μέσω των AMBA ΑΧΙ πρωτοκόλλων, καθώς επίσης και τη δυναμική προσαρμογή του κατωφλίου που χρησιμοποιείται κατά τη συσταδοποίηση ανάλογα με τα επίπεδο θορύβου της εικόνας.

Το σύστημά μας εξετάστηκε με ρεαλιστικές εικόνες που έχουν ληφθεί σε μια αποστολή της NASA και αξιολογείται ως προς την απόδοση, τη χρήση πόρων του FPGA και την κατανάλωση ισχύος. Είναι ικανό για ακριβή ανίχνευση εκατοντάδων συστάδων εντός του πλαισίου της εικόνας επιταχύνοντας την εκτέλεση κατά 60 φορές συγκριτικά με τον ARM επεξεργαστή του SoC FPGA, ενώ εκτιμάται οτι η επιτάχυνση μπορεί να αυξηθεί έως και 108 φορές. Τελικά, η ενσωματωμένη υλοποίηση που συνδυάζει υλικό και λογισμικό είναι ικανή για απόδοση σε πραγματικό χρόνο, καθώς επωφελείται από την αρχιτεκτονική παράλληλης επεξεργασίας του FPGA και τις ειδικά προσαρμοσμένες τεχνικές υλοποίησης.

### Λέξεις Κλειδιά

Ανιχνευτές αστέρων, SoC, Zynq FPGA, Συσταδοποίηση, Ομαδοποίηση, Κατωφλίωση, Συνδυασμός HW/SW, Εφαρμογές Διαστήματος

## Abstract

In space applications it is critical to measure the satellite's orientation fast and precisely, which can be only achieved using star trackers. This setup consists of a digital image sensor that captures images of the sky, as well as hardware that detects stars and maps them to known constellations in order to determine the inertial attitude of the satellite. Star detection is a process of high complexity due to large amounts of image data and thus, it takes significant time to execute, especially when operating on conventional microprocessors. Thus, the need for high performance star trackers leads to the use of Commercial Off-The-Shelf (COTS) FPGAs, which offer great parallelisation opportunities and provide remarkable speedups.

In this thesis, we focus on the implementation of an efficient algorithm for accelerating preprocessing operations of star trackers on COTS SoC FPGAs. More specifically, we develop a HW/SW embedded system for accelerating the preprocessing stages of a star tracker pipeline on Xilinx's Zynq. These stages refer to the image binning that decreases the data volume, and to the detection of clusters from which centroids will be subsequently extracted. The proposed architecture exploits parallelisation at multiple levels via parametric HDL circuit design. The HW/SW co-design integrates the PS and PL parts of Zynq, whose communication is established via AMBA AXI protocols. Our integrated system supports dynamic adjustment to the threshold used in clustering process depending on the noise floor level of the image frame.

The proposed design is tested with real images captured on a NASA mission and is evaluated in terms of performance, resource utilisation and power consumption. A software-oriented approach running on the PS of the SoC is also developed and compared to our HW/SW embedded system. Our proof-of-concept implementation accurately detects hundreds of clusters within the image frame while accelerating the execution, resulting to a speedup of 60x compared to the ARM processor with an estimated increase up to 108x. Hence, this HW/SW co-design achieves real-time performance as it benefits from the FPGA's parallel processing architecture and our custom implementation techniques.

#### Keywords

Star Tracker, SoC, Zynq FPGA, Clustering, Binning, Thresholding, HW/SW Co-Design, Space Applications

# Contents

| $\mathbf{E}_{1}$ | υχαρ  | ιστίες |                                            | 1    |

|------------------|-------|--------|--------------------------------------------|------|

| П                | ερίλι | ηψη    |                                            | 9    |

| $\mathbf{A}$     | bstra | ıct    |                                            | Ę    |

| $\mathbf{C}_{0}$ | onter | nts    |                                            | 7    |

| Li               | st of | Figur  | es                                         | ę    |

| Li               | st of | Table  | 5                                          | 13   |

| <b>E</b> :       | κτετ  | αμένη  | Περίληψη                                   | 15   |

| 1                | Intr  | oducti | ion                                        | 27   |

|                  | 1.1   | Motiv  | ation                                      | . 27 |

|                  | 1.2   | Thesis | s Scope                                    | . 28 |

|                  | 1.3   | Projec | et Objectives                              | . 30 |

|                  | 1.4   | Thesis | S Outline                                  | . 30 |

| <b>2</b>         | Bac   | kgroui | $\operatorname{ad}$                        | 33   |

|                  | 2.1   | Star T | rackers                                    | . 33 |

|                  |       | 2.1.1  | Star Tracker Characteristics               | . 34 |

|                  |       | 2.1.2  | Sub-pixel Accuracy                         | . 35 |

|                  |       | 2.1.3  | Theoretical Background                     | . 36 |

|                  |       | 2.1.4  | Algorithms                                 | . 38 |

|                  |       | 2.1.5  | Commercially Available Star Trackers       | . 39 |

|                  | 2.2   | Relate | ed Work                                    | . 40 |

|                  | 2.3   | Space  | Navigation                                 | . 41 |

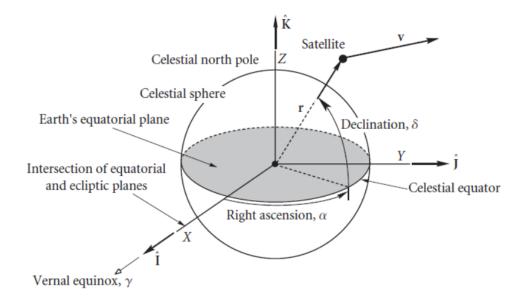

|                  |       | 2.3.1  | Celestial navigation for satellites        | . 41 |

|                  |       | 2.3.2  | Celestial navigation for deep space probes | . 42 |

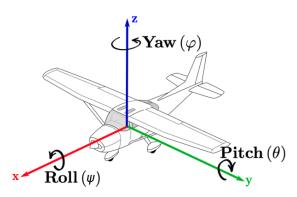

|                  | 2.4   | Rotati | ional Kinematics                           | . 43 |

|                  |       | 2.4.1  | The Earth Centred Inertial (ECI)           | . 43 |

8 Contents

| Bi | Sibliography 105 |               |                                     |      |  |  |

|----|------------------|---------------|-------------------------------------|------|--|--|

| 5  | Con              | clusio        | n and Future Work                   | 101  |  |  |

|    | 4.2              | Result        | s and Analysis on Zynq FPGA         | . 92 |  |  |

|    | 4.1              |               | imental Setup                       |      |  |  |

| 4  | $\mathbf{Exp}$   |               | ntal Evaluation                     | 91   |  |  |

|    |                  | ა.⊿.⊍         | System integration                  | . 00 |  |  |

|    |                  | 3.2.4 $3.2.5$ | Performance-Wise Optimization       |      |  |  |

|    |                  | 3.2.3 $3.2.4$ | Low Level Implementation            |      |  |  |

|    |                  | 3.2.2         | High Level Architecture             |      |  |  |

|    |                  | 3.2.1         | Cluster detection algorithm         |      |  |  |

|    | 3.2              | •             | W Co-design of Clustering           |      |  |  |

|    |                  | 3.1.2         | Low Level Implementation            |      |  |  |

|    |                  | 3.1.1         | High Level Architecture             | . 58 |  |  |

|    | 3.1              | HW/S          | W Co-design of Averaging 2D Binning | . 57 |  |  |

| 3  | Dev              | elopm         | ent on the Zynq SoC FPGA            | 57   |  |  |

|    |                  | 2.5.4         | Design Flow                         | . 54 |  |  |

|    |                  | 2.5.3         | AXI4 Stream                         |      |  |  |

|    |                  | 2.5.2         | AXI4 Lite                           |      |  |  |

|    |                  | 2.5.1         | Xilinx Zynq SoC FPGA Architecture   | . 50 |  |  |

|    | 2.5              | SoC F         | PGA Overview                        | . 48 |  |  |

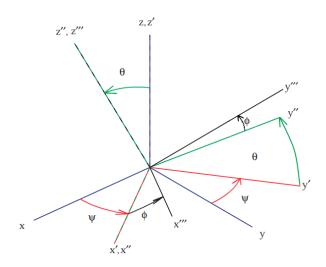

|    |                  | 2.4.3         | Coordinate Transformation           | . 46 |  |  |

|    |                  | 2.4.2         | Euler Angles                        | . 43 |  |  |

|    |                  |               |                                     |      |  |  |

# List of Figures

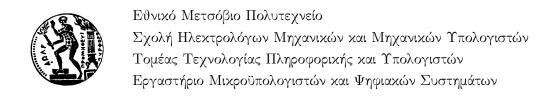

| 1    | $\Delta$ ιαφορετικά επίπεδα ομαδοποίησης εικονοστοιχείων                | 17 |

|------|-------------------------------------------------------------------------|----|

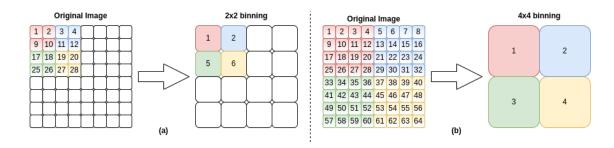

| 2    | Σχεδιαστική απεικόνιση του πυρήνα Ομαδοποίησης Εικονοστοιχείων          | 18 |

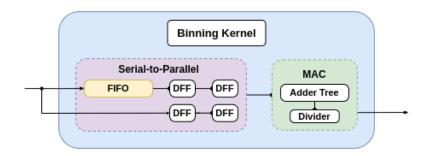

| 3    | Μηχανισμός αναζήτησης ειχονοστοιχείων                                   | 20 |

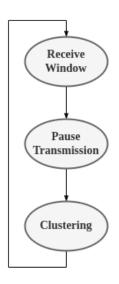

| 4    | $\Delta$ ιάγραμμα ροής για τη λήψη των δεδομένων εικόνας                | 21 |

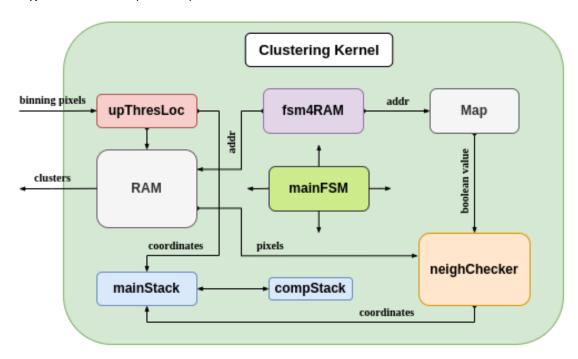

| 5    | Σχεδιαστική αναπαράσταση του πυρήνα Συσταδοποίησης                      | 22 |

| 6    | Αναπαράσταση καταμερισμού διεργασιών                                    | 23 |

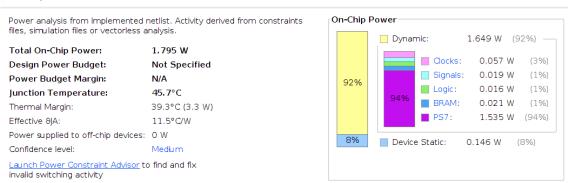

| 7    | Εκτιμώμενη κατανάλωση ισχύος για το ολοκληρωμένο σύστημα                | 25 |

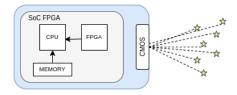

| 1.1  | Block diagram of a typical Star Tracker                                 | 29 |

| 1.2  | System-on-Chip Layout                                                   | 29 |

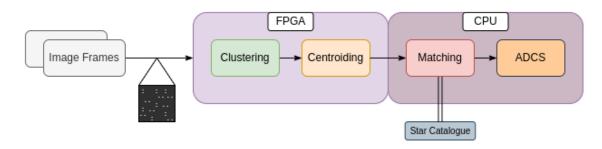

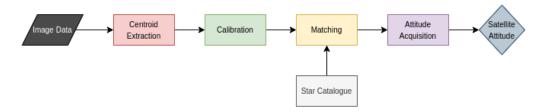

| 1.3  | Process Flow of a Star Tracker                                          | 29 |

| 2.1  | Pointing and rolling accuracy schematic of the star tracker [1]         | 34 |

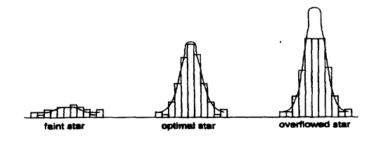

| 2.2  | Different Stars Utilising Hyperacuity technique [2]                     | 36 |

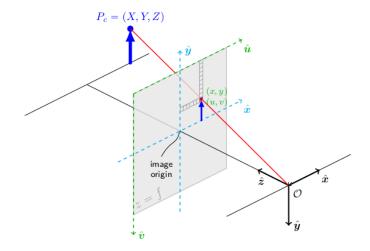

| 2.3  | Image sensor's perspective Projection model [3]                         | 37 |

| 2.4  | High level process flow of an ADCS                                      | 38 |

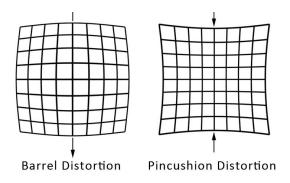

| 2.5  | Types of radial distortion [4]                                          | 39 |

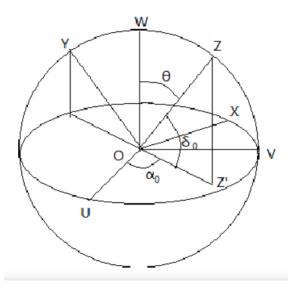

| 2.6  | The Earth-Centred Inertial (ECI) frame [5]                              | 44 |

| 2.7  | Roll-Pitch-Yaw notation for Euler angles [6]                            | 45 |

| 2.8  | Euler Angle Sequence $(3,1,3)$                                          | 45 |

| 2.9  | Coordinate model of a star tracker [7]                                  | 46 |

| 2.10 | Celestial coordinate system to star tracker's coordinate system [7]     | 47 |

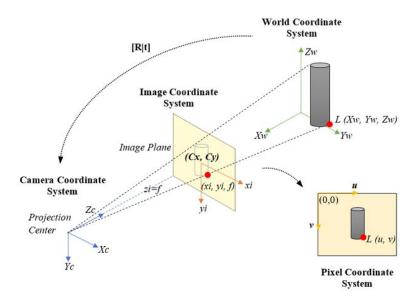

| 2.11 | Pinhole Camera Model: ideal projection of a 3D object on a 2D image [8] | 48 |

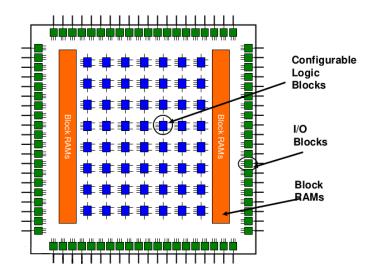

| 2.12 | Field Programmable Gate Array (FPGA) schematic [9]                      | 49 |

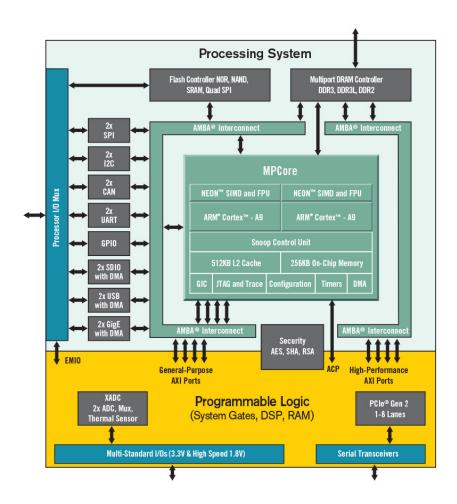

| 2.13 | Xilinx Zynq SoC FPGA Architecture [10]                                  | 50 |

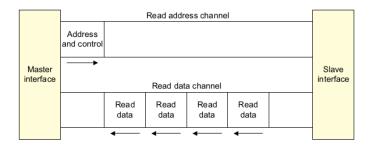

| 2.14 | Channel architecture of reads [11]                                      | 53 |

| 2.15 | Channel architecture of writes [11]                                     | 53 |

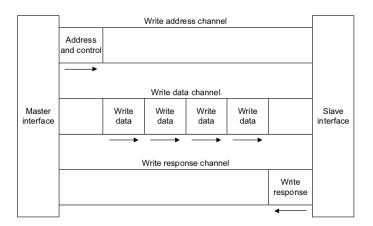

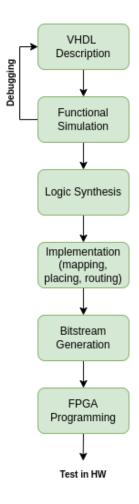

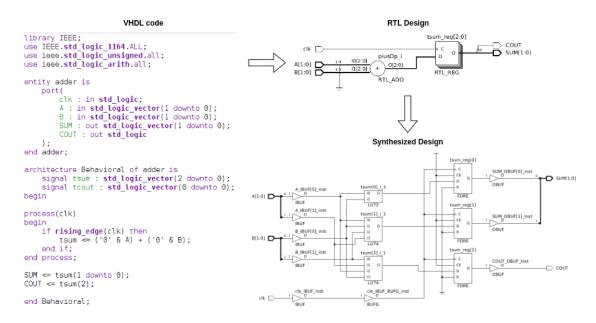

| 2.16 | FPGA Design Flow                                                        | 55 |

| 2.17 | VHDL code to synthesized design conversion                              | 56 |

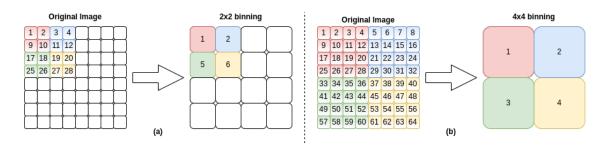

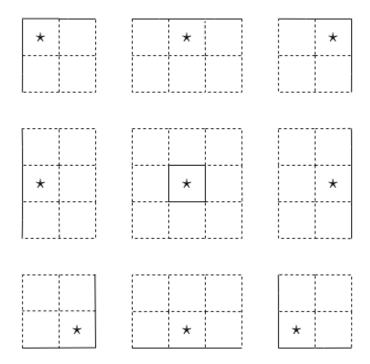

| 3.1  | Different levels of averaging binning                                   | 58 |

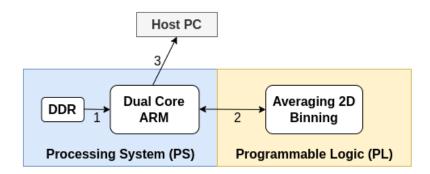

| 3.2  | Processing flow of the integrated system                                | 58 |

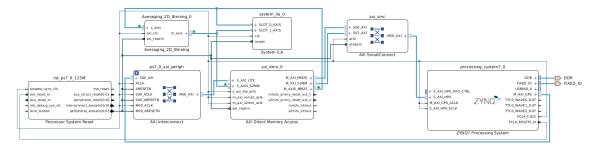

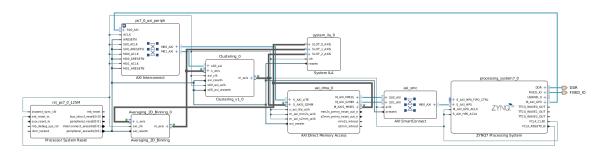

| 3.3  | Block design of the HW/SW integrated system                             | 60 |

10 List of Figures

| 3.4 | Zynq7 Processing System block design                                            | 60         |

|-----|---------------------------------------------------------------------------------|------------|

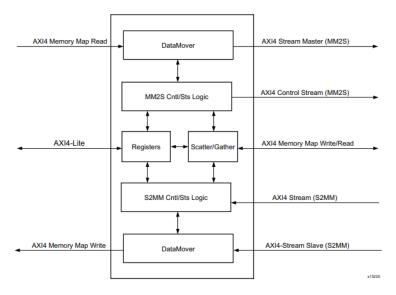

| 3.5 | AXI DMA Block Diagram [12]                                                      | 62         |

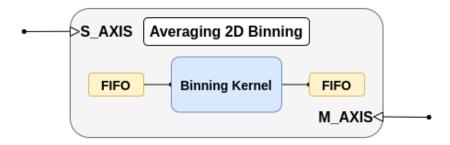

| 3.6 | Averaging 2D Binning block design.                                              | 62         |

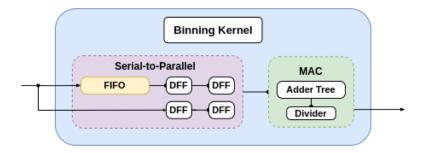

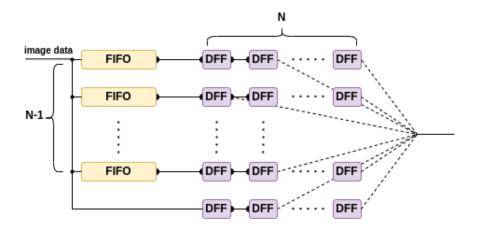

| 3.7 | Block design of the Binning kernel                                              | 63         |

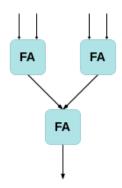

| 3.8 | Adder Tree Structure for $2\times 2$ binning                                    | 64         |

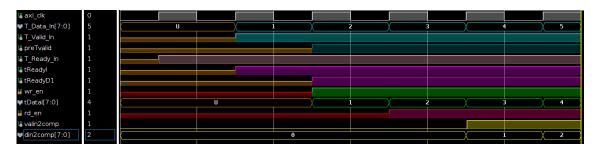

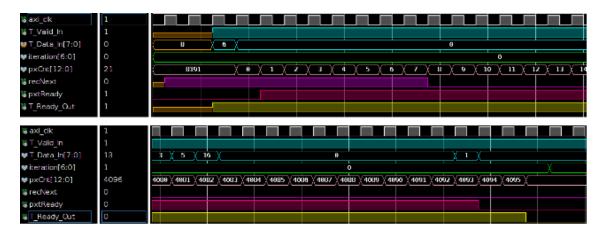

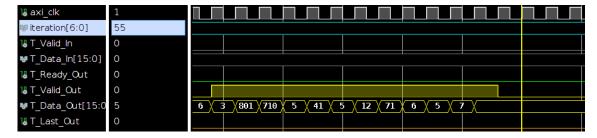

| 3.9 | Behavioural Simulation of the input FIFO buffer handling                        | 65         |

| 3.1 | 0 Behavioural Simulation of the output FIFO buffer handling                     | 66         |

| 3.1 | 1 Serial-to-Parallel block                                                      | 66         |

| 3.1 | 2 Behavioural simulation of Serial-to-Parallel operation                        | 67         |

| 3.1 | 3 Generic block design of Adder Tree                                            | 67         |

| 3.1 | 4 Behavioural simulation of MAC operation                                       | 68         |

| 3.1 | 5 Visualization of light spreading in a defocused star                          | 69         |

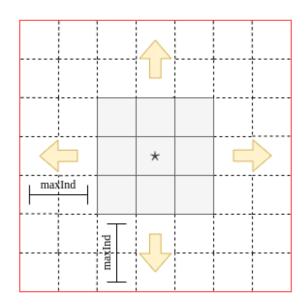

| 3.1 | 6 Configuration of Neighbourhoods of Search                                     | 70         |

| 3.1 | 7 Processing flow of the HW/SW Co-design for Clustering                         | 71         |

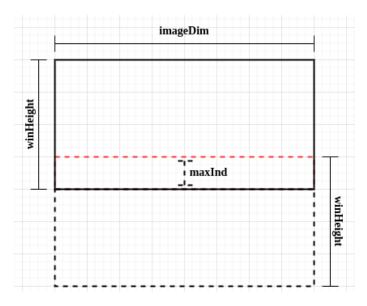

| 3.1 | 8 Image partitioning in sliding windows                                         | 72         |

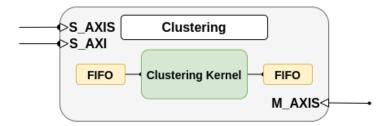

| 3.1 | 9 Clustering block design                                                       | 72         |

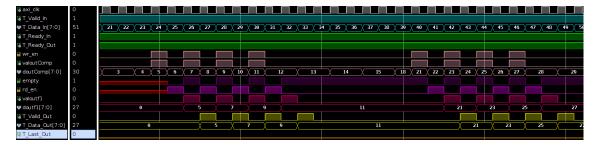

| 3.2 | 20 Data transmission pipeline                                                   | 73         |

| 3.2 | 21 Block design of the Clustering kernel                                        | <b>7</b> 4 |

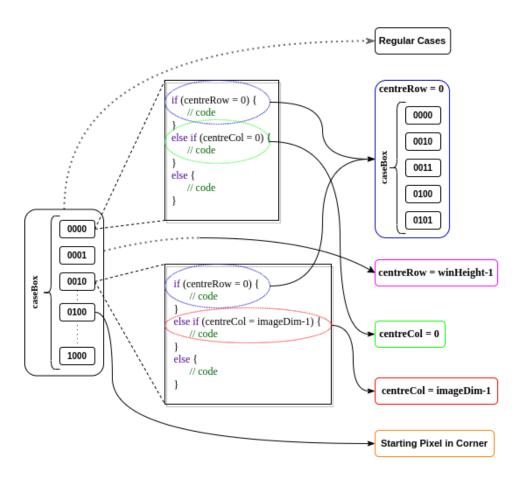

| 3.2 | 22 Illustration of every possible case for reading operation of starting pixels | 75         |

| 3.2 | 23 Determination of Region-of-Interest                                          | 76         |

| 3.2 | 24 Example of the addressing operation                                          | 77         |

| 3.2 | 25 Pipeline of the processing steps handled by mainFSM                          | 78         |

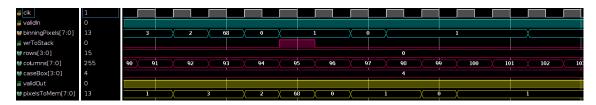

| 3.2 | 26 Behavioural simulation of driving TREADY signal for a $256 \times 256$ image |            |

|     | and winHeight of 16 rows                                                        | 80         |

| 3.2 | Properties Behavioural simulation of upperThresLoc                              | 80         |

| 3.2 | 8 VHDL code of the function that computes the addresses                         | 81         |

| 3.2 | 9 Behavioural simulation of fsm4ram                                             | 81         |

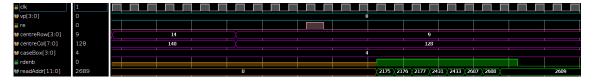

| 3.3 | Behavioural simulation of neighChecker                                          | 82         |

| 3.3 | 31 Illustration of the correlation between the operations performed by fsm4RAM  |            |

|     | and neighChecker blocks                                                         | 83         |

| 3.3 | 32 VHDL code transformation regarding signal overflow                           | 85         |

| 3.3 | 3 Visualization of task partitioning                                            | 87         |

| 3.3 | 4 Illustration of the three individual sub-processes performed by neighChecker  |            |

|     | component                                                                       | 88         |

| 3.3 | 5 Pipeline of the processing stages of the HW/SW Co-design                      | 89         |

| 3.3 | Block design of the HW/SW Co-design                                             | 89         |

|     |                                                                                 |            |

| 4.1 |                                                                                 |            |

| 4.2 | * L J                                                                           |            |

| 4.3 |                                                                                 |            |

| 4.4 | Estimated Power Consumption of Binning component                                | 94         |

List of Figures 11

| 4.5  | Behavioural simulation of an output detected cluster                        | 95 |

|------|-----------------------------------------------------------------------------|----|

| 4.6  | Visualisation of a detected cluster on MATLAB                               | 95 |

| 4.7  | Post execution results as shown in SDK terminal after clustering operation. | 96 |

| 4.8  | Estimated Power Consumption of Clustering component                         | 97 |

| 4.9  | Behavioural simulation of the Binning-Clustering co-design                  | 97 |

| 4.10 | Post execution results as shown in SDK terminal after Preprocessing oper-   |    |

|      | ation                                                                       | 97 |

| 4.11 | Estimated Power Consumption of the Integrated System                        | 98 |

| 4.12 | Analytic overview of the consumed power for each individual block           | 98 |

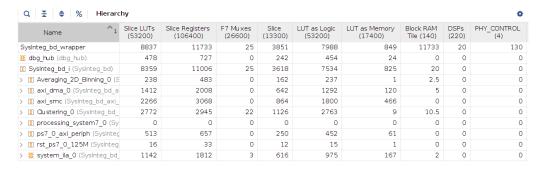

| 4.13 | Hierarchical presentation of the FPGA resource utilisation                  | 99 |

# List of Tables

| 1   | Δυγκριτικός Πινάκας με τις συχνότητες ρολογιού που επέτευχθησαν κατοπίν     |    |

|-----|-----------------------------------------------------------------------------|----|

|     | βελτιστοποιήσεων                                                            | 24 |

| 2   | Σύγχριση μέσων χρόνων εχτέλεσης μεταξύ των δύο προσεγγίσεων για κάθε        |    |

|     | ένα από τα υλοποιημένα στοιχεία                                             | 24 |

| 3   | Χρήση πόρων του FPGA για το ολοκληρωμένο σύστημα                            | 25 |

| 2.1 | Table of commercially available star trackers                               | 39 |

| 3.1 | Table of the achieved clock period per component after optimisation $\dots$ | 88 |

| 4.1 | Comparison of mean execution time between SoC FPGA and ARM CPU              |    |

|     | for Averaging Binning operation                                             | 93 |

| 4.2 | Resource Utilisation of FPGA for Binning implemented design                 | 94 |

| 4.3 | Comparison of mean execution time between SoC FPGA and ARM CPU              |    |

|     | for Clustering operation                                                    | 96 |

| 4.4 | Resource Utilisation of FPGA for Clustering implemented design              | 97 |

| 4.5 | Comparison of mean execution time between SoC FPGA and ARM CPU              |    |

|     | for the Integrated HW/SW Co-design                                          | 98 |

| 4.6 | Resource Utilisation of FPGA for the Integrated System                      | 98 |

# Εκτεταμένη Περίληψη

#### Εισαγωγή

Η παρούσα διπλωματική εργασία διεξήχθη σε συνεργασία με την Infinite Orbits, μια εταιρεία που δραστηριοποιείται στη διαστημική βιομηχανία και παρέχει καινοτόμες υπηρεσίες για δορυφορικά συστήματα. Οι διαστημικές εφαρμογές είναι γενικά ιδιαίτερα απαιτητικές διεργασίες και είναι ζωτικής σημασίας το να ικανοποιούνται συγκεκριμένες προδιαγραφές. Πρέπει να χαρακτηρίζονται από υψηλά επίπεδα αυτονομίας ώστε να ελαχιστοποιούνται οι καθυστερήσεις που εισάγονται από τα κανάλια επικοινωνίας και ελέγχου που βρίσκονται σε περιβάλλον εδάφους. Επιπλέον, τα δορυφορικά συστήματα πρέπει να μπορούν να λειτουργούν αδιαλείπτως και χωρίς προβλήματα ή έστω να είναι σε θέση να τα αντιμετωπίζουν με ασφάλεια και συνεπώς πρέπει να διακατέχονται από ευρωστία. Τέλος, πρέπει να είναι εξαιρετικά γρήγορα ώστε να ανταποκρίνονται άμεσα και να αντιμετωπίζουν ανεπιθύμητες καταστάσεις που μπορούν να οδηγήσουν σε ατυχήματα.

Το όργανο εχείνο που παρέχει τη δυνατότητα ταχείας και υψηλής αχρίβειας μέτρησης για τον προσδιορισμό του προσανατολισμού ενός δορυφορικού συστήματος είναι ο ανιχνευτής αστέρων. Ο ανιχνευτής αστέρων αποτελείται από ένα οπτικό σύστημα και από το ψηφιακό υλικό. Το οπτικό σύστημα περιλαμβάνει ένα ψηφιακό αισθητήρα εικόνας που τραβάει φωτογραφίες του ουρανού οι οποίες χρησιμοποιούνται από το υλικό για τον προσδιορισμό της θέσης του δορυφόρου. Το υλικό περιλαμβάνει κάποιο σύστημα επεξεργασίας που είναι συνήθως κάποιος μικροεπεξεργαστής, ο οποίος πραγματοποιεί τους απαραίτητους υπολογισμούς για να εξάγει χρήσιμες πληροφορίες. Η διαδικασία αυτή αποτελείται από επιμέρους υπολογιστικά στάδια μερικά από τα οποία παρουσιάζονται στα πλαίσια αυτής της διπλωματικής εργασίας. Γενικά, η ανίχνευση αστέρων χαρακτηρίζεται από υψηλή υπολογιστική πολυπλοκότητα η οποία ενισχύεται από το γεγονός οτι απαιτείται επεξεργασία μεγάλου όγκου δεδομένων αποτελώντας έτσι περιοριστικό παράγοντα στην απόδοση του συστήματος, ιδίως εάν η εκτέλεση πραγματοποιείται σε κάποιον συμβατικό μικροεπεξεργαστή.

Τα τελευταία χρόνια, η ανάγκη για αποδόσεις πραγματικού χρόνου έχει στρέψει το ενδιαφέρον σε άλλες εναλλακτικές δημιουργώντας νέες τάσεις στην βιομηχανία του διαστήματος. Πλέον, έχουμε ραγδαία αύξηση χρήσης εμπορικών συσκευευών υλικού «από το ράφι» σε διαστημικές εφαρμογές με την πιο διαδεδομένη από αυτές να είναι τα FPGA, αφού η αγορά παρέχει ήδη ένα μεγάλο εύρος πλατφορμών κατάλληλες για τέτοιου είδους εφαρμογές.

Στα πλαίσια διερεύνησης του πεδίου εφαρμογών των COTS FPGA στο διάστημα με τις

οποίες ασχολείται το Εργαστήριο Μιχροϋπολογιστών & Ψηφιαχών Συστημάτων, διεχπεραιώθηχε η διπλωματική αυτή η οποία πραγματεύεται την ανάπτυξη αλγορίθμων σε ένα ενσωματωμένο σύστημα SoC FPGA οι οποίοι υλοποιούν τα πρώτα στάδια της προγραμματιστικής ροής ενός ανιχνευτή αστέρων. Αυτά τα στάδια αφορούν την προεπεξεργασία δεδομένων και χωρίζονται στις εξής δύο υποδιεργασίες: την ομαδοποίηση των εικονοστοιχείων με σκοπό τη μείωση των διαστάσεων της υπό επεξεργασία εικόνας και την ανίχνευση συστάδων αστεριών εντός του πλαισίου αυτής. Οι εξαγόμενες αυτές συστάδες χρησιμοποιούνται στα επόμενα στάδια για τον υπολογισμό του ύψους του δορυφόρου. Σκοπός είναι να αξιοποιήσουμε τις δυνατότητες της πλατφόρμας του υλικού προτείνοντας μια αρχιτεκτονική που συνδυάζει τόσο το λογισμικό όσο και το υλικό του SoC FPGA.

### Θεωρητικό υπόβραθρο

Οι ανιχτευτές αστέρων χρησιμοποιούνται για τον προσδιορισμό της θέσης ενός διαστημικού σκάφους, επειδή παρέχουν τη μεγαλύτερη ακρίβεια από οποιονδήποτε άλλον αισθητήρα. Προκειμένου να μεγιστοποιηθεί η ακρίβεια της εκτίμησης της θέσης ενός αστεριού, η λάμψη που εκπέμπει αυτό αποκεντράρεται σε μάσκες εικονοστοιχείων μεγέθους από  $3\times3$  έως  $15\times15$  ανάλογα με τα χαρακτηριστικά του αισθητήρα εικόνας. Η εξάπλωση του φωτός που αποτυπώνεται στα εικονοστοιχεία της εικόνας του αισθητήρα περιγράφεται από μαθηματικές συναρτήσεις που ονομάζονται PSF (Point Spread Functions) οι οποίες είναι ουσιαστικά Γκαουσιανές συναρτήσεις. Εν συνεχεία, χρησιμοποιούνται κατάλληλοι αλγόριθμοι αναγνώρισης προτύπων οι οποίοι με την κατάλληλη επεξεργασία των δεδομένων μπορούν να εκτιμήσουν τον προσανατολισμό του συστήματος με ακρίβεια εικονοστοιχείου κάτω από  $1\sigma$ .

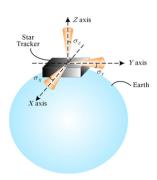

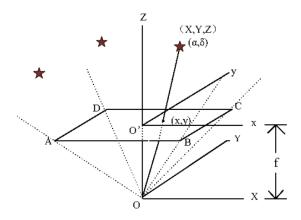

Στη διαστημική πλοήγηση απαιτείται ένα σταθερό σύστημα συντεταγμένων ως σημείο αναφοράς ώστε να υπάρχει συσχέτιση με το αντίστοιχο σύστημα του χινούμενου διαστημικού οχήματος. Το σύστημα που χρησιμοποιείται ονομάζεται Earth Central Inertial (ΕCΙ) και η αρχή των αξόνων του είναι αχριβώς στο χέντρο της Γης, χωρίς να αχολουθεί όμως την χίνησή της. Ο ανιχνευτής αστέρων συσχετίζει το ΕΟΙ με το σύστημα συντεταγμένων του οχήματος που τοποθετείται στο κέντρο μάζας του προκειμένου να εξάγει πληροφορίες σχετικά με τη θέση αυτού. Προχειμένου να γίνει η συσχέτιση της θέσης του ανιχνευόντος αστέρα στο πλαίσιο της εικόνας με την πραγματική του θέση στον ουρανό, απαιτούνται κάποιοι μετασχηματισμοί στα αντίστοιχα συστήματα συντεταγμένων. Αρχικά, οι συντεταγμένες του αστέρα στο ΕCΙ σύστημα πρέπει να μεταφερθούν στο αντίστοιχο σύστημα συντεταγμένων του οπτιχού αισθητήρα. Έπειτα, πρέπει να γίνει η προβολή της θέσης του αστέρα από τον τρισδιάστατο χώρο στο πλαίσιο της δισδιάστατης εικόνας, το οποίο επιτυγχάνεται με τη χρήση του μοντέλου κάμερας pinhole, το οποίο παρέχει μια απλή περιγραφή της σχέσης μεταξύ των τρισδιάστατων συντεταγμένων ενός σημείου και της προβολής του σε μια ιδανικής κάμερας η οποία θεωρείται σημείο αναφοράς. Το τελευταίο βήμα αφορά τη μεταφορά από το σύστημα συντεταγμένων της ειχόνας στο σύστημα συντεταγμένων του ειχονοστοιχείου (Ειχόνα 2.11).

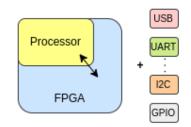

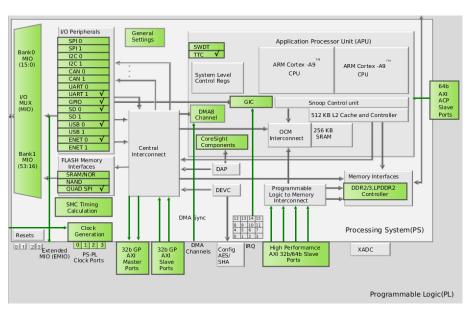

Η παρούσα διπλωματική εργασία επικεντρώνεται στην υλοποίηση ενός αλγορίθμου για ανιχνευτές αστέρων σε μια συσκευή υλικού SoC FPGA αξιοποιώντας τις δυνατότητες που

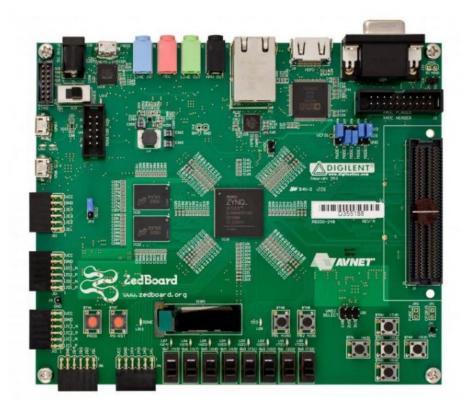

προσφέρει λόγω της ευελιξίας και της απόδοσής της. Οι συσκευές SoC FPGA συνιστούν μια καινοτόμα βελτιωμένη προσέγγιση στο χώρο των πλατφορμών υλικού καθώς περιλαμβάνουν στο ίδιο ολοκληρωμένο chip έναν επεξεργαστή καθώς επίσης και ένα FPGA. Κατά συνέπεια, έχουν μεγαλύτερο βαθμό ολοκλήρωσης, χαμηλότερη ισχύ και υψηλότερο εύρος ζώνης επικοινωνίας μεταξύ του επεξεργαστή και του FPGA. Ως εκ τούτου, τα SoC FPGA συνιστούν μια ιδιαίτερα ανταγωνιστική εναλλακτική προσέγγιση έναντι των συμβατικών μέσων υλικού της αγοράς. Για τις ανάγκες της διπλωματικής αυτής, χρησιμοποιήθηκε η πλακέτα Zedboard της ΑVNET η οποία περιλαμβάνει το σύστημα Xilix Zynq-7020 SoC.

#### Υλοποίηση του στοιχείου για την Ομαδοποίηση Εικονοστοιχείων

Το πρώτο στοιχείο του συνδυαστικού μας συστήματος υλικού/λογισμικού είναι υπεύθυνο για την ομαδοποίηση εικονοστοιχείων σε δισδιάστατη εικόνα. Η τεχνική αυτή είναι ευρέως διαδεδομένη σε εφαρμογές που βασίζονται σε συστήματα οπτικών αισθητήρων και αφορά το συνδυασμό των τιμών γειτονικών εικονοστοιχείων ώστε να σχηματιστεί ένα υπερ-εικονοστοιχείο και να αυξηθεί κατά κάποιον τρόπο το μέγεθος του αισθητήρα εικόνας. Ως εκ τούτου, πετυχαίνουμε την αποτελεσματική αύξηση της ευαισθησίας του εικονοστοιχείου που προκύπτει με κόστος τη μειωμένη χωρική ανάλυση. Επιπλέον, σε εφαρμογές όπου επεξεργάζονται εικόνες μεγάλου μεγέθους είναι πολύ ευεργετική τεχνική για την απόδοση του συστήματος καθώς οι διαστάσεις της εικόνας μειώνονται σημαντικά. Έτσι, όχι μόνο μειώνεται ο χρόνος επεξεργασίας, αλλά και οι απαιτούμενοι πόροι ελαττώνονται σημαντικά.

Σχήμα 1: Διαφορετικά επίπεδα ομαδοποίησης εικονοστοιχείων.

Το συγκεκριμένο μπλοκ που υλοποιήσαμε, λειτουργεί σε περιοχές εικόνας  $2\times2$  ή  $4\times4$  με βηματισμό 2 ή 4 αντίστοιχα και υπολογίζει τη μέση τιμή τους. Λαμβάνοντας υπόψη τις απαιτήσεις του πρότζεκτ, επιλέξαμε να προχωρήσουμε με ομαδοποίηση  $2\times2$  κρίνοντας πως είναι καταλληλότερη επιλογή για τη διατήρηση της ισορροπίας μεταξύ της ανάλυσης της εικόνας και της ευαισθησία της.

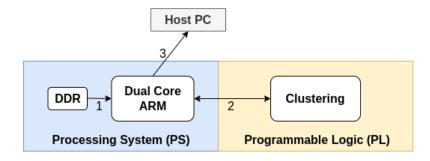

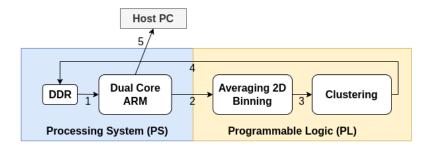

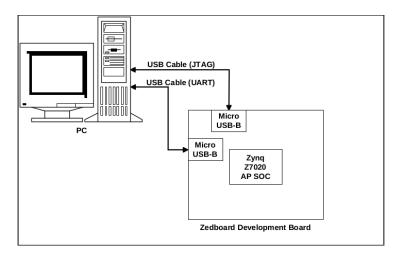

Όπως έχει ήδη αναφερθεί, η προτεινόμενη αρχιτεκτονική του συστήματός μας συνδυάζει τόσο το υλικό (PL) όσο και το λογισμικό (PS) του Zynq SoC FPGA. Για λόγους απλότητας, στην παρούσα εφαρμογή οι εικόνες είναι αποθηκευμένες στο μνήμη της πλατφόρμας, αντί να λαμβάνονται από τον αισθητήρα εικόνας. Και στις δύο περιπτώσεις, ο επεξεργαστής είναι ο διαμεσολαβητής ώστε να προωθούνται τα δεδομένα από τη μνήμη ή την κάμερα στην προγραμματιστική λογική. Ως εκ τούτου, πρέπει να διαμορφωθεί καταλλήλως το σύστημα

ώστε να επιτυγχάνεται η επικοινωνία μεταξύ των δύο διαφορετικών υπο-στοιχείων της πλατφόρμας. Επομένως, το στοιχείο μας έχει διαμορφωθεί ώστε να υποστηρίζει το πρωτόκολλο ΑΧΙ4-Stream ώστε να μπορεί να λαμβάνει έγκυρα δεδομένα από το PS.

Η μονάδα ομαδοποίησης εικονοστοιχείων αποτελείται από δύο βασικά υπο-κυκλώματα. Τα εισερχόμενα εικονοστοιχεία της εικόνας λαμβάνονται σειριακά ακολουθώντας σάρωση τύπου raster, δηλαδή από δεξιά προς τα αριστερά και από πάνω προς τα κάτω στο πλαίσιο της εικόνας. Συνεπώς, απαιτείται ένα κύκλωμα που θα λαμβάνει τα εικονοστοιχεία σειριακά και με κάποιο τρόπο θα τα προωθεί στα επόμενα στάδια παράλληλα. Εν προκειμένω, τα εικονοστοιχεία λαμβάνονται ένα-ένα και ομαδοποιούνται σε τετράδες ώστε να υπολογιστεί η μέση τιμή τους και να προκύψει ένα υπερ-εικονοστοιχείο. Ένα ακόμα ζήτημα εδώ είναι πως πρέπει να σαρωθεί μια ολόκληρη γραμμή εικόνας ώστε να μπορέσει να ξεκινήσει η διαδικασία υπολογισμού των μέσων τιμών. Οι γραμμές επεξεργάζονται σε ζευγάρια και η πρώτη από κάθε ζεύγος αποθηκεύεται προσωρινά σε έναν FIFO buffer. Αυτό προσθέτει σημαντική καθυστέρηση στη λειτουργική απόδοση του συστήματος. Παρ΄ όλ΄ αυτά, ο επιταχυντής FPGA υποστηρίζει παράλληλη επεξεργασία, επομένως ο υπολογισμός των μέσων τιμών κάθε πλέγματος 2×2 και η αποθήκευση της επόμενης γραμμής εικόνας συμβαίνουν ταυτόχρονα.

Σχήμα 2: Σχεδιαστική απεικόνιση του πυρήνα Ομαδοποίησης Εικονοστοιχείων.

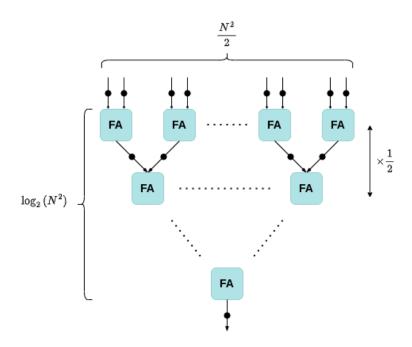

Το έτερο μπλοχ είναι η μονάδα πολλαπλασιαστή-συσσωρευτή (MAC) η οποία λαμβάνει παράλληλα τις τιμές των εικονοστοιχείων της  $2\times2$  ή  $4\times4$  γειτονιάς. Όπως βλέπουμε στην Εικόνα 2, το πρώτο υπο-κύκλωμα είναι μια δομή δέντρου από πλήρεις αθροιστές που πραγματοποιεί ταχύτατα προσθέσεις αξιοποιώντας τον παραλληλισμό. Στη συνέχεια, το συνολικό άθροισμα μεταβιβάζεται στον Διαιρέτη ο οποίος υπολογίζει τη μέση τιμή διαιρώντας απλώς με το 4 (ή με το 16). Γενικότερα στον προγραμματισμό υπολογιστών, οι αριθμητικές μετατοπίσεις συνιστούν έναν πολύ αποτελεσματικό τρόπο για τις πράξεις του πολλαπλασιασμού ή της διαίρεσης. Η μετατόπιση των bit προς τα αριστερά κατά η θέσεις σε έναν δυαδικό αριθμό έχει ως αποτέλεσμα τον πολλαπλασιασμό του επί 2η, ενώ αντίστοιχα η μετατόπιση των bit προς τα δεξιά κατά η θέσεις καταλήγει σε διαίρεση με το 2η. Συνεπώς, ο διαιρέτης απλώς εκτελεί μια αριθμητική μετατόπιση προς τα δεξιά κατά N-bit στο άθροισμα εξόδου του δέντρου αθροιστή, όπου N είναι η αντίστοιχη διάσταση του τετραγωνισμένου πλέγματος που χρησιμοποιείται στην ομαδοποίηση. Η έξοδος του κυκλώματος αναφέρεται στο νέο υπερ-εικονοστοιχείο της παραγόμενης εικόνας.

#### Συνδυαστική υλοποίηση ΗW/SW για τη Συσταδοποίηση

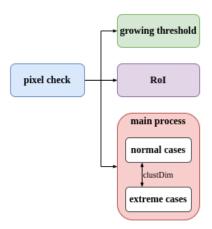

Το χύριο θέμα που πραγματεύεται η παρούσα διπλωματιχή είναι η υλοποίηση ενός αποδοτιχού αλγορίθμου για συσταδοποίηση των ειχονοστοιχείων που συγχροτούν αστέρι. Αυτό είναι το πρώτο στάδιο της προγραμματιστιχής ροής ενός Ανιχνευτή Αστέρων. Ο παραδοσιαχός τρόπος προσέγγισης για ανίχνευση των αστέρων στην ειχόνα περιγράφεται αχολούθως. Αρχικά, χάθε ειχονοστοιχείο συγχρίνεται με ένα σαφώς χαθορισμένο χατώφλι χαι εάν η τιμή του είναι μεγαλύτερη ή ίση, τότε ορίζεται χαταλλήλως μια περιοχή ενδιαφέροντος εντός της οποίας πραγματοποιείται η αναζήτηση του αστέρα. Κατα τη διάρχεια της αναζήτησης εντός της περιοχής ενδιαφέροντος χρησιμοποιείται ένα άλλο, συνήθως μιχρότερο χατώφλι για τη σύγχριση των τιμών των ειχονοστοιχείων. Τα γειτονιχά ειχονοστοιχεία που βρίσχονται πάνω από το λεγόμενο χατώφλι αύξησης, συγχεντρώνονται σε ομάδες χαι σχηματίζουν μια συστάδα σε ένα μέγιστο πλέγμα 5×5 ειχονοστοιχείων. Ο σχεδιασμός πάνω στο υλιχό είναι ιδιαίτερα απαιτητιχός εξαιτίας των δομών δεδομένων χαι της έλλειψης χρήσιμων συναρτήσεων. Επειδή λοιπόν ο αλγόριθμος συσταδοποίησης είναι από τη φύση του επαναληπτιχός και χρησιμοποιεί αναδρομιχές υπορουτίνες, είναι πολύ σημαντιχή η βελτιστοποίησή του ώστε να έχει χαμηλούς χρόνους εχτέλεσης.

#### Μηχανισμός Αναζήτησης Εικονοστοιχείων

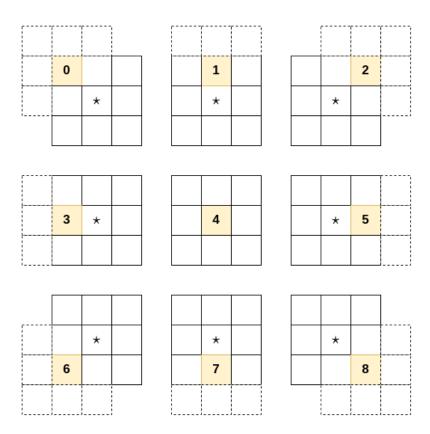

Μετά την κατωφλίωση με το πρωταρχικό κατώφλι, επιτελείται η αναζήτηση στην περιοχή ενδιαφέροντος για κάθε ένα εικονοστοιχείο που εντοπίστηκε. Προκειμένου να επιταχυνθεί η διαδικασία αυτή, προτείναμε έναν μηχανισμό αναζήτησης με σκοπό τη μείωση των απαιτούμενων κύκλων ρολογιού. Έτσι, θεωρούμε τα εικονοστοιχεία που προέκυψαν από το πρώτο κατώφλι ως σημεία εκκίνησης της αναζήτησης και στο εξής θα αναφέρονται ως 'εικονοστοιχεία εκκίνησης'. Αρχικά, για κάθε εικονοστοιχείο εκκίνησης ελέγχονται τα 8 γειτονικά του εικονοστοιχεία στο πλέγμα 3×3 συγκρίνοντας τις τιμές τους με το επονομαζόμενο 'αυξανόμενο κατώφλι' και στη συνέχεια πραγματοποιείται η ίδια διαδικασία για κάθε ένα από αυτά που έχουν τιμή μεγαλύτερη ή ίση αυτού. Η διαφορά όμως έγκειται στο οτι κάποια από τα γειτονικά εικονοστοιχεία της 3×3 περιοχής έχουν ήδη ελεγχθεί προηγουμένως. Η διαδικασία αναζήτησης των εικονοστοιχείων περιορίζεται στις εξής 9 περιπτώσεις που αποτυπώνονται στην παρακάτω Εικόνα 3. Κάθε εικονοστοιχείο που εξετάζεται φέρει έναν αριθμό που υποδηλώνει τη σχετική του θέση στη γειτονιά στην οποία ανιχνεύτηκε ώστε να αναγνωρίζεται σε ποιά από τις 9 περιπτώσεις βρίσκεται και να ελέγχονται τα αντίστοιχα εικονοστοιχεία.

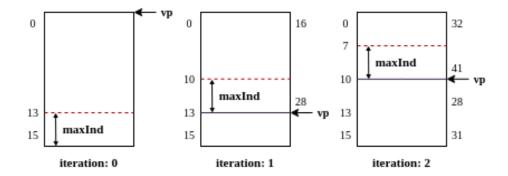

#### Διαδικασία λήψης δεδομένων εικόνας

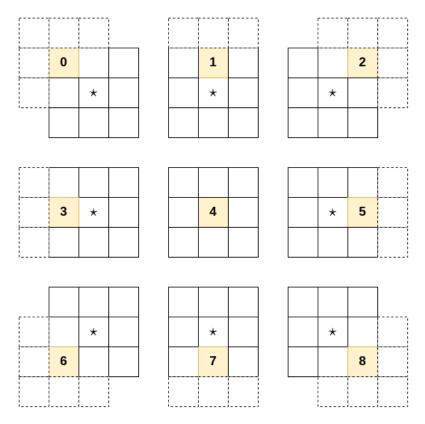

Στο σημείο αυτό θα αναλύσουμε λίγο περισσότερο σε βάθος τα επιμέρους στοιχεία που απαρτίζουν τη μονάδα Συσταδοποίησης. Πρωτίστως, να αναφέρουμε πως σε αυτήν την περίπτωση χρησιμοποιήθηκαν τα πρωτόκολλα επικοινωνίας ΑΧΙ4 Stream καθώς επίσης και ΑΧΙ4 Lite. Όσον αφορά το πρώτο πρωτόκολλο, εξυπηρετεί την επικοινωνία με το μπλοκ Ομαδοποίησης εικονοστοιχείων απ΄ το οποίο λαμβάνει τα εικονοστοιχεία της νέας επεξεργασμένης εικόνας, ενώ το δεύτερο εξυπηρετεί τη δυναμική προσαρμογή κατωφλίου λαμβάνοντας τις τιμές από έναν συγκεκριμένο καταχωρητή στη μνήμη του SoC FPGA. Προκειμένου να είναι δυνατή η αναζήτηση των αστεριών εντός της εικόνας, είναι απαραίτητη η προσωρινή της αποθήκευση

Σχήμα 3: Μηχανισμός αναζήτησης εικονοστοιχείων.

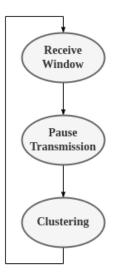

στο τμήμα του PL όπου εκτελείται η συσταδοποίηση. Ωστόσο, εξαιτίας των περιορισμένων πόρων του FPGA, καθίσταται αδύνατη αποθήκευση ολόκληρης της εικόνας ακόμα και μετά την ομαδοποίηση των εικονοστοιχείων που υποδιπλασιάζει τις διαστάσεις της. Συνεπώς, η εικόνα στέλνεται τμηματικά σε κομμάτια που ονομάζουμε 'κυλιόμενα παράθυρα' και έτσι πραγματοποιείται η αναζήτηση συστάδων. Συνεπώς η διαδικασία επεξεργασίας της εικόνας παρουσιάζεται στο παρακάτω σχήμα. Τα κυλιόμενα παράθυρα είναι επικαλυπτόμενα προκειμένου να είναι κατά το δυνατόν πιο ακριβής η αναζήτηση των συστάδων. Η επικάλυψη είναι προκαθορισμένη και παραμετροποιήσιμη και σχετίζεται άμεσα με το μέγεθος των συστάδων που είναι προς αναζήτηση. Πιο συγκεκριμένα, η περιοχή ενδιαφέροντος ορίζεται γύρω από το εικονοστοιχείο εκκίνησης οριοθετώντας γύρω του μια τετραγωνική περιοχή 7×7. Η τιμή αυτή προκύπτει ώστε να είναι δυνατή η ανίχνευση συστάδων σε πλέγμα μέχρι και 5×5. Έτσι λοιπόν, εάν το εικονοστοιχείο εκκίνησης βρίσκεται στις τελευταίες γραμμές του παραθύρου, δεν μπορεί να οριστεί η απαραίτητη περιοχή ενδιαφέροντος και χωρίς βλάβη της γενικότητας, θεωρούμε οτι η συστάδα εντοπίζεται καλύτερα στις παρακάτω γραμμές της εικόνας οπότε και εξετάζεται στο επόμενο παράθυρο.

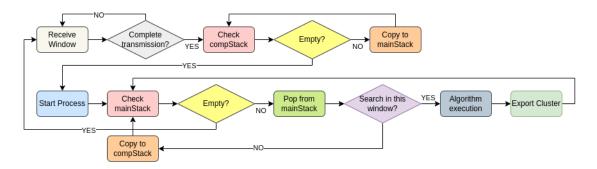

#### Περιγραφή του πυρήνα Συσταδοποίησης

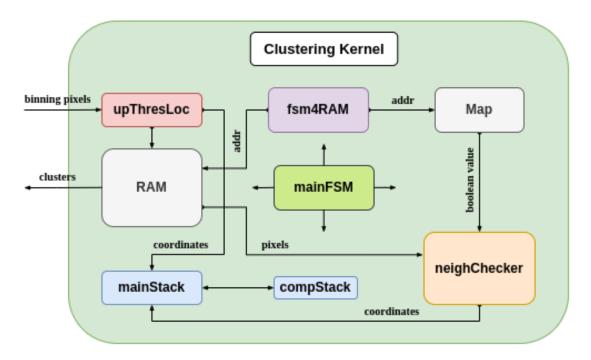

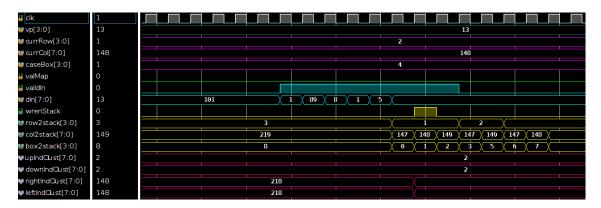

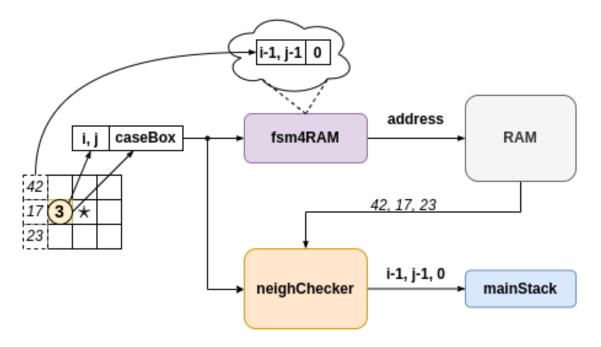

Το περιγραφικό διάγραμμα του πυρήνα Συσταδοποίησης απεικονίζεται παρακάτω στην Εικόνα 5. Όλα τα επιμέρους στοιχεία του μπλοκ ελέγχονται από μια μηχανή πεπερασμένης κατάστασης (FSM). Αρχικά, τα εισερχόμενα ομαδοποιημένα εικονοστοιχεία εξετάζονται από το upThresLoc στο οποίο πραγματοποιείται η πρώτη κατωφλίωση, πρωτού καταλήξουν στη

Σχήμα 4: Διάγραμμα ροής για τη λήψη των δεδομένων εικόνας.

μνήμη RAM όπου και αποθηκεύονται προσωρινά. Οι συντεταγμένες των εικονοστοιχείων που προχύπτουν από την πρώτη κατωφλίωση αποθηκεύονται στην αντίστοιχη στοίβα. Οι main-Stack και compStack είναι δομές που αποτελούνται από 3 στοίβες εκ των οποίων οι δύο είναι για τις συντεταγμένες i, j των εικονοστοιχείων και η τρίτη αναφέρεται στη σχετική θέση αυτών που ανιχνεύτηκαν στην  $3\times3$  γειτονιά αναζήτησης. Τα δύο κύρια μπλοκ είναι αυτό της fsm4ram και του neighChecker. Όσον αφορά το πρώτο, η λειτουργία του χωρίζεται σε 3 κατευθύνσεις οι οποίες είναι οι εξής: η πρώτη αφορά τον υπολογισμό διευθύνσεων στις οποίες θα γράφονται τα αντίστοιχα εισερχόμενα ειχονοστοιχεία στη μνήμη, η δεύτερη αφορά τον υπολογισμό των κατάλληλων διευθύνσεων των εικονοστοιχείων κατά τη διαδικασία συσταδοποίησης και η τρίτη σχετίζεται με τον υπολογισμό διευθύνσεων κατά την εξαγωγή της συστάδας που ανιχνεύτηκε. Σχετικά με το δεύτερο και σημαντικότερο υποστοιχείο, αυτό επιτελεί ουσιαστικά τον έλεγχο της συσταδοποίησης. Δέχεται τις τιμές των κατάλληλων ειχονοστοιχείων στη γειτονιά αναζήτησης και τις συγχρίνει με το αυξανόμενο κατώφλι. Εάν προχύψει οτι χάποιο απ' τα ειχονοστοιχεία ανήχει στη συστάδα, τότε εξάγονται οι συντεταγμένες αυτού ώστε να ελεγχθούν μετέπειτα τα δικά του γειτονικά εικονοστοιχεία. Παράλληλα, επιτελείται και η διαδικασία υπολογισμού των διαστάσεων της συστάδας. Αρχικά, ορίζονται 4 μεταβλητές με τις συντεταγμένες του ειχονοστοιχείου εχχίνησης οι οποίες αντιστοιχούν στο πάνω, κάτω, δεξί και αριστερό άκρο της συστάδας καταγράφοντας ουσιαστικά τις κινήσεις που πραγματοποιούνται κατά την αναζήτηση εντός της περιοχής ενδιαφέροντος. Όταν ολοκληρωθεί η διαδικασία υπολογίζεται η διάσταση της τετραγωνικής συστάδας και οι συντεταγμένες του άνω αριστερού ειχονοστοιείου αυτής. Στο σημείο αυτό, αξίζει να σημειωθεί πως είναι πιθανό να εντοπιστεί ένα μόνο εικονοστοιχείο εντός της περιοχής ενδιαφέροντος. Σε αυτήν την περίπτωση θεωρούμε πως δεν συνιστά έγχυρη συστάδα οπότε και απορρίπτεται. Επιπλέον, δεν αποκλείεται να προκύψει και συστάδα σε πλέγμα 7×7, όμως σε αυτήν την περίπτωση εξαιτίας των προδιαγραφών που δόθηκαν από την Infinite Orbits, επιλέγεται ένα τμήμα 5×5 εντός του πλέγματος αυτού το οποίο και εξάγεται. Τα υπόλοιπα στοιχεία του πυρήνα συσταδοποίησης

είναι η μνήμη στην οποία αποθηκεύονται τα κυλιόμενα παράθυρα και ένα ακόμα που ονομάζεται Μαρ και ουσιαστικά είναι κι αυτός μια μονάδα μνήμης. Ως ένας τρόπος για βελτιστοποίηση του αλγορίθμου αναζήτησης, εισήχθη το συγκεκριμένο στοιχείο στο οποίο καταγράφονται τα εικονοστοιχεία που έχουν ελεγχθεί προκειμένου να αποφεύγονται επαναληπτικοί έλεγχοι για αυτά στην περιοχή ενδιαφέροντος. Αυτό επίσης υποδηλώνει πως ένα εικονοστοιχείο θα ελεγχθεί στο πλαίσιο μίας και μόνο συστάδας.

Σχήμα 5: Σχεδιαστική αναπαράσταση του πυρήνα Συσταδοποίησης.

#### Βελτιστοποιήσεις ως προς την απόδοση

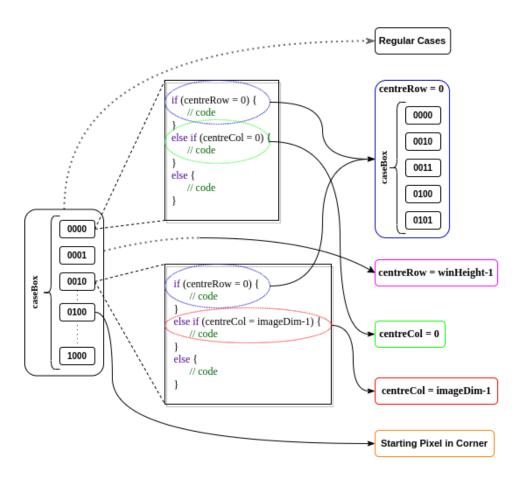

Στο σημείο αυτό θα παρουσιάσουμε μερικές από τις βελτιστοποιήσεις που πραγματοποιήσαμε. Κατα τη διαδικασία ανάγνωσης, υπάρχουν ορισμένες ακραίες περιπτώσεις όσον αφορά τη θέση του κεντρικού εικονοστοιχείου που διαφοροποιούν τη διαμόρφωση της γειτονιάς αναζήτησης. Αυτές οι περιπτώσεις εμφανίζονται όταν το κεντρικό εικονοστοιχείο βρίσκεται στα άκρα του παραθύρου που σημαίνει ότι συνορεύει με λιγότερα από 8 εικονοστοιχεία, οπότε δεν μπορεί να σχηματιστεί γειτονιά 3×3. Στην περίπτωσή μας, ο αρχικός κώδικα γράφτηκε με τέτοιον τρόπο που περιείχε πολλά εμφωλευμένα if-else. Αυτός ο τρόπος συγγραφής κώδικα με βάση τον προγραμματισμό σε γλώσσες υψηλού επιπέδου είναι εξαιρετικά αναποτελεσματικός για σχεδιασμό υλικού καθώς επηρεάζει τον τρόπο με τον οποίο αποτυπώνεται η λογική πάνω σε αυτό. Υποθέτοντας πως κάθε κατάσταση if αντιπροσωπεύει μια διεργασία που εκτελείται από ένα FSM, ομαδοποιούμε τις παρόμοιες διεργασίες που εκτελούνται υπό την ίδια συνθήκη. Αυτή η τεχνική μπορεί να ερμηνευθεί ως ένας τρόπος καταμερισμού εργασιών και οδηγεί σε ενίσχυση του παραλληλισμού. Αυτή η βελτιστοποίηση γίνεται περισσότερο κατανοητή με την παρακάτω εικόνα 6.

Όπως περιγράφηκε προηγουμένως, υπάρχει ισχυρή συσχέτιση μεταξύ των εργασιών που εκτελούνται από το fsm4RAM και το neighChecker. Επομένως, η ίδια λογική που περιγράφηκε

Σχήμα 6: Αναπαράσταση καταμερισμού διεργασιών.

παραπάνω υιοθετήθηκε και από τη μονάδα neighChecker, ώστε να σχηματίζονται έξι επιμέρους μπλοκ για αύξηση του παραλληλισμού. Ωστόσο, η ιδέα μπορεί να επεκταθεί και στα χαμηλότερα επίπεδα της σχεδίασης. Για κάθε εισερχόμενη τιμή του εικονοστοιχείου, πραγματοποιούνται τρεις λειτουργίες ελέγχου, ώστε να μπορεί να θεωρηθεί το εικονοστοιχείο ως μέρος μιας συστάδας. Αυτά τα τρία βήματα ελέγχου περιγράφονται ως εξής:

- Σύγκριση με το αυξανόμενο κατώφλι και αποφυγή επανελέγχου

- Έλεγχος ώστε το προς έλεγχο ειχονοστοιχείο να βρίσχεται εντός της περιοχής ενδιαφέροντος

- Εξαγωγή συντεταγμένων και ενημέρωση των διαστάεων της συστάδας

Έτσι, αντί να εκτελούνται αυτά τα τρία αλληλοεξαρτώμενα στάδια ελέγχου, διαχωρίζονται σε τρεις μεμονωμένες και ανεξάρτητες διεργασίες. Καθένα από τα έξι υποσυστήματα που σχηματίζονται εκτελεί αυτά τα ξεχωριστά στάδια ελέγχου. Κάθε ένα εξ αυτών ενεργεί σαν να ικανοποιούνται οι υπόλοιπες δύο συνθήκες ελέγχου και προκύπτει ένα τελικό σήμα ώστε εάν ικανοποιούνται και οι τρεις τα αποτελέσματα που εξάγονται να θεωρούνται έγκυρα. Μετά τα βήματα βελτιστοποιήσεων που περιγράφησαν παραπάνω, καθώς και κάποια άλλα που εξετάζονται αναλυτικά στο κύριο μέρος της διπλωματικής εργασίας προέκυψαν τα παρακάτω αποτελέσματα που αναγράφονται στον Πίνακα 1.

**Πίνακας 1:** Συγκριτικός Πίνακας με τις συχνότητες ρολογιού που επετεύχθησαν κατόπιν βελτιστοποιήσεων

| Στοιχείο          | Περίοδος Ρολογιού | Βελτιστοποιημένη<br>Περίοδος Ρολογιού | Ποσοστό<br>Βελτίωσης |

|-------------------|-------------------|---------------------------------------|----------------------|

| upperThresLoc     | 3.7 ns            | 2.4 ns                                | 35.1%                |

| fsm4RAM           | 5 ns              | 5 ns                                  | 30%                  |

| clusterCal        | 4.3 ns            | 3.2 ns                                | 25.6%                |

| neighChecker      | 9.4 ns            | 4.4 ns                                | 53.2%                |

| Clustering kernel | 11.2 ns           | 4.3 ns                                | 61.6%                |

### Πειραματική Αξιολόγηση

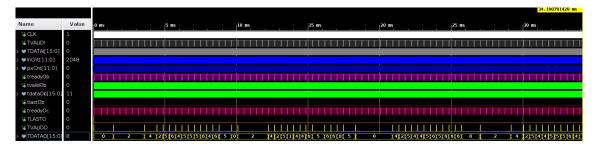

Η πλακέτα που χρησιμοποιήθηκε για τη πειραματική αξιολόγηση του συστήματος που υλοποιήσαμε είναι το Zedboard το οποίο περιλαμβάνει το Zynq-7020 SoC FPGA. Η σχεδίαση του υλιχού πραγματοποιήθηκε στο εργαλείο Vivado Design Suite v2019.1 της Xilinx ενώ επιπλέον χρησιμοποιήθηκε το συμπληρωματικό εργαλείο Xilinx Software Development Kit (XSDK) για τη δημιουργία ενσωματωμένων εφαρμογών που εκτελούνται στον διπύρηνο επεξεργαστή ARM Cortex του Zynq SoC, έτσι ώστε να εδραιωθεί την επιχοινωνία PS-PL. Στο πλαίσιο της παρούσας διπλωματικής, τα πειράματα που πραγματοποιήθηκαν επικεντρώνονται στα στάδια προεπεξεργασίας των δεδομένων ενός ανιχνευτή αστέρων δίνοντας έμφαση στην επιτάχυνση του αλγορίθμου συσταδοποίησης. Όπως έχει ήδη αναφερθεί χρησιμοποιήθηκαν ειχόνες σε μορφή χλίμαχας του γχρι με ανάλυση 2048×2048, αν και το σύστημα εξετάστηκε και με εικόνες μικρότερου μεγέθους. Το σύνολο δεδομένων εισόδου δημιουργήθηκε από ένα αποθετήριο που περιέχει το πλήρες αρχείο καταγεγραμμένων φωτογραφιών από τη διαστημική αποστολή Cassini της NASA που ελήφθησαν από το Φεβρουάριο του 2004 έως το Σεπτέμβρίο του 2017 [14]. Στον παρακάτω συγκεντρωτικό Πίνακα 1 παρουσιάζονται τα αποτελέσματα όσον αφορά την απόδοση των επι μέρους συστημάτων για τις δύο διαφορετικές προσεγγίσεις οι οποίες αφορούν το συνδυασμό υλικού/λογισμικού στο Zynq SoC FPGA, καθώς επίσης και την υλοποίηση λογισμικού που εκτελείται στον ARM επεξεργαστή της πλατφόρμας.

Πίνακας 2: Σύγκριση μέσων χρόνων εκτέλεσης μεταξύ των δύο προσεγγίσεων για κάθε ένα από τα υλοποιημένα στοιχεία

| Σύστημα                   | ARM       | SoC     | Επιτάχυνση | Εχτιμώμενος<br>χρόνος<br>εχτέλεσης | Εκτιμώμενη<br>επιτάχυνση |

|---------------------------|-----------|---------|------------|------------------------------------|--------------------------|

| Σύστημα<br>Ομαδοποίησης   | 1607.5 ms | 33.6 ms | 47.9x      | 16.8 ms                            | 95.8x                    |

| Σύστημα<br>Συσταδοποίησης | 383.1 ms  | 8.9 ms  | 43.1x      | 5.11 ms                            | 75.4x                    |

| Πλήρες<br>Σύστημα         | 2050.3 ms | 34.1 ms | 60.2x      | 18.9 ms                            | 108.2x                   |

Ο παραχάτω συγκεντρωτικός πίναχας παρουσιάζει μια σύνοψη της χρήσης πόρων του FPGA μετά την αποτύπωση της λογικής στο υλικό.

Πίνακας 3: Χρήση πόρων του FPGA για το ολοκληρωμένο σύστημα.

| Πόροι  | Χρήση | $oldsymbol{\Delta}$ ιαθέσιμοι | Χρήση (%) |

|--------|-------|-------------------------------|-----------|

| LUT    | 8837  | 53200                         | 16.61     |

| LUTRAM | 849   | 17400                         | 4.88      |

| FF     | 11733 | 106400                        | 11.03     |

| BRAM   | 20    | 140                           | 14.29     |

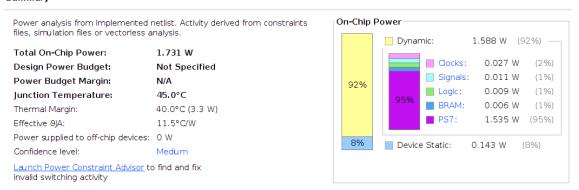

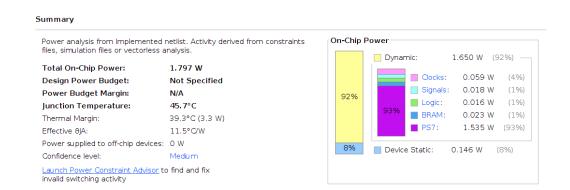

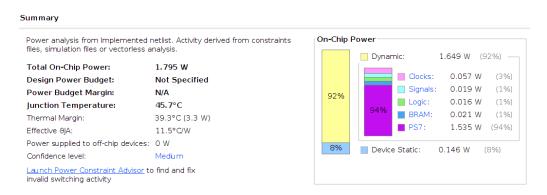

Τέλος, η Εικόνα 7 παρουσιάζει την εκτιμώμενη κατανάλωση ισχύος του FPGA η οποία υπολογίζεται περίπου στα 1.795 Watt. Όπως βλέπουμε, η δυναμική ισχύς που καταναλώνεται αφορά το μεγαλύτερο μέρος της συνολικής ισχύος σε ποσοστό 92%, ενώ το αντίστοιχο ποσοστό της στατικής ισχύος εκτιμάται σε μόλις 8%. Επιπλέον, αξίζει να αναφερθεί πως όσον αφορά τη δυναμική ισχύ, για το μεγαλύτερο μέρος της υπεύθυνο είναι σύστημα του επεξεργαστή του Zyng SoC FPGA σε ποσοστό περίπου 94%.

#### Summary

Σχήμα 7: Εκτιμώμενη κατανάλωση ισχύος για το ολοκληρωμένο σύστημα.

Συμπερασματικά, η προτεινόμενη αρχιτεκτονική σχεδίασης χρησιμοποιεί λιγότερο από 20% των πόρων του FPGA για κάθε συστατικό στοιχείο. Ως εκ τούτου, δίνεται η δυνατότητα ανάπτυξης πρόσθετων στοιχείων HDL για την ολοκλήρωση των αλγοριθμικών βημάτων του ανιχνευτή αστέρων. Σε τελική ανάλυση, υλοποιήσαμε ένα στοιχείο στο Zynq-7020 SoC FPGA που συνδυάζει το υλικό με το λογισμικό και επιτελεί τα πρώτα στάδια προεπεξεργασίας δεδομένων με εκτιμώμενη κατανάλωση ισχύος στο chip κάτω από 2 Watt.

### Συμπεράσματα και Μελλοντικές Προεκτάσεις

Η παρούσα διπλωματική εργασία πραγματεύεται την ανάπτυξη ενός επιταχυντικού αλγορίθμου για την προεπεξεργασία δεδομένων ενός ανιχνευτή αστέρων, ο οποίος υλοποιείται σε μια συνδυαστική αρχιτεκτονική υλικού/λογισμικού σε μια πλατφόρμα SoC FPGA. Πιο συγκεκριμένα, η προεπεξεργασία χωρίζεται σε δύο βήματα λειτουργίας τα οποία είναι η ομα-

δοποίηση ειχονοστοιχείων και η συσταδοποίηση αντίστοιχα. Και οι δύο λειτουργίες σχεδιάστηκαν, υλοποιήθηκαν και δοκιμάστηκαν μεμονωμένα χρησιμοποιώντας πραγματικές εικόνες. Επιπροσθέτως, παρουσιάζεται μια λεπτομερής επισχόπηση των βελτιστοποιήσεων που πραγματοποιήθηκαν στον αλγόριθμο συσταδοποίησης αξιολογώντας τις επιτευχθείσες συχνότητες λειτουργίας. Επιπλέον, οι προτεινόμενες αρχιτεκτονικές αναπτύχθηκαν και σε επίπεδο λογισμικού ώστε να εκτελεστούν στον ενσωμεταμένο ARM επεξεργαστή του Zyng SoC FPGA. Ο συνδυαστικός σχεδιασμός Υλικού/Λογισμικού υπερτερεί πλήρως έναντι της εκτέλεσης στο επεξεργαστή όσον αφορά την απόδοση καθώς κατάφερε να μειώσει το συνολικό χρόνο εκτέλεσης κατά περίπου 60 φορές, ενώ εκτιμάται οτι η επιτάχυνση αυτή μπορεί να αυξηθεί έως και τις 108 εάν το σύστημα πιάσει το μέγιστο της εκτιμώμενης συχνότητας λειτουργίας. Όσον αφορά την κατανάλωση ενέργειας, η συνολική ισχύς εκτιμάται περίπου στα 1.8 W, πράγμα που σημαίνει πως η προτεινόμενη αρχιτεκτονική είναι κατάλληλη για ένα ευρύ φάσμα οικονομικά αποδοτικών διαστημικών εφαρμογών. Τέλος, το προτεινόμενο ενσωματωμένο σύστημα είναι σχετικά μη απαιτητικό όσον αφορά τη χρήση των πόρων του FPGA, αφήνοντας περιθώριο για πρόσθετες υλοποιήσεις υλικού που αφορούν την προγραμματιστική ροή ενός συστήματος ανιχνευτή αστέρων.

Η μελλοντική μας εργασία θα επικεντρωθεί στη βελτίωση της απόδοσης του συστήματος, συμπεριλαμβανομένης της περαιτέρω εξέτασης των παραμέτρων που περιορίζουν τη συχνότητα λειτουργίας, ώστε να επιτευχθεί η μέγιστη εκτιμώμενη συχνότητα και να αυξηθεί περαιτέρω εάν είναι δυνατόν. Επιπλέον, θα εκτελέσουμε περαιτέρω πειράματα ώστε να επεκτείνουμε την αξιολόγηση και την επαλήθευση των τεχνικών μας με τη χρήση πραγματικών δεδομένων προσαρμοσμένων στις απαιτήσεις της Infinite Orbits. Τέλος, ο κύριος στόχος μας είναι να συνδυάσουμε το προτεινόμενο σύστημα με τις υπόλοιπες προγραμματιστικές διαδικασίες ώστε να ολοκληρωθεί το σύστημα του ανιχνευτή αστέρων και να συμπεριληφθεί σε μια μελλοντική διαστημική αποστολή καθοδηγούμενη από την Infinite Orbits.

### Chapter 1

### Introduction

This chapter's goal is to describe the motivation behind this work and introduce readers to some of the problems appearing in space industry. In addition, it contains the main scope of the thesis, as well as a brief outline of it.

#### 1.1 Motivation

Nowadays, the technological evolution has brought significant achievements in almost every scientific field. More specifically, when it comes to space industry, the progress that has been made has had great influence on the development of human society. However, other than opening up new horizons and opportunities, some major challenges have arisen.

This current thesis was conducted in cooperation with Infinite Orbits in the context of the research activity of the Microprocessors and Digital Systems Lab regarding the applications of COTS FPGAs in space. Infinite Orbits is a company which operates in space industry and provides innovative in-orbit services. Among the cases that Infinite Orbits, as well as other companies are facing appears to be life extension. Satellite's lifespan ranges between 12 and 18 years, but the prevailing design life remains at 15 years. As per NSR's recent study, commercial GEO communications satellites in-orbit today have an average age of 8.9 years [15]. The idea of in-space service prolonging the life of a satellite in orbit is yet to be accomplished. Instead, of replacing the entire satellite, we could get another one to rendezvous and dock onto the outdated system providing a refueling source. Life extension is reportedly a very challenging case of rendezvous and docking due to the difficulties associated with the non-cooperative nature of the target satellite, the risks involved and the characteristics of the orbit, and thus extreme accuracy and safety is required. The main idea proposed by Infinite Orbits to resolve these challenges, is developing an embedded satellite navigation system which uses neural network-based models for image processing aiming to achieve real-time performance using a custom FPGA accelerator.

There are specific requirements that system in orbit needs to meet and are summarised as follows. First of all, the communication channel of the satellite is characterised by high latency and unreliability. Thus, the software is expected to be smart enough and capable of high levels of autonomy. Another challenge is that satellites involve excessive costs and therefore mistakes must be avoided. The system needs to work constantly or at least be able to fail safely. Because of the mission's nature and lack of validation environment on ground, it is really exacting to achieve robustness. Finally, fast performance is needed so that the system is responsive to deal with unwanted situations and avoid accidents. Some of the most common instruments to measure satellite's orientation fast and precisely are star trackers.

Determining the position of a satellite plays a prominent role among the majority of space missions. This type of information is vital for space navigation, firing thrusters which control altitude and pointing antennas to required positions. There are various types of sensors used for attitude determination, some of the most common are horizon sensors (or conical Earth scanners), sun sensors, star sensors and magnetometers[16]. Each type can be used individually or in combination with the others and in the aggregate they constitute part of an integrated attitude determination and control system (ADCS).

Among the above instruments mentioned, star trackers are capable of providing high accuracy for attitude determination. In many cases where there are demanding scientific objectives, an attitude control system of high accuracy is required. It is therefore understood why star trackers are of high importance. Additionally, there are missions where a certain level of agility is required for specialized tasks. For example, satellites should be agile and maneuverable as it considerably increases the return of earth and science mission data making them more efficient.

#### 1.2 Thesis Scope

In this thesis, we focus on the first stages of a star detection algorithm which in particular are associated with the preprocessing of the image captured by the sensor of the system. More specifically, we propose an efficient algorithm which applies in a star tracking system that detects clusters of stars, which are to be used during the next stages for centroid extraction. Furthermore, we aim to implement a HW/SW co-design which runs at a SoC FPGA accelerated system in order to achieve fast performance.

We suppose that we have a satellite in orbit that is being provided with frames that were captured by the system's sensor. Each frame is a two dimensional image that contains only a portion of the night sky. Star trackers, need to evaluate this data and determine the attitude recognising patterns of constellations and mapping them to known star positions in a catalogue. The challenge here is that large images need to be processed and the computation should be fast and accurate as long as star tracker's update rate depends on that. Thus, we can understand that fast execution while processing each frame is critical to achieve real-time performance.

Several commercial star tracker solutions exist but are not easily accessible. They are of high cost and it is often a preferable option to develop a custom one according to the

mission's requirements. The block diagram of a typical star tracker is shown below in Figure 1.1.

Figure 1.1: Block diagram of a typical Star Tracker.

Generally, star trackers play an important role to the entire satellite's Attitude Determination and Control System (ADCS) and they consist of a CMOS Image Sensor that is exposed to light and digital hardware that processes the data. Usually, a System-on-Chip (SoC) device which integrates a processor, a Field Programmable Gate Array (FPGA) including interconnections, memory and some peripherals all in one chip, is responsible for the processing of the image data. When considering CPU & FPGA co-processing, the most prominent devices are the COTS SoC FPGAs, which integrate both types of processors in a single chip [17]. However, space community employs both space-grade [18][19][20][21] and Commercial Off-The-Shelf (COTS) [18][22][23] FPGAs. In general, FPGAs are not only utilised to accelerate complex DSP functions of high computational intense, but they can be used as well as add-on processors in co-processing architectures [24][25][26] where they perform operations such as I/O handling, data transcoding and data compression.

Figure 1.2: System-on-Chip Layout.

Figure 1.3: Process Flow of a Star Tracker.

The sequential process flow of a Star Tracker is shown in figure 1.3. Exposure time is

the first stage of the process and is the time needed for the sensor to produce image data of the night sky. Afterwards, data are processed on the FPGA platform so as to extract centroids which consequently are forwarded to the processor. The final stage of the process is matching. During that stage, a pattern recognition algorithm is executed in order to identify the extracted centroids by mapping them to a known star catalogue. The main scope of this thesis is to develop an efficient algorithm that performs the preprocessing tasks and is presented in Chapter 3. That is a non trivial problem due to the limitations of the FPGA platform while certain requirements of the star tracker need to be met such as robustness, low cost, precision and low power consumption.

#### 1.3 Project Objectives

This thesis was a collaboration of Microlab-NTUA and Infinite Orbits and due to their uttermost contribution it was completed successfully. In addition to their excessive support, Infinite Orbits provided a custom camera lens which is to be used for future work and extension of this thesis. More specifically, the lens is a backside illuminated (BSI) scientific CMOS image sensor, with 4MP resolution (2048×2048) and 12 bits per pixel whose size is 6.5 µm. For the development and evaluation of the system a COTS SoC FPGA was utilised and in particular, Zedboard 7020 chip that hosts Xilinx ZYNQ SoC with ARM processor. Thus, the project objective is to optimise an algorithm used for star trackers and can be applied to an entire ADCS, on Zynq SoC for that specific image sensor which is provided by Infinite Orbits. However, as it will be discussed in the following chapters, the proposed system has been designed to be configurable in order to adjust to different conditions according to the mission's requirements and therefore it supports many different camera types. The specifications of this project are the following:

• Field of View (FOV):  $15.5^{\circ} \times 15.5^{\circ}$

• Image Resolution: 4 MP

• Pixel Depth: 12 bits

• Real-time performance of 1-2 frames per second

• Accelerated clustering algorithm

• Low Power Consumption

#### 1.4 Thesis Outline

The remaining of the thesis is structured as follows.

Chapter 2 presents the full background, which is helpful to completely understand the concept of our ideas and implementations in the following chapters. It involves some general information about star trackers, their characteristics and what is the main purpose they are used for. In addition, we will review some of the related work that has been published or is currently available for space missions and finally, we will provide an overview of SoC FPGAs, as well as a general outlook of the interconnection protocols that are used.

Chapter 3 focuses on the ideas that our algorithm is based on. We analyze quite extensively the proposed architectures presenting them both at high and low level. The first subsection of this chapter emphasizes on the averaging binning, while the second one describes the main algorithm for cluster extraction. Finally, we review the optimization steps we made aiming to achieve high performance.

Chapter 4 presents the experimental evaluation of the proposed system, along with a results section which basically compares the hardware to the software outcomes. It also refers to the power consumption and resource utilisation of our integrated system.

Chapter 5 is the final chapter, summarizing the conclusions drawn from the total contributions of our work.

# Chapter 2

# Background

In this section we are going to present background material for the explanation of the methods and ideas that have been used in the main part of the thesis. Our main focus is on the background of star trackers regarding some of their characteristics and algorithms used for their development.

# 2.1 Star Trackers

A star tracker is an optical device that measures the positions of stars. As long as this happens to a high degree of accuracy, a star tracker on a satellite or spacecraft may be used to determine its orientation with respect to the stars. In order to do this, the star tracker needs to obtain an image of the stars and measure their apparent position using pattern recognition algorithms so as to identify them compared to their known absolute position on a star map.

Generally, star sensing and tracking devices can be divided into three major classes which are star scanners, gimbaled star trackers and fixed head star trackers. Star scanners use the spacecraft's orientation to provide the searching and sensing function while gimbaled star trackers search out and acquire stars using mechanical action. Finally, the last class of star trackers has electronic searching and tracking capabilities over a limited field of view[27].

Attitude determination based on charge couple devices (CCD) area array image sensors was pioneered in the early 1970s. There are the so-called "First-Generation CCD Star Trackers" and consist of a CCD sensor, associated optics and dedicated electronics[28]. Within the last decade, a new generation of star trackers has been developed which involves units identified as "Second-Generation Star Trackers". The main difference from the prior generation is that pattern recognition algorithms are performed autonomously so as to identify constellations using internal catalogues. In addition, they are more advanced as expected and they are capable of high performance in adverse conditions.

#### 2.1.1 Star Tracker Characteristics

Commercial star trackers vary in terms of performance according to their characteristics. Depending on the mission's requirements, there are several parameters that can be adjusted in order meet these exact objectives.

#### Accuracy

As we have pointed earlier, accuracy correlates with the star tracking algorithms. The more demanding the application is, the more increasing the need is to develop algorithms of high accuracy, and so the performance becomes computationally intensive. Liebe in his article describes extensively how performance accuracy is measured[29]. Actually, there are two types of accuracy metrics when we refer to star trackers, pointing accuracy and rolling accuracy. Accuracy measurement is essentially the angle error curve of pointing and rolling axis with respect to the boresight[1]. Usually, they are also referred as cross boresight accuracy (pitch and yaw) and about boresight accuracy (roll) correspondingly and are quoted in  $3\sigma$  values. Cross boresight errors are significantly less than about boresight errors and modern star trackers are capable of accuracies that range from 0.1 to 20 arcseconds (cross boresight)[30]. In order to achieve such low levels of accuracies, sub-pixel accuracy is critical while executing centroid detection.

Figure 2.1: Pointing and rolling accuracy schematic of the star tracker [1].

#### Field of View

The size of the Field of View is probably the most important parameter. A narrow FOV implies high precision and is a requirement for astronomical star trackers. Low cost general purpose star trackers offer wide FOV whose size ranges from a few degrees to over 40° diagonally and are usually utilized as a part of the ADCS in micro satellites. High precision star trackers are capable of accuracies of 1 arcsecond. On the contrary, the typical precision of general purpose star trackers is about 15 to 20 arcseconds. However, decreasing the FOV has some disadvantages as well. First of all, it is more difficult to determine the initial attitude. When the FOV contains a small number of stars, the algorithm tend to reject the frame. Moreover, a much bigger star catalogue is required, which is significantly undesirable since it increases the amount of memory needed. Furthermore, initial attitude acquisition becomes a more complicated task and also the complexity of pattern recognition algorithms increases rapidly with the number of stars [2].

# **Update Rate**

The update rate basically depends on the exposure time and the processing time of the image. There is a strong correlation between exposure time and the optical and hardware design. The longer the exposure time, the more photons are captured by the image sensor and this results to a better signal-to-noise ratio. Choices regarding the sensitivity of the sensor, the aperture of the lens, the sky coverage and some other factors affect the exposure time. Generally, it is required to have a specific number of stars on average in the FOV. Thus, to compensate the decreased FOV, we usually increase aperture of the lens so as the fainter stars to be captured. The aperture primarily determines image sensor's sensitivity. Increasing the exposure time is another technique that is used in order to increase system's sensitivity. However, this method has disadvantages as it leads to lower update rates and smeary images that affect the performance of the ADCS. Therefore, exposure time and accuracy are trade-offs for a stable star tracker. Lastly, second generation star trackers need to process large amounts of data which is a significant limiting factor to update rate. In this thesis we focus on the acceleration of a clustering algorithm used in a star tracker sub-system in order to improve the processing speed.

# Physical Characteristics

Physical dimensions of a star tracker are important factors which are to be taken into consideration when discussing about commercial star trackers. The mass of a star tracker usually varies from 1 to more than 20 kg. At this point, it should be mentioned that aperture of the lens is proportional to the system's mass and size. High-performance star trackers are huge and are designed for more scientific space missions, hence the assumption that they are more accurate. However, the increasing market for microsatellites tends to push the interest towards smaller designs.

#### Other Characteristics

Other than the aforementioned, there are a few other characteristics that describe star trackers such as power consumption, sky coverage, SNR, star catalogue size and average number of stars tracked per frame. These all directly affect the performance of the system in a certain way. However, as we discussed earlier, there are no optimal choices as there are some trade-offs and so preference is given upon the parameters that meet the design's requirements.

# 2.1.2 Sub-pixel Accuracy

Generally, among the most limiting factors for the resolution of optical instruments, is the size of the sensor's pixel. In digital image processing, a sub-pixel resolution method is utilized to enhance the resolution of images and therefore to improve the algorithm's performance. A widely known technique to increase the accuracy, is the hyperacuity technique, also known as sub-pixel accuracy.

In a focused image, the star appears as a point source, so all the luminous power gathers in a single pixel. However, images might often be slightly defocused, even if they're taken by an expensive image sensor of high accuracy. In these cases, a star occupies several pixels in the image plane. This makes it easier to model the centre of the star mathematically.

It may seem intuitively inconsistent with the sampling theorem to increase the accuracy beyond one pixel, but it is the a priori knowledge of the pointspread function that is utilized in combination with the actual measure. The performance of the hyperacuity technique is defined by the algorithm used to determine the center of the star [2]. The achieved sub-pixel accuracy depends on the S/N ratio. Unlike the fancy mathematical models, the hyperacuity technique normally uses empirical calibrations which appear to be really consistent.

There is an enormous dynamic range of illumination between the brightest and the dimmest star. The resolution is limited when digitalising the CCD signal received from the sensor (typically 8 to 16 bits are used). This leads to a contrasting situation where the brightest stars will overflow and the dimmest stars will be hardly perceived due to noise. These different situations are shown in Figure 2.2

Figure 2.2: Different Stars Utilising Hyperacuity technique [2].

## 2.1.3 Theoretical Background

At this point it is important to introduce a theoretical background regarding the information that is obtained by the image. The image sensor captures only a small portion of the night sky that contains just a fraction of the stars which often appear dimmer or distorted. Stars within the FOV are projected onto an image plane, where their magnitudes are converted to a corresponding electron count. The magnitudes are expressed as two-dimensional Gaussian functions in order to account for the (u,v) image directions. The standard deviation of each Gaussian is determined by the sensor and optics of the system and is defined in units of pixel width.

The FOV is described here by only one angle, which is defined by the angle from the center of the lens to the outer edge of it. Camera's frame is defined with the z-axis pointing out the boresight, y-axis out of the top of the camera and x-axis completes the right-hand frame. Once the frame and the FOV are defined, we should determine camera's attutude, or orientation with respect to another reference frame. The most common one that is used is the J2000 Earth centered inertial (ECI) frame [31]. Hence, the entire catalogue in matching process is searched to find all stars within the camera's FOV by determining the angular distance between z-axis and each star's ECI unit vector.

Figure 2.3: Image sensor's perspective Projection model [3].

We should mention that each star on the is projected onto a two-dimensional image frame and so a determination of the three-dimensional points that represent the unit vector is needed. To do so, we should take into consideration some camera parameters: the intrinsic parameters regarding the properties of the sensor; and the extrinsic parameters, which are related to the location and attitude of the camera with respect to the inertial frame. These parameters form the camera matrix. The image plane is digitized and forms the (u,v) pixel array, so the characteristics of the optical system define how the plane's coordinates transform to the (u,v) pixel coordinates.

So far, we made a short report of how the pixel location for a star in the FOV is determined. When it comes to the image processing, we need to perform certain calculations regarding the corresponding brightness of the image. In astronomy, the brightness, or magnitude, of a celestial body is defined in a logarithmic scale and is often measured in a specific wavelength, spectrum or photometric band. Typically, magnitudes are measured in the visual or near-infrared spectrum, wavelengths from hundreds of nanometers up to micrometers. Since we have a logarithmic scale, the closer to zero in absolute scale a star is, the brighter it is.

The magnitudes of stars in the FOV corresponds to a number of electrons. The magnitude is related to solar irradiance, which is defined as the power per unit area emitted by a star. Once the electron count is calculated through a series of steps, which are considered superfluous for the needs of this thesis, we can determine the area of pixels taken up by a star in the FOV. The electron count can be described by a two-dimensional Gaussian function, which provides a more intuitive way in order to determine the spread of a star. The standard deviation of the Gaussian is determined by sensor and optic parameters and is kept constant for each star regardless of brightness.

# 2.1.4 Algorithms

Although star trackers might differ in quite a few parameters, they mostly follow the same process flow. The entire process can be divided into four primary sub-processes that cooperate to provide the system with the information needed for attitude determination.

Figure 2.4: High level process flow of an ADCS.

## **Centroid Extraction**

The first step of the algorithm is to extract centroid positions of possible stars on the image plane. This actually happens in three steps, thresholding, clustering and finally centroiding. This thesis puts a strong focus on the first two steps proposing two optimised algorithms for hardware implementation that will be discussed in detail on Chapter 3. Some of the most common algorithms that are used for centroid extraction are the center of gravity and the fast gaussian fitting.

#### **Distortion Correction**

Distortion correction is the process where lens distortion correction is done in order to convert the image plane coordinates to the corresponding three-dimensional sensor body coordinates in Cartesian form. Unfortunately, there is no perfect lens, so it is inevitable to have some distortion to the images due to variations in image magnification. Although distortion can be irregular or follow many patters, the most commonly encountered distortions are radially symmetric and can be classified as either barrel distortions or pincushion distortions[32]. Figure 2.5 illustrates these two types of radial distortions. In barrel distortion, image magnification decreases with distance from the optical axis, whereas in pincushion distortion it increases. Radial distortion can be corrected using Brown's distortion model, also known as the Brown-Conrady model. This model utilizes a series of polynomial coefficients that are often provided by the lens manufacturer, but in most cases, it is necessary to calibrate the camera and the lens.

#### Matching

During this step, pattern recognition algorithms are used to map constellations with known star positions in a catalogue. The algorithms are of the lost-in-space type or the recursive type, wich runs off of some prior position knowledge. One of the most widely known star catalogue is the Hipparcos catalogue of nearby stars. The Hipparcos catalogue was obtained from the European Space Agency's Hipparcos astrometric mission that operated from November 1989 to March 1993 viewing the celestial sphere. The mission returned very high quality star astrometric and photometric data, specifically high precision data on 118,218 stars. It is important to mention that this process is of

Figure 2.5: Types of radial distortion [4].

great complexity and software optimisations are required to improve its processing time. Lately, new techniques have been proposed to accelerate this process using neural network models.

# Attitude Acquisition

The final step is the attitude acquisition. Once the centroids have been extracted an matched to known ECI coordinates, they can be used to determine the satellite's attitude. There are many different types of attitude determination algorithms for star trackers in use today. Some of them which are commonly used are the TRIAD algorithm as well as the Quaternion Estimator (QUEST) algorithm.

# 2.1.5 Commercially Available Star Trackers

Indicatively, a list of commercially available star trackers with high performance standards is presented as follows in table 2.1.

Table 2.1: Table of commercially available star trackers

| Manufacturer         | Redwire                                | Vectronic<br>Aerospace GmbH            | Terma                               | Ball         |

|----------------------|----------------------------------------|----------------------------------------|-------------------------------------|--------------|

| Model                | SpectraTRAC                            | VST-68M                                | HE-5AS                              | HAST         |

| FOV                  | N/A                                    | $14^{\circ} \times 14^{\circ}$         | N/A                                 | 8° × 8°      |

| Update Rate          | 4 Hz                                   | 5 Hz                                   | 4 Hz                                | configurable |

| Accuracy (x, y axis) | 10 arcsec                              | 5 arcsec                               | <1 arcsec                           | <0.5 arcsec  |

| Accuracy<br>(z axis) | 27 arcsec                              | 30 arcsec                              | <5 arcsec                           | N/A          |

| Mass                 | 0.475  kg                              | $0.470~\mathrm{kg}$                    | 1 kg                                | N/A          |

| Volume               | $120 \times 61$ $\times 61 \text{ mm}$ | $60 \times 60$ $\times 138 \text{ mm}$ | 120 × 120<br>× 33 mm                | N/A          |

| Power                | 2.5 W                                  | 3 W                                    | 1.5 W (camera)<br>5.5 W (processor) | N/A          |

| Temperature          | $-30^{o}\text{C} - 55^{o}\text{C}$     | $-20^{o}\text{C} - 65^{o}\text{C}$     | $-40^{o}C - 70^{o}C$                | N/A          |

# 2.2 Related Work