### National Technical University of Athens School of Electrical & Computer Engineering Division of Communication, Electronic and Information Engineering

# Hardware Acceleration Techniques for Computation and Data Intensive Machine Learning and Bioinformatic Applications

Ph.D. Thesis

Konstantina I. Koliogeorgi

Athens, May 2023

This Ph.D. thesis was cofinanced by the E.C. funded projects H2020 AEGLE and H2020 EVOLVE.

The content of this Ph.D. Thesis does not reflect the official opinion of the National Technical University of Athens. Responsibility for the information and views expressed in this thesis lies entirely with the author.

Content that is reused from publications that the author has (co-)authored (excerpts, figures, tables, etc.) is under copyright with the respective paper publishers (IEEE, ACM, Springer etc) and is cited accordingly in the current text. Content that is reused from third-party publications appears with the appropriate copyright note. Reuse of any such content by any interested party requires the publishers' prior consent, according to the applicable copyright policies. Content that has not been published before is copyrighted jointly as follows:

Copyright ©Konstantina K. Koliogeorgi, 2023 Electrical & Computer Engineer N.T.U.A. All rights reserved

National Technical University of Athens School of Electrical & Computer Engineering Division of Communication, Electronic and Information Engineering Microprocessors and Digital Systems Lab

### Hardware Acceleration Techniques for Computation and Data Intensive Machine Learning and Bioinformatic Applications

$\begin{array}{c} {\rm Ph.D.\ Thesis} \\ {\rm of} \\ {\bf Konstantina\ I.Koliogeorgi} \end{array}$

Supervisor: Prof. Dimitrios Soudris

Submitted in School of Electrical & Computer Engineering of National Technical University of Athens

Athens, May 2023

National Technical University of Athens School of Electrical & Computer Engineering Division of Communication, Electronic and Information Engineering Microprocessors and Digital Systems Lab

### Hardware Acceleration Techniques for Computation and Data Intensive Machine Learning and Bioinformatic Applications

Ph.D. Thesis of Konstantina I. Koliogeorgi

${\bf Supervising\ Committee:} \quad {\rm Dimitrios\ Soudris}$

Kiamal Pekmestzi Georgi Gaydadjiev

Approved by the advisory committee on May 2, 2023.

Dimitrios Soudris Kiamal Pekmestzi Georgi Gaydadjiev Professor N.T.U.A Professor N.T.U.A Professor TU Delft

Sotirios Xydis Dionisios Pnevmatikatos Asst. Professor N.T.U.A Professor N.T.U.A

Leonidas Alexopoulos Onur Mutlu Professor N.T.U.A Professor E.T.H.Z

Athens, May 2023

Εθνικό Μετσόβιο Πολυτεχνείο Σχολή Ηλεκτρολόγων Μηχανικών & Μηχανικών Υπολογιστών Τομέας Επικοινωνιών, Ηλεκτρονικής και Συστημάτων Πληροφορικής Εργατήριο Μικροϋπολογιστών

Τεχνικές Επιτάχυνσης σε Hardware για εφαρμογές Τεχνητής Νοημοσύνης και Βιοπληροφορικής απαιτητικές σε Υπολογισμούς και Δεδομένα

Διδακτορική Διατριβή της Κωνσταντίνας Ι. Κολιογεώργη

Επιβλέπων: Καθ. Δημήτριος Σούντρης

Υποβλήθηκε στη Σχολή Ηλεκτρολόγων Μηχανικών & Μηχανικών Υπολογιστών του Εθνικού Μετσόβιου Πολυτεχνείου

Αθήνα, Μάιος 2023

Εθνικό Μετσόβιο Πολυτεχνείο Σχολή Ηλεκτρολόγων Μηχανικών & Μηχανικών Υπολογιστών Τομέας Επικοινωνιών, Ηλεκτρονικής και Συστημάτων Πληροφορικής Εργατήριο Μικροϋπολογιστών

# Τεχνικές Επιτάχυνσης σε Hardware για εφαρμογές Τεχνητής Νοημοσύνης και Βιοπληροφορικής απαιτητικές σε Υπολογισμούς και Δεδομένα

Διδακτορική Διατριβή της Κωνσταντίνας Ι. Κολιογεώργη

Συμβουλευτική Επιτροπή: Δημήτριος Σούντρης

Κιαμάλ Πεκμεστζή Georgi Gaydadjiev

Εγκρίθηκε από την επταμελή εξεταστική επιτροπή την  $2^{\eta}$  Μαΐου 2022.

Δημήτριος Σούντρης Κιαμάλ Πεκμεστζή Georgi Gaydajiev Καθηγητής ΕΜΠ Καθηγητής ΕΜΠ Professor TU Delft

Σωτήριος Ξύδης Διονύσιος Πνευματικάτος Επ.Καθηγητής Ε.Μ.Π. Καθηγητής Ε.Μ.Π.

. . . . . . . . . . . . .

Λεωνίδας Αλεξόπουλος  $\begin{array}{ccc} \text{Onur Mutlu} \\ \text{Καθηγητής E.M.} \Pi \end{array}$

Αθήνα, Μάιος 2023

.....

Κωνσταντίνα Ι. Κολιογεώργη Διδάκτωρ Ηλεκτρολόγος Μηχανικός και Μηχανικός Υπολογιστών Ε.Μ.Π.

Copyright ©Κωνσταντίνα Ι. Κολιογεώργη, 2023. Με επιφύλαξη παντώς δικαιώματος. All rights reserved.

Απαγορεύεται η αντιγραφή, αποθήκευση και διανομή της παρούσας εργασίας, εξ ολοκλήρου ή τμήματος αυτής, για εμπορικό σκοπό. Επιτρέπεται η ανατύπωση, αποθήκευση και διανομή για σκοπό μη κερδοσκοπικό, εκπαιδευτικής ή ερευνητικής φύσης, υπό την προϋπόθεση να αναφέρεται η πηγή προέλευσης και να διατηρείται το παρόν μήνυμα. Ερωτήματα που αφορούν τη χρήση της εργασίας για κερδοσκοπικό σκοπό πρέπει να απευθύνονται προς τον συγγραφέα.

Οι απόψεις και τα συμπεράσματα που περιέχονται σε αυτό το έγγραφο εκφράζουν τον συγγραφέα και δεν πρέπει να ερμηνευθεί ότι αντιπροσωπεύουν τις επίσημες θέσεις του Εθνικού Μετσόβιου Πολυτεχνείου.

### **Abstract**

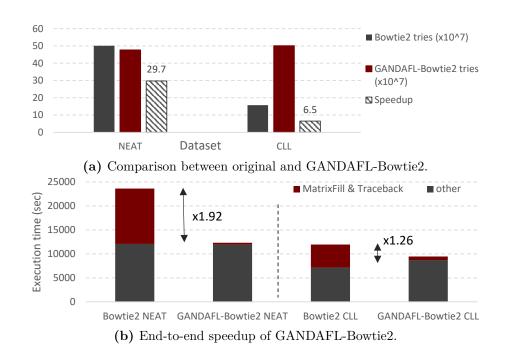

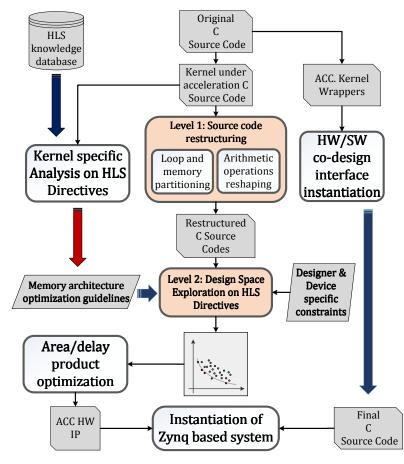

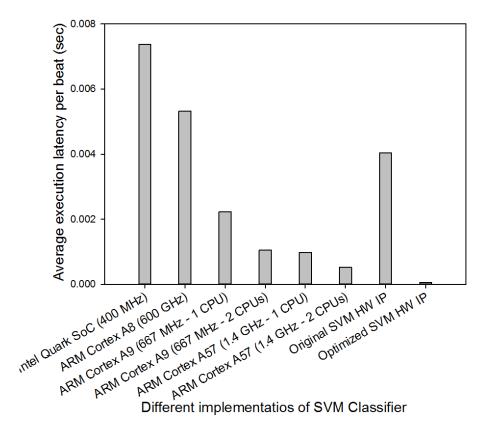

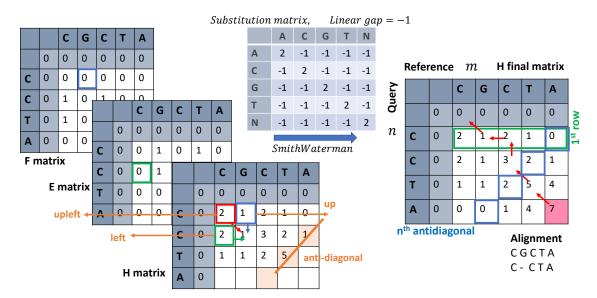

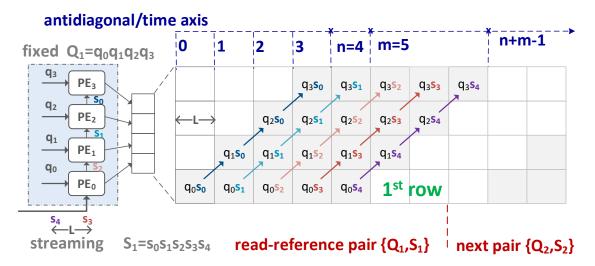

In this thesis, we focus on the hardware acceleration of two representative applications of modern healthcare: a ML-based prediction analysis and Read Alignment of genomic data. Both fields experience an intense growth in the latest decades and generate an immense amount of raw data. Creating value and making decisions based on these data have proved to be a challenging task as both the datasets as well as the computational intensity of the algorithms continue to escalate. To cope with this issue, High Performance techniques such as hardware acceleration have been examined. There is a great surge of works that leverage different programming models and frameworks to develop efficient FPGA-based accelerators, thanks to the bit-level customization capabilities of the devices. However, the frameworks available for programming such devices cannot always straightforwardly fully exploit the acceleration prospects of the applications. Furthermore, in complex applications existing solutions are characterized by a narrow view on real integration aspects, such as system wide communication and accelerator call overheads. In the current research work, the core contribution is based on the delivery of efficient solutions through strategic exploration of the design space and the synergy of hardware and software code modifications. The first application that this thesis examines is efficient hardware acceleration of Support Vector Machine (SVM) classifiers. SVMs have played a crucial role in providing data fusion and high accuracy classification solutions for various, complex, non-linear problems. In this thesis, we explore an application that SVM hardware co-processors perform classification for ECG signal arrhythmia detection. The proposed methodology for accelerating the SVM has been implemented as a framework on top of the state-of-art Vivado High-Level Synthesis (HLS) tool. We propose a systematic two-level approach for SVM acceleration, which first optimizes the global structure of the original SVM's behavioral description to assist the tool in infering the inherent data- and instruction-level parallelism of the algorithm. The second level of optimization further refines the design through a targeted design exploration that matches the accelerator's memory architecture to its computation and memory access patterns. In the second part of the thesis, we study the effect of acceleration techniques on one of the major bottlenecks of a typical genomic pipeline, which is short read alignment. In our study we perform extensive profiling on a popular aligner and identify the bottleneck within alignment as the string-matching algorithm Smith-Waterman. Our approach is to provide a dataflow implementation for this task that targets FPGA devices by taking into account the implications of integrating the accelerator in the original software tool. We therefore present GANDAFL, a novel genome alignment dataflow architecture for Smith-Waterman Matrix-fill and Traceback stages to perform high throughput

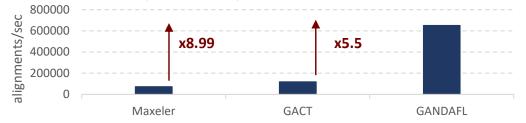

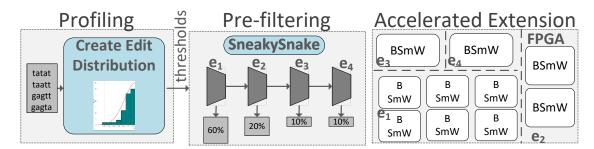

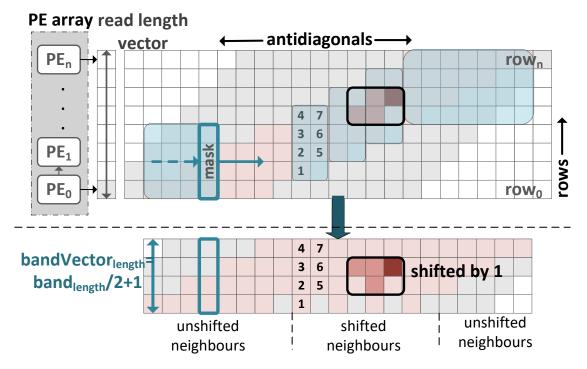

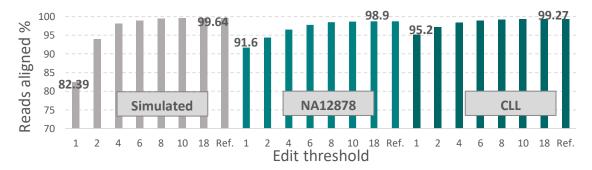

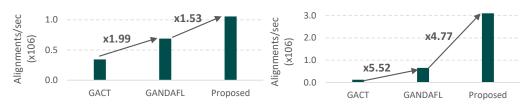

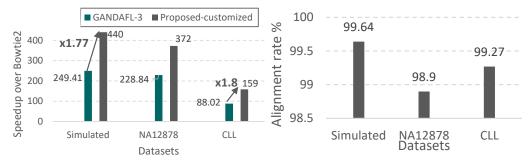

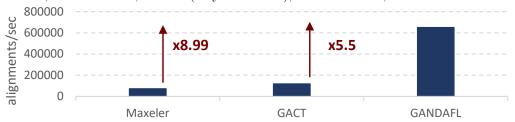

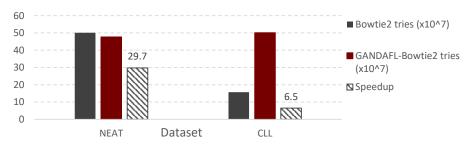

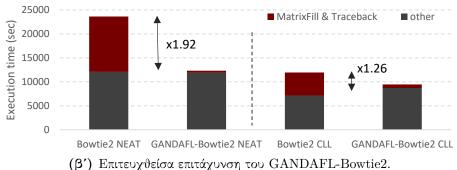

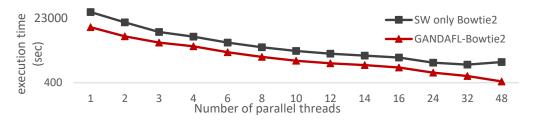

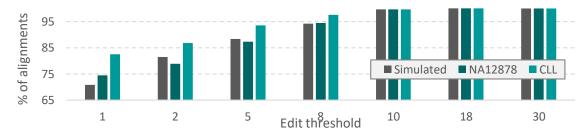

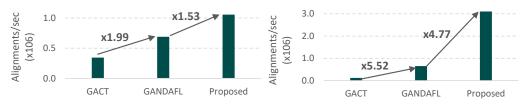

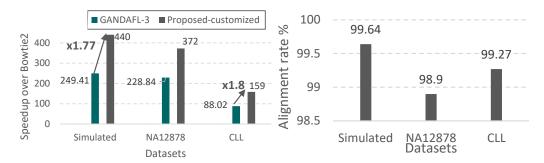

short-read alignment on Next Generation Sequencing data. We then propose a radical software restructuring to widely-used Bowtie2 aligner that implements an aggregationbatching strategy and feeds the accelerator in high-throughput streaming fashion with minimized transfer and call overheads. The standalone solution delivers up to  $\times 116$  and ×2 speedup over state-of-the-art software and hardware accelerators respectively and GANDAFL-enhanced Bowtie2 aligner delivers a  $\times 1.9$  speedup. We also examine an alternative approach to accelerating short read alignment. We introduce a high throughput alignment system that combines Banded SmithWaterman accelerators and pre-filtering for alignment optimization by introducing a profile-driven accelerator methology. Extensive profiling of genomic datasets reveals low edit thresholds that can be leveraged by a heuristic of SmithWaterman, i.e. Banded SmithWaterman, to create resource-efficient accelerators that are customized to the edit profile of the input. We therefore design and deliver a highly optimized dataflow implementation for Banded Smith-Waterman seedextension targeting FPGA devices, which is leveraged within a multi-dataflow accelerated system. The multi-dataflow system covers the full range of edits and therefore achieves both high throughput as well as high accuracy alignments. The evaluation shows that the proposed Banded Smith-Waterman accelerator delivers a  $\times 34$  speedup over stateof-the-art software aligners and ×1.53 and ×3 over state-of-the-art dataflow and RTL SmithWaterman accelerators respectively. The multi-dataflow system delivers average speedups of ×1.8 over state-of-art multi-accelerator FPGA solutions that employ generic and input-agnostic accelerators.

**Keywords:** FPGA Acceleration, High Level Synthesis, Design Space Exploration, Code transformation, Machine Learning, Next-Generation Sequencing, Short Read Alignment, SW/HW Co-design, Dataflow computing

### Περίληψη

Σε αυτή τη διατριβή επικεντρωνόμαστε στην υλοποίηση υλικού επιτάχυνσης για δύο αντιπροσωπευτικές εφαρμογές του σύγχρονου τομέα της υγείας: μια ανάλυση πρόβλεψης που βασίζεται στη μηχανική μάθηση και η ευθυγράμμιση ανάγνωσης γονιδιωματικών δεδομένων. Και οι δύο τομείς βιώνουν έντονη ανάπτυξη τις τελευταίες δεκαετίες και παράγουν έναν τεράστιο όγκο ακατέργαστων δεδομένων, πλούσιο σε πληροφορία. Η ερμηνεία και η λήψη αποφάσεων βασισμένων σε αυτά τα δεδομένα έχουν αποδειχθεί δύσχολες εργασίες καθώς τα δεδομένα και η υπολογιστική πολυπλοκότητα των αλγορίθμων αυξάνονται εκθετικά. Για να αντιμετωπιστεί αυτό το πρόβλημα, έχουν εξεταστεί τεχνικές υψηλής απόδοσης όπως η επιτάχυνση σε hardware. Υπάρχει μια πληθώρα ερευνητικών εργασιών που αξιοποιούν διαφορετικά μοντέλα προγραμματισμού για να αναπτύξουν αποτελεσματικούς επιταχυντές βασισμένους σε FPGA, χάρη στην ευελιξία προγραμματισμού τους σε επίπεδο βιτ. Ωστόσο, τα διαθέσιμα μοντέλα προγραμματισμού για την προγραμματισμό τέτοιων συσχευών δεν μπορούν πάντα να εχμεταλλευτούν πλήρως τις προοπτιχές επιτάχυνσης των εφαρμογών με απλό τρόπο. Επιπλέον, σε πολύπλοκες εφαρμογές, οι υπάρχουσες λύσεις χαραχτηρίζονται από μια περιορισμένη οπτική στην ενσωμάτωση των επιταχυντών σε ένα ρεαλιστικό σύστημα, όπως η επικοινωνία σε επίπεδο συστήματος και οι πρόσθετοι χρόνοι κλήσης των επιταχυντών. Στο τρέχον διδακτορικό, η κύρια συνεισφορά βασίζεται στην παροχή αποτελεσματικών λύσεων μέσω της στρατηγικής εξερεύνησης του χώρου σχεδιασμού και της συνέργιας βελτιστοποιήσεων του κώδικα τόσο σε επίπεδο υλικού όσο και λογισμιχού.

Η πρώτη εφαρμογή που εξετάζεται σε αυτή τη διατριβή είναι η αποδοτική επιτάχυνση υλικού των ταξινομητών Συππορτ έςτορ Μαςηινε (SVM). Σε αυτήν τη διατριβή, εξετάζουμε μια εφαρμογή στην οποία οι επιταχυντές υλικού SVM εκτελούν ταξινόμηση για την ανίχνευση αρρυθμιών σήματος ECG. Η προτεινόμενη μεθοδολογία για την επιτάχυνση του SVM έχει υλοποιηθεί χρησιμοποιώντας το εργαλείο Vivado High-Level Synthesis (HLS). Προτείνουμε μια συστηματική προσέγγιση δύο επιπέδων για την επιτάχυνση του SVM, η οποία πρώτα βελτιστοποιεί τη γενική δομή της αρχικής περιγραφής συμπεριφοράς του SVM για να βοηθήσει το εργαλείο να αναγνωρίσει τον εγγενμή παραλληλισμό σε επίπεδο δεδομένων και εντολών του αλγορίθμου. Το δεύτερο επίπεδο βελτιστοποίησης βελτιώνει επιπρόσθετα το σχεδιασμό μέσω μιας στρατηγικής εξερεύνησης του χώρου σχεδιασμού που σχεδιάζει τη μνήμη του επιταχυντή βάσει των μοτίβων υπολογισμού και πρόσβασης στη μνήμη του.

Στο δεύτερο μέρος της διπλωματικής εργασίας, μελετάμε την επίδραση των τεχνικών ε-

πιτάχυνσης σε ένα από τα πιο υπολογιστικά απαιτητικά κομμάτια της επεξεργασίας γονιδιώματος, που είναι η ευθυγράμμιση ακολουθιών  $\Delta {

m NA}$  στο ανθρώπινο γονιδίωμα. Εκτελούμε ανάλυση της απόδοσης ενός εργαλείου αλληλούχισης (το Bowtie2) και εντοπίζουμε τον αλγόριθμο Smith-Waterman ως το πιο χρονοβόρο χομμάτι. Η προσέγγισή μας είναι να παρέχουμε μια υλοποίηση ροής δεδομένων που στοχεύει συσκευές FPGA λαμβάνοντας υπόψη τις συνέπειες της ενσωμάτωσης του επιταχυντή στο εργαλείο αλληλούχισης και επομένως σε ένα πραγματικό σύστημα. Προτείνουμε το GANDAFL, μια νέα αρχιτεκτονική ροής δεδομένων ευθυγράμμισης γονιδιώματος για τον Smith-Waterman για την εκτέλεση ευθυγράμμισης υψηλής απόδοσης σε δεδομένα αλληλουχίας επόμενης γενιάς. Στη συνέχεια, προτείνουμε μια ριζική αναδιάρθρωση του κώδικα του Bowtie2 η οποία ομαδοποιεί πολλά μεμονωμένα αιτήματα αλληλούχισης και τα τροφοδοτεί στον επιταχυντή με υψηλής ρυθμό απόδοσης ελαχιστοποιώντας έξοδα μεταφοράς και κλήσεων. Ο επιταχυντής προσφέρει έως και 116 και 2 φορές επιτάχυνση αντίστοιχα σε σύγκριση με πρόσφατους επιταχυντές λογισμικού και υλικού, αντίστοιχα, και η βελτιωμένη με GANDAFL ευθυγράμμιση Bowtie2 προσφέρει επιτάχυνση 1,9 επί του συνολικού συστήματος. Τέλος εξετάζουμε μια εναλλακτική προσέγγιση, η οποία συνδυάζει μια ευριστική υλοποίηση του Smith-Waterman και ένα στάδιο φιλτραρίσματος των αρχικών δεδομένων. Μελέτη των δεδομένων εισόδου υποδεικνύει ότι η αλληλούχιση συνήθως είναι ακριβής και εντοπίζεται μικρός αριθμός διαφοροποιήσεων από το ανθρώπινο γονιδίωμα. Αυτό μειώνει το χώρο αναζήτησης των λύσεων και μας επιτρέπει να χρησιμοποιήσουμε τον ευριστικό Banded Smith Waterman ο οποίος επιτελεί την ίδια λειτουργία, εντοπίζει λιγότερες διαφοροποιήσεις και καταναλώνει λιγότερους πόρους στο υλικό. Προτείνουμε λοιπόν ένα σύστημα που πλέον αποτελείται από πολλούς επιταχυντές και καλύπτει έως έναν αριθμό διαφοροποιήσεων ενώ εντοπίζει πλέον τις αλληλουχίσεις με ταχύτερο ρυθμό. Το προτεινόμενο σύστημα αποδίδει επιτάχυνση έως 34 φορές σε σχέση με λογισμικά ενώ είναι έως 3 φορές ταχύτερο από σύγχρονους επιταχυντές.

**Λέξεις Κλειδιά:** Επιτάχυνση Υλιχού, Γλώσσες Σύνθεσης Υψηλού Επιπέδου, Μετασχηματισμός Κώδικα, Διερεύνηση Χώρου Σχεδίασης, Μηχανική μάθηση, Αλληλούχιση γονιδιώματος, Next-Generation Sequencing, Short Read Alignment, SW/HW Co-design, Dataflow computing

### Acknowledgements

This section of my thesis is dedicated to expressing my gratitude to all people that have contributed to my efforts and completion of my Ph.D. studies. It is very challenging to capture the thoughts and feelings that occur upon reflecting over the past years. I can only hope that the next words, despite their simplicity and lack of originality, convey the sincerity and depth of my gratitude.

To begin with, I would like to express my graditude for being a member of the Microprocessors and Digital Systems Lab (MicroLab) of N.T.U.A.. First and foremost, I would like to thank my advisor Professor Dimitrios Soudris for trusting me and offering me the opportunity to pursue my Ph.D. degree in such an inspiring and productive environment as is MicroLab. His constant technical and moral support and genuine interest has encouraged me and guided me through all steps of my studies. The lessons learned during this mentorship will stay close to me and continue to help me cope with the new challenges in my life. Next I would like to specially acknowledge the contribution of Sotirios Xydis, with whom I closely collaborated since my diploma thesis. His insightful remarks on my research and our intriguing discussions were inspiring and crucial for the completion of my thesis. Hopefully his love for research and work ethics are reflected on my work from now on.

My Ph.D. studies would not be the same without the Ph.D. candidates, researchers and administrative staff that comprise MicroLab. I would like to thank all of them for being part of one of the most challenging accomplishments of my life and some of my fondest memories. I consider them my friends and they have trully made MicroLab feel like a second home. With that said, I would like to specially thank Dimosthenis Masouros, Georgios Zervakis, Giannis Stratakos, Haris Marantos, Vasilis Leon, Manolis Katsaragakis, Giannis Oroutzoglou, Achilleas Tzenetopoulos, Aggelos Ferikoglou, Christos Lamprakos, George Armeniakos, George Lentaris and Zefi Skini.

I could not omit to thank all of my friends that stood by me throughout these years. They have patiently supported me through hard work and deadlines, encouraged me to reach my goals and filled my life outside Microlab with beautiful moments. I am sorry for missing out on some of them and grateful for your understanding and love. A special thanks to Anastasia, Katerina, Christos, Konstantina M, Konstantina S, Sotiria Fytraki, Sotiria Filandra, Rania and Rafailia.

Finally, I would like to thank my parents, Ioannis and Matoula, and my sister, Roza, for their unconditional love and support. They are the ones that were closest to me during this venture, offering me their support and never losing faith in me. Without them, I would not have the perseverance to fulfil my goals.

Μαμά, Μπαμπά και Ρόζα,

$\Sigma$ ας ευχαριστώ για όλα. Ελπίζω να σας δίνω χαρές και να στέκομαι δίπλα σας όπως εσείς σε εμένα.

Κωνσταντίνα

## **Contents**

| Ab  | strac                         | t                                                                                                                                                         | xi                                     |

|-----|-------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| Αb  | strac                         | t in Greek                                                                                                                                                | xiii                                   |

| Ac  | know                          | ledgements                                                                                                                                                | χV                                     |

| Lis | t of                          | Figures                                                                                                                                                   | xxi                                    |

| Lis | t of                          | Tables                                                                                                                                                    | xxv                                    |

| 1.  | 1.1.                          | Big Data Overview and Challenges                                                                                                                          | 1<br>1<br>6<br>11                      |

| 2.  | 2.1.                          | Sis Contribution  Challenges in HLS optimization techniques and Thesis Contributions  Challenges in Short read alignment and Thesis Contributions         | 15<br>16<br>19                         |

| 3.  | 3.1.                          | High Level Synthesis on Reconfigurable platforms                                                                                                          | 25<br>25<br>25<br>27<br>30<br>30<br>31 |

| 4.  | tor I<br>4.1.<br>4.2.<br>4.3. | Exploration Framework for Efficient High-Level Synthesis of Support Vec-Machines: Case Study on ECG Arrhythmia Detection for Xilinx Zynq Soc Introduction | 35<br>36<br>39<br>41<br>41<br>42<br>45 |

### Contents

|          | 4.5. |          | Optimization Level 2: Design Space Exploration of HLS Directives Methodology for Approximate SVM | 55<br>64<br>64<br>66 |

|----------|------|----------|--------------------------------------------------------------------------------------------------|----------------------|

|          | 16   |          | mental Results                                                                                   | 67                   |

|          | 4.0. | 4.6.1.   | Experimental Set-up                                                                              | 67                   |

|          |      | 4.6.2.   | Efficiency evaluation of the proposed DSE methodology                                            | 69                   |

|          |      | 4.6.2.   | Evaluating derived SVM accelerators classifier at scale                                          | 70                   |

|          |      | 4.6.4.   | SVM based ECG arrhythmia detection                                                               | 72                   |

|          |      | 4.6.5.   | Performance Evaluation of Approximate SVM                                                        | 74                   |

| <b>E</b> | CAN  | IDAEL.   | Dataflow Acceleration for Short Read Alignment on NGS data                                       | 77                   |

| J.       |      |          | uction                                                                                           | 78                   |

|          |      |          | d Work                                                                                           | 80                   |

|          | 5.3. |          | etical Background                                                                                | 82                   |

|          | 5.5. | 5.3.1.   | NGS genomics pipeline                                                                            | 82                   |

|          |      | 5.3.2.   | 9                                                                                                | 83                   |

|          |      | 5.3.3.   |                                                                                                  | 84                   |

|          | 5.4  |          | of the Accelerator System                                                                        | 86                   |

|          | 0.4. | 5.4.1.   | Dataflow Smith-Waterman & Traceback Engine                                                       | 86                   |

|          |      | 5.4.1.   |                                                                                                  | 90                   |

|          |      | 5.4.3.   | Control and Data Flow of Engines                                                                 | 93                   |

|          |      | 5.4.4.   | Analytical Performance Model of the Accelerator                                                  | 96                   |

|          |      | 5.4.5.   | -                                                                                                | 98                   |

|          | 5.5. |          | ·                                                                                                | $10^{2}$             |

|          | 5.5. | 5.5.1.   |                                                                                                  | $10^{2}$ $10^{2}$    |

|          |      | 5.5.2.   | 3 3 1                                                                                            | $10^{2}$             |

|          | 5.6. |          | •                                                                                                | $10^{2}$             |

|          | 5.0. | 5.6.1.   |                                                                                                  | 107                  |

|          |      | 5.6.2.   | 1                                                                                                |                      |

|          |      | 0.0      |                                                                                                  | 108                  |

|          |      | 5.6.3.   | Integrated Architecture Evaluation                                                               | 109                  |

| 6.       |      |          | ren Banded Smith-Waterman acceleration for Short Read Alignment                                  |                      |

|          | 6.1. |          |                                                                                                  | 118                  |

|          | 6.2. |          | *                                                                                                | 120                  |

|          | 6.3. | _        |                                                                                                  | 124                  |

|          | 6.4. | _        |                                                                                                  | 126                  |

|          |      | 6.4.1.   | 1                                                                                                | 126                  |

|          |      | 6.4.2.   |                                                                                                  | 126                  |

|          |      | 6.4.3.   | Multi-Dataflow System Evaluation                                                                 | 129                  |

| 7.       | Con  | clusions | 5                                                                                                | 13                   |

|          | 7.1. | Summa    | ary of Ph.D. Thesis                                                                              | 131                  |

|          | 7 2  | Future   | Extensions                                                                                       | 133                  |

| 8. | Brief Description of the Proposed Frameworks in Greek                    | 137 |

|----|--------------------------------------------------------------------------|-----|

| Gr | reek Glossary                                                            | 165 |

| Ρι | ublications                                                              | 169 |

| Bi | ibliography                                                              | 173 |

| Α. | . Appendix: FPGA Acceleration of Multi-Temporal Change Detection on High |     |

|    | Resolution Images                                                        | 193 |

|    | A.1. Introduction and Background Information                             | 193 |

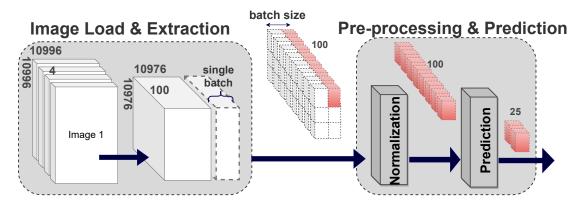

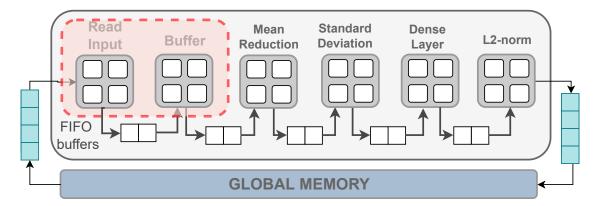

|    | A.2. Multi-temporal Prediction on High Resolution Images                 | 196 |

|    | A.2.1. Change Detection on Sentinel-2 Satellite images                   | 196 |

|    | A.2.2. Pre-processing and Prediction Model architecture                  | 197 |

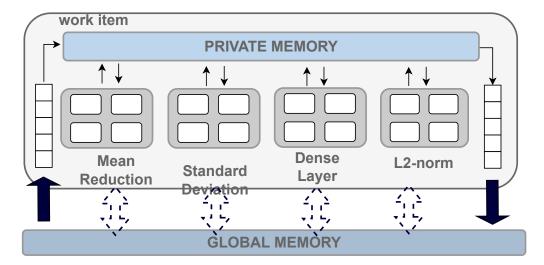

|    | A.2.3. Pre-processing and Prediction as an OpenCL kernel                 | 198 |

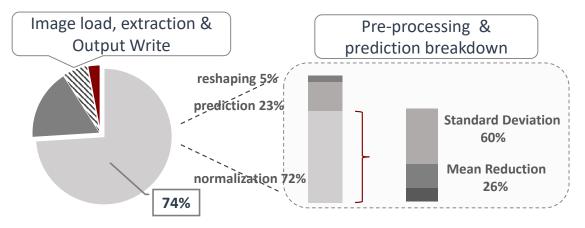

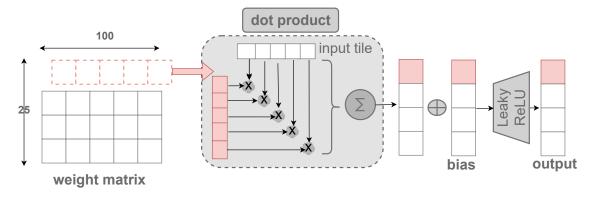

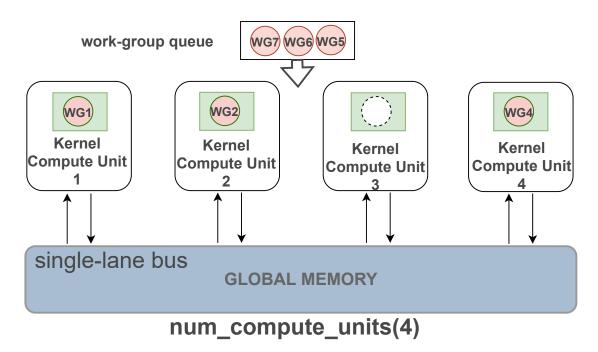

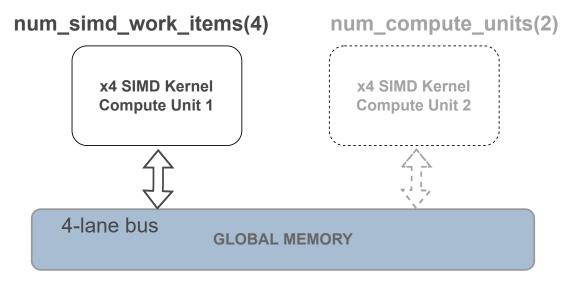

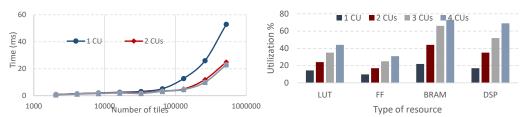

|    | A.3. Hierarchical Optimization Strategy of Model Architecture            | 199 |

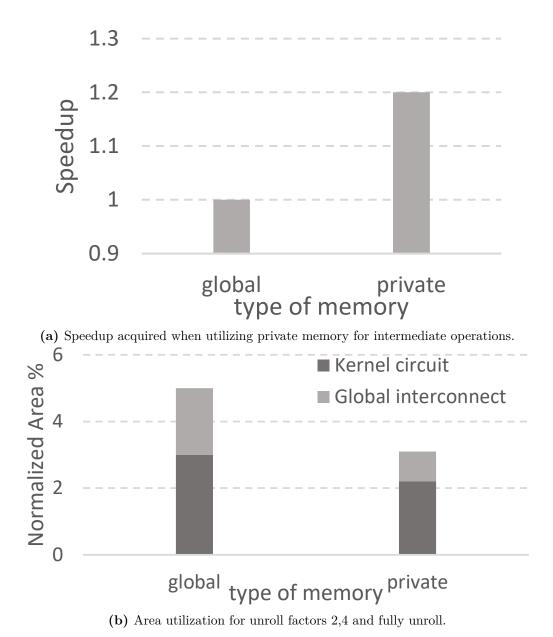

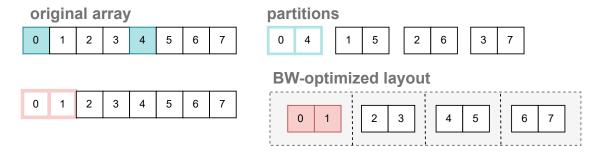

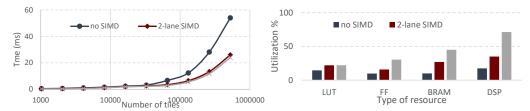

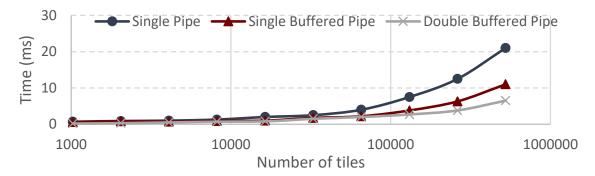

|    | A.3.1. Optimizing Baseline Architecture                                  | 199 |

|    | A.3.2. Optimizing horizontal and vertical scaling                        | 203 |

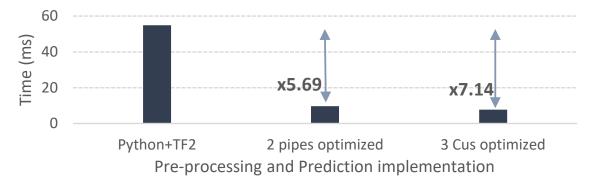

|    | A.4. Experimental Evaluation                                             |     |

|    | A.4.1. Experimental Setup                                                |     |

|    | A.4.2. Performance evaluation                                            |     |

Contents

# **List of Figures**

| 1.1.  | by Seagate withdata from IDC Global Datasphere                                                                                                  | 2   |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 1.3.  | Business Insights                                                                                                                               | 3   |

| 1.4.  | Analytics in the Healthcare domain [1]                                                                                                          | 9   |

| 2.1.  | Thesis Scope and Contribution within Healthcare HPC Domain                                                                                      | 16  |

| 3.1.  | Example of an Alignment between a reference and read sequence. It includes all possible types of mismatches among DNA bases                     | 31  |

| 3.2.  | Typical Genomic Pipeline stages. Sequencing generates short reads from a DNA sample and is followed by aligning them to a reference and calling | 0.0 |

| 3.3.  | variants                                                                                                                                        | 32  |

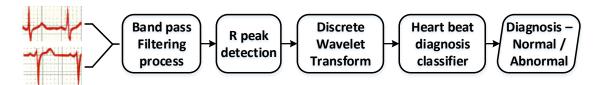

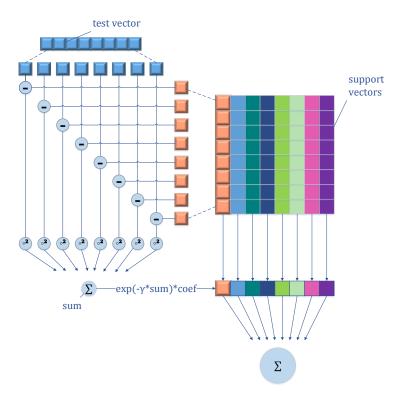

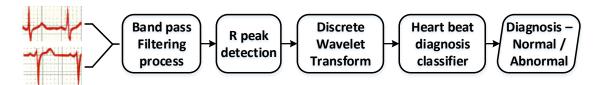

| 4.1.  | Utilized ECG analysis flow                                                                                                                      | 44  |

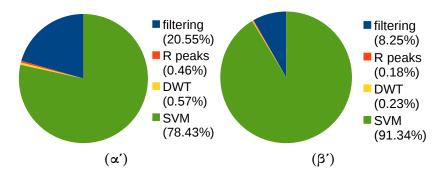

| 4.2.  | Average CPU utilization per heart beat processing (a) SVM models of moderate computational requirements, (b) SVM models of high computational   |     |

|       | requirements                                                                                                                                    | 44  |

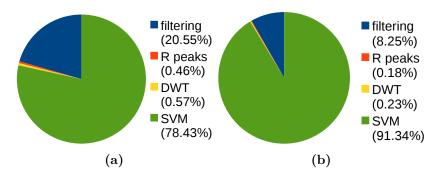

| 4.3.  | Proposed HLS based HW design methodology                                                                                                        | 46  |

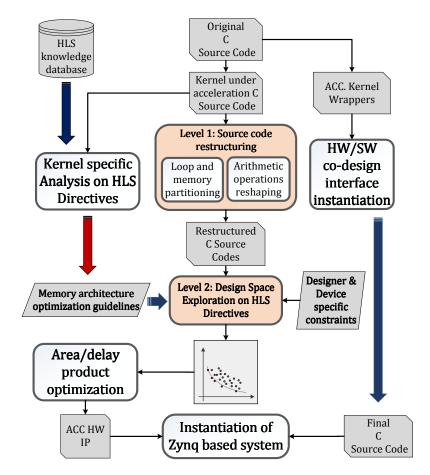

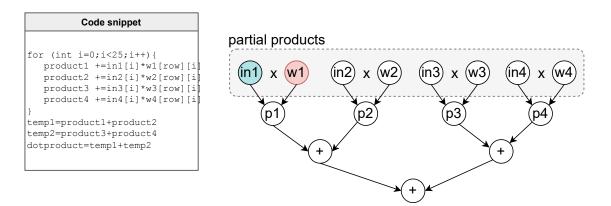

| 4.4.  | Data-level parallelism in SVM                                                                                                                   | 48  |

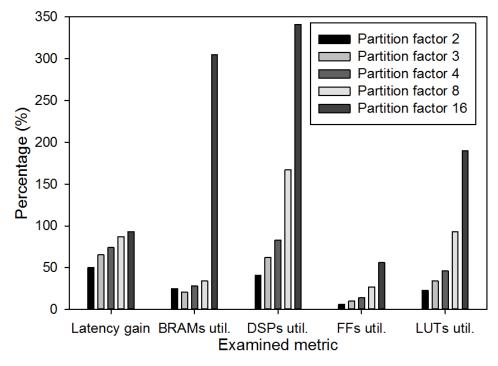

| 4.5.  | Performance and utilization for increasing number of partitions (automatic)                                                                     | 50  |

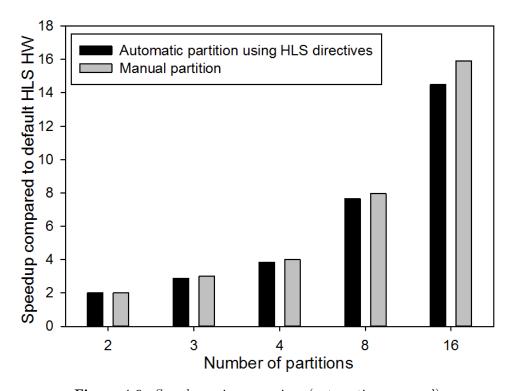

| 4.6.  | Speedup gain comparison (automatic vs manual)                                                                                                   | 51  |

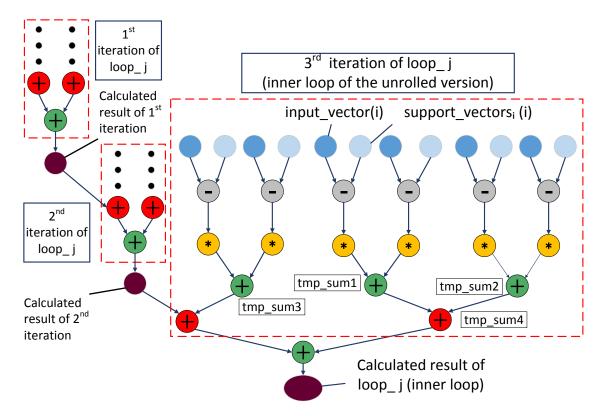

| 4.7.  | Tree based computations for manual unrolling and HLS scheduling $\dots$ .                                                                       | 54  |

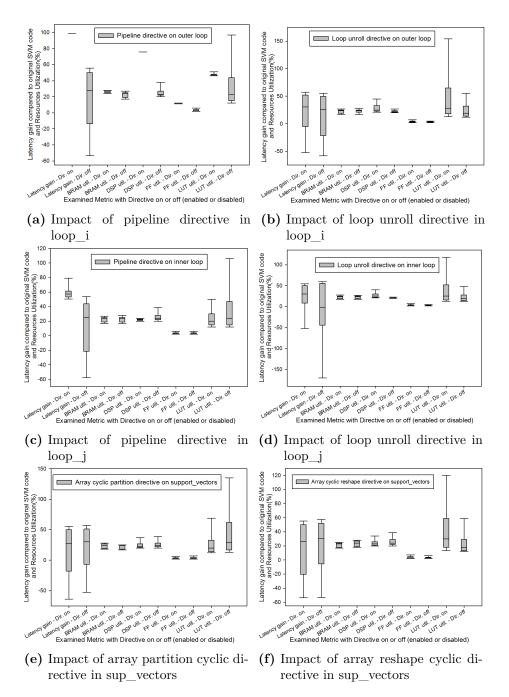

| 4.8.  | Impact of directives on SVM kernel source code                                                                                                  | 56  |

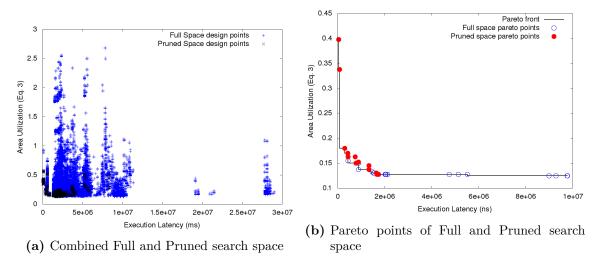

| 4.9.  | Full and Pruned Design Space                                                                                                                    | 60  |

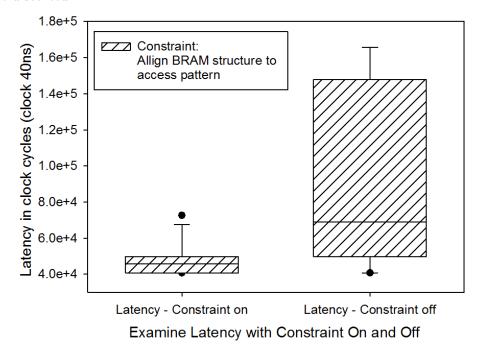

|       | Impact of loop unroll directive in loop_j $\dots \dots \dots \dots$ .                                                                           | 61  |

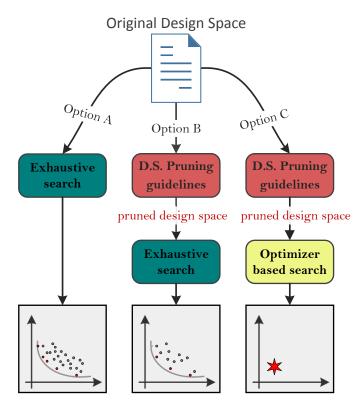

|       | DSE options provided by the proposed framework                                                                                                  | 63  |

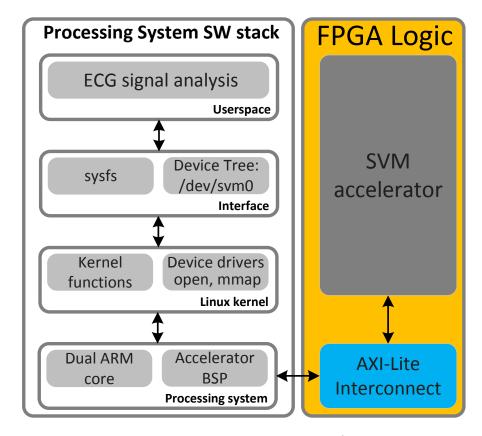

|       | Target Zynq based system HW/SW overview                                                                                                         | 68  |

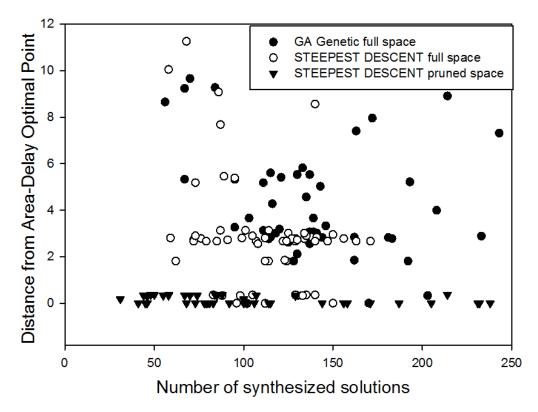

|       | Average Distance from Optimal Design for Different Optimizers                                                                                   | 70  |

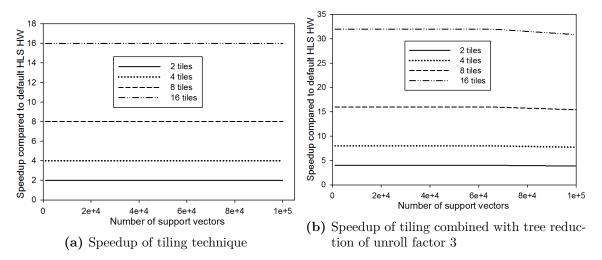

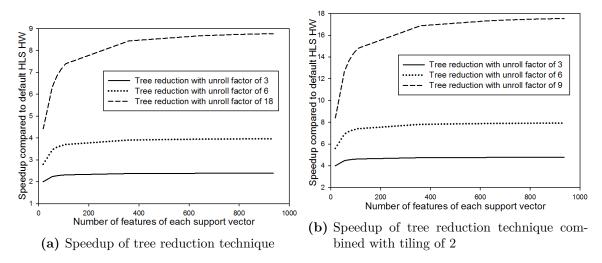

|       | Speedup of proposed techniques remains the same with scaling N_sv $\dots$                                                                       | 71  |

|       | Gain of proposed techniques remains the same with scaling D_sv $\dots$ .                                                                        | 71  |

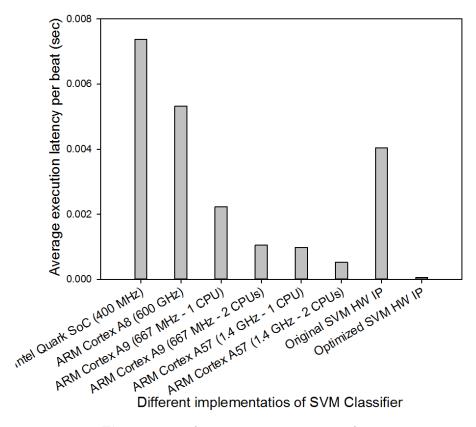

| 4.16. | Average execution time per beat                                                                                                                 | 72  |

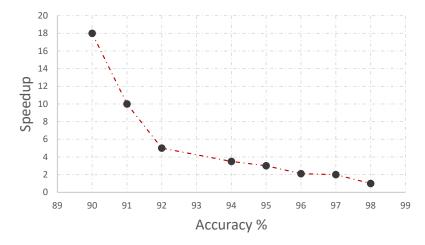

|              | Pareto Front for Accuracy and Speedup Metrics                                                                       | 74   |

|--------------|---------------------------------------------------------------------------------------------------------------------|------|

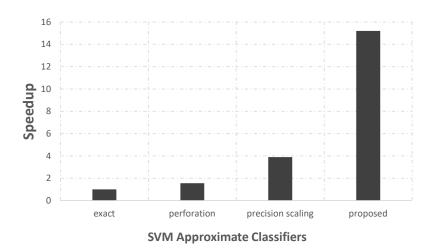

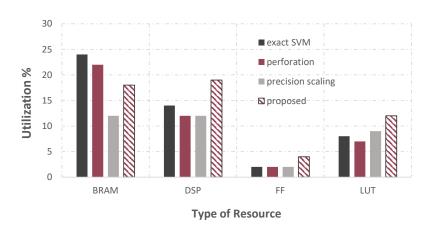

|              | Speedup for Fastest SVM of each technique                                                                           | 75   |

| 4.19.        | Resources Evaluation for Fastest SVM of each technique                                                              | 75   |

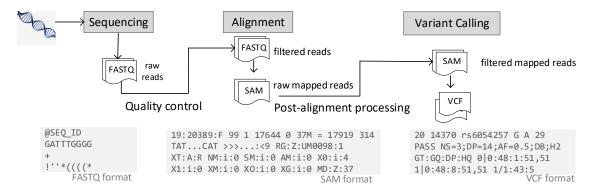

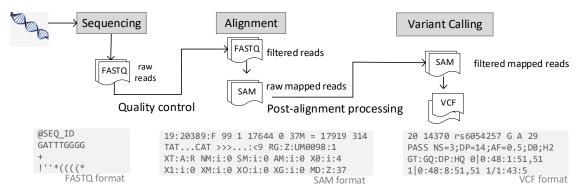

| 5.1.<br>5.2. | Typical Variant Discovery Workflow                                                                                  | 82   |

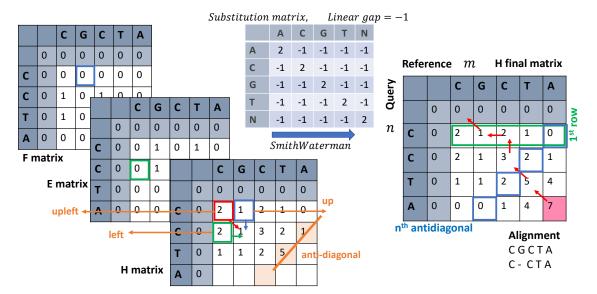

|              | Waterman with linear gap penalty scheme                                                                             | 86   |

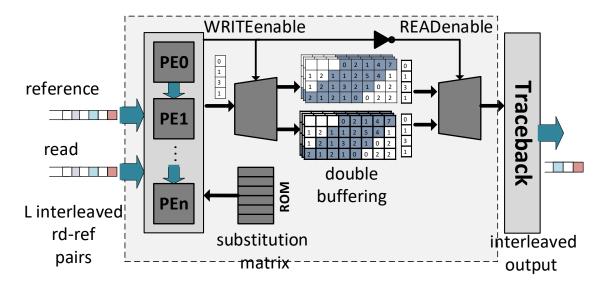

| 5.3.         | Architecture of Dataflow Engines on Chip                                                                            | 87   |

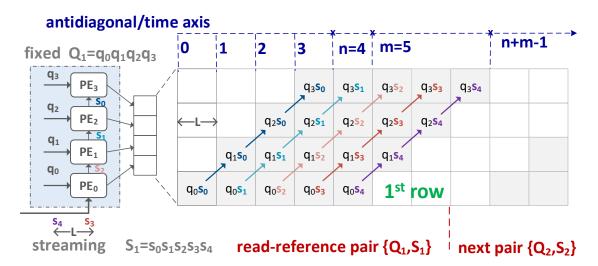

| 5.4.         | Example of computation of H matrix by PE array unfolded in time for sequence lengths $n = 4, m = 5, \ldots, \ldots$ | 88   |

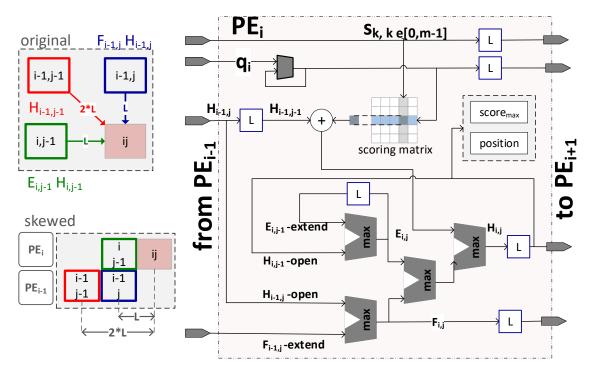

| 5.5.         | Schematic diagram of PE architecture and flow of Data between consecutive PEs                                       | 89   |

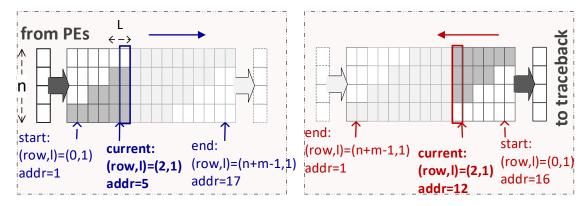

| 5.6.         | Flow of data from Matrix Fill to Traceback phase                                                                    | 90   |

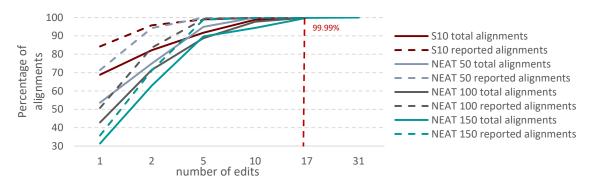

|              | Cumulative distribution of edits for all utilized datasets                                                          | 91   |

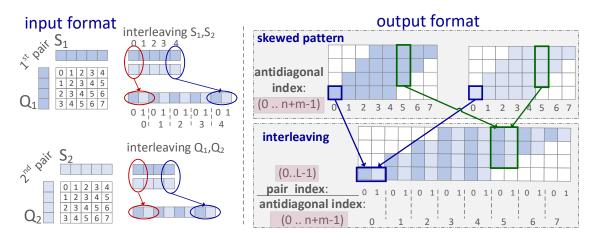

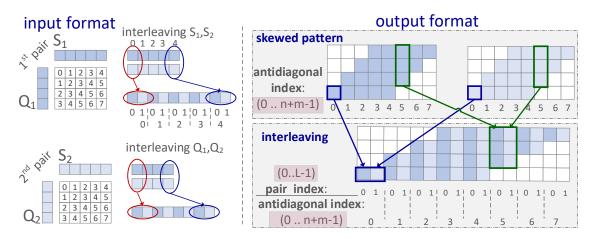

|              | Example of interleaving technique for L=2, reflected in both input and output buffers                               | 92   |

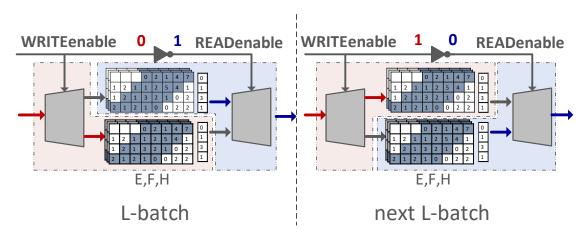

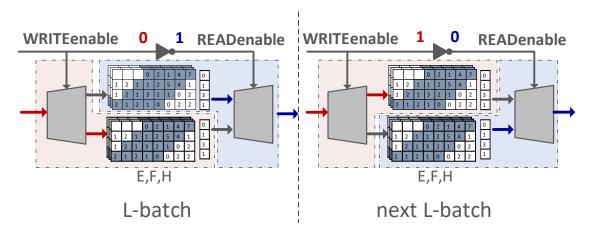

| 5.9.         | Alternate READ/WRITE operations based on Double Buffering technique                                                 | 32   |

| 5.5.         | for consecutive batch alignment tasks                                                                               | 93   |

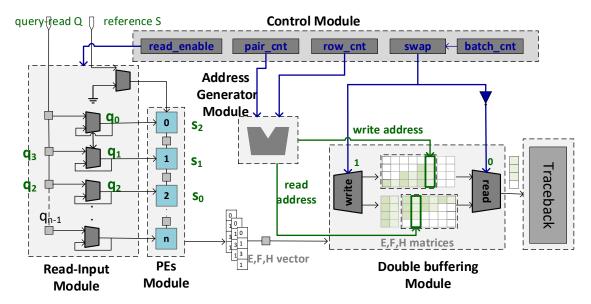

| 5 10         | Control (marked blue) and Data Flow (marked green) within the pipeline.                                             | 90   |

| 5.10.        | The state of each module for aligning 2 batches with $L=2, n=4, m=5$                                                |      |

|              | at time $\{batch\_cnt, row\_cnt, pair\_cnt\} = \{1, 2, 1\}$ is illustrated                                          | 94   |

|              | Address generation and matrix indexing applied on double buffers                                                    | 96   |

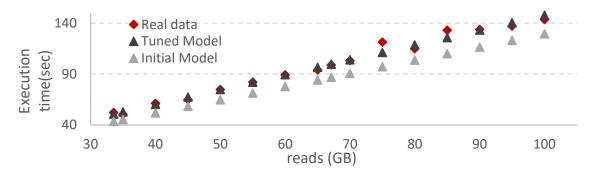

|              | Accuracy of Performance Model based on static timing analysis                                                       | 98   |

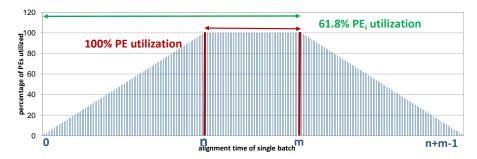

| 5.13.        | PE utilization in time                                                                                              | 99   |

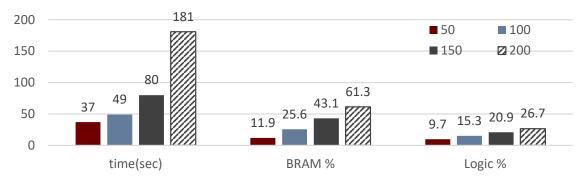

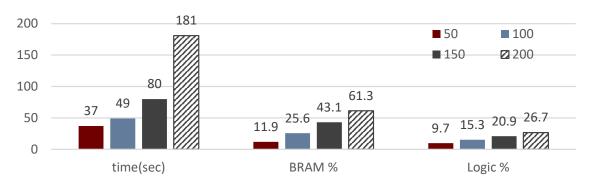

|              | Performance and Area utilization for Various Lengths of Read                                                        | 99   |

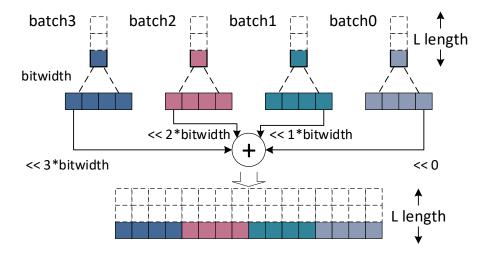

| 5.15.        | Multiplexing multiple input batches into one batch for multi-instance design                                        | .100 |

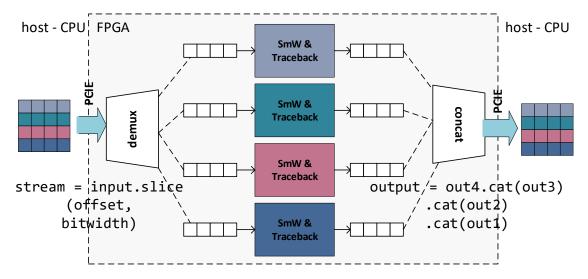

| 5.16.        | Architecture of Multiple Instances Design                                                                           | 101  |

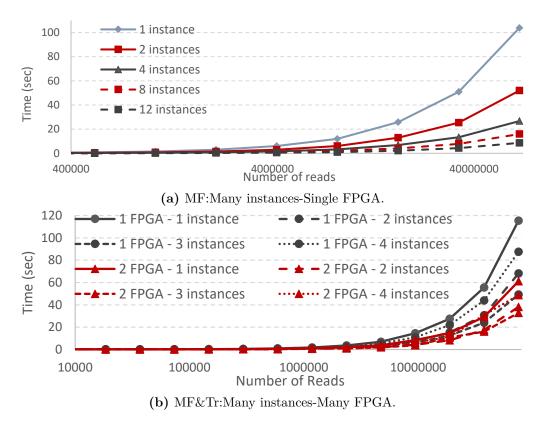

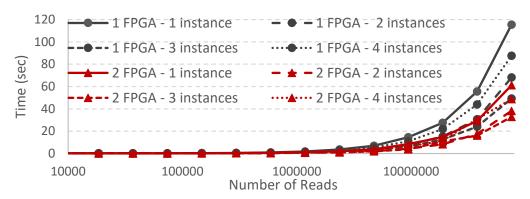

| 5.17.        | Performance scaling for Various Configurations {#instances, #FPGAs}                                                 |      |

|              | for dataflow engines for scaling number of reads (4K to 60 million in loga-                                         |      |

|              | rithmic scale), (MF=MatrixFill,Tr=Traceback)                                                                        | 103  |

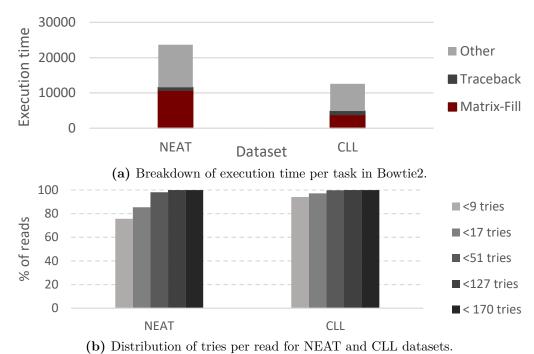

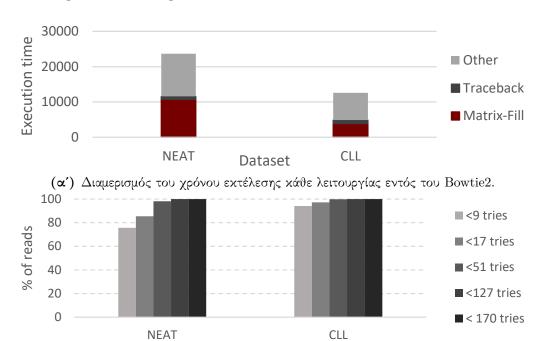

| 5.18.        | Study of Bowtie2 software for different datasets                                                                    | 104  |

| 5.19.        | Restructured Bowtie2 Three-phase Algorithm. For simplicity, only a single                                           |      |

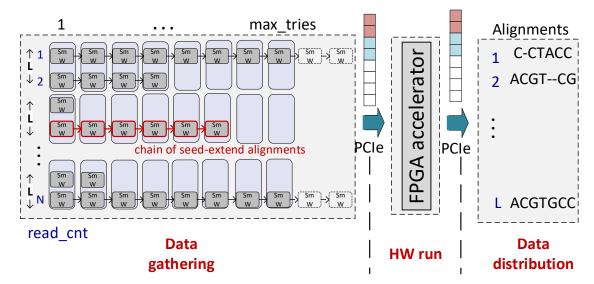

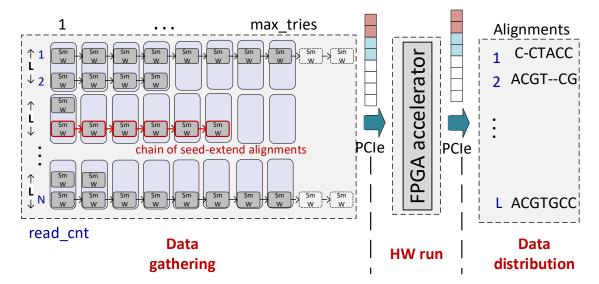

|              | batch of $L$ reads is illustrated                                                                                   | 106  |

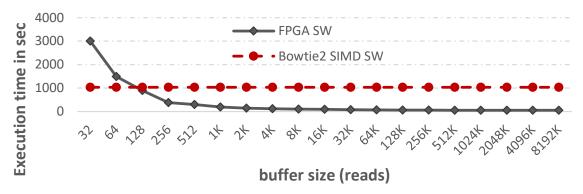

| 5.20.        | Impact of input buffer size on accelerator-call overhead and thus execution                                         |      |

|              | latency.                                                                                                            | 107  |

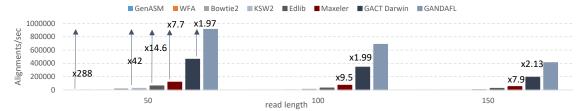

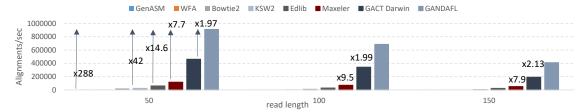

| 5.21.        | Throughput evaluation of aligners                                                                                   | 110  |

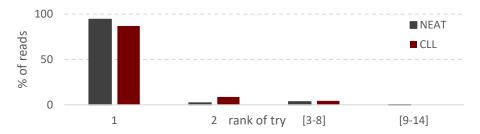

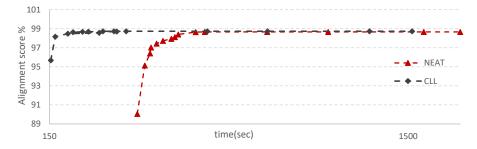

|              | Distribution of the rank of tries that delivers the reported alignment across                                       |      |

|              | reads.                                                                                                              | 111  |

| 5 23         | Tradeoff of Alignment success rate and performance for scaling number of                                            |      |

| 0.20.        | candidates per read                                                                                                 | 112  |

| 5 24         | caption                                                                                                             | 112  |

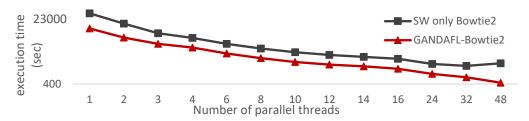

|              | Performance of Bowtie2 integrated accelerator with $max\_tries = 8$                                                 | 114  |

|              | Comparison performance for scaling number of threads while sharing two                                              | 114  |

| J.∠U.        | accelerators                                                                                                        | 114  |

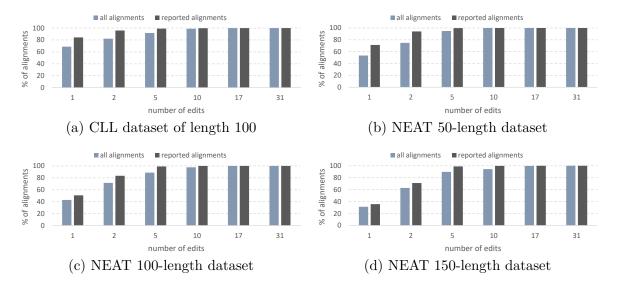

| 6.1.  | Distribution of number of edits for alignments for three different datasets.         | 121 |

|-------|--------------------------------------------------------------------------------------|-----|

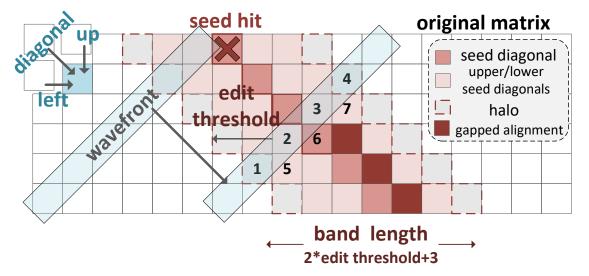

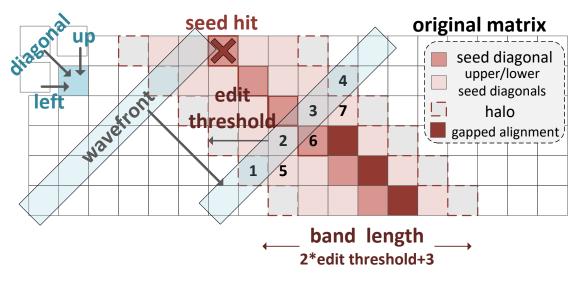

| 6.2.  | Banded SmithWaterman example for edit threshold 2                                    | 121 |

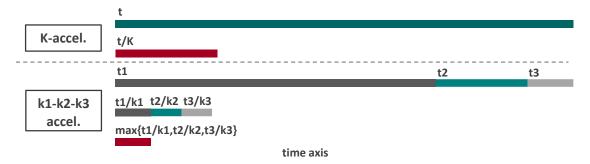

| 6.3.  | Calculation of execution time when applying $K$ generic accelerators as              |     |

|       | opposed to applying $k_1, k_2, k_3$ smaller accelerators fit to an edit distribution |     |

|       | of $70 - 20 - 10$                                                                    | 122 |

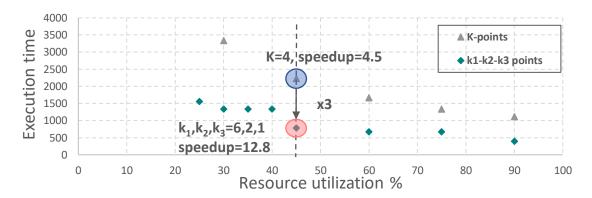

| 6.4.  | Example of applying generic accelerators as opposed to employing smaller             |     |

|       | accelerators fit to the input edit profile                                           | 122 |

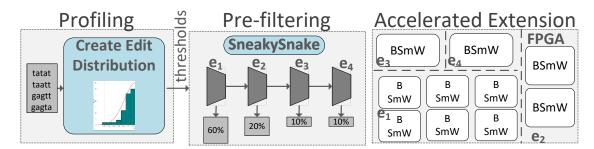

| 6.5.  | Overview of profile-driven acceleration strategy and system architecture             |     |

|       | for a distribution of $60-20-10-10\%$                                                | 123 |

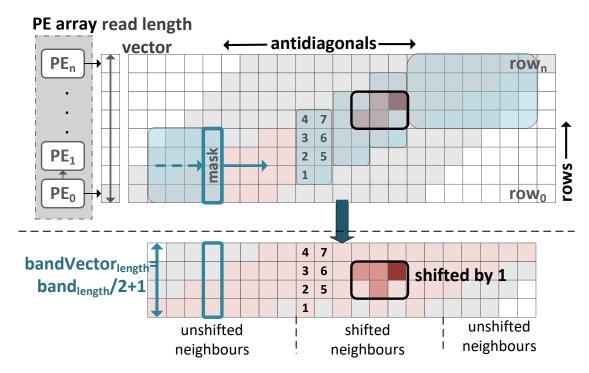

| 6.6.  | PE computation of score matrices and BRAM allocation of band elements.               | 125 |

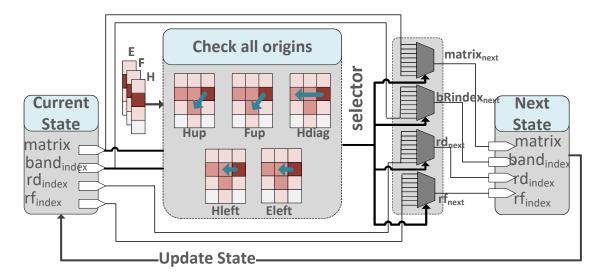

| 6.7.  | Logic Diagram of Traceback Dataflow implementation                                   | 126 |

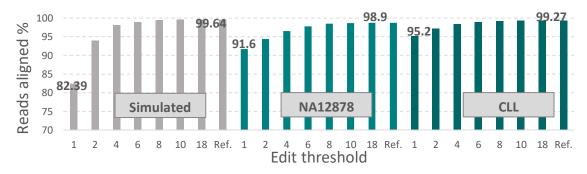

| 6.8.  | Alignment success when using SneakySnake pre-filtering and the proposed              |     |

|       | Banded Smith-Waterman accelerator for seed extension                                 | 127 |

| 6.9.  | Throughput comparison between Proposed Banded 10-edit threshold ac-                  |     |

|       | celerator and state-of-the-art SW aligners                                           | 128 |

| 6.10. | Throughput and Resource utilization efficiency evaluation for HW Smith-              |     |

|       | Waterman accelerators                                                                | 128 |

| 6.11. | Performance and accuracy evaluation of proposed customized accelerated               |     |

|       | system                                                                               | 129 |

| A.5.  | Speedup and Resources utilization when applying unroll for various factors.          | 201 |

|       | Decrease both in kernel and interconnect logic when utilizing private mem-           |     |

|       | ory for intermediate operations                                                      | 207 |

|       |                                                                                      |     |

# **List of Tables**

| 3.1. | Basic HLS Optimization Directives                                         | 28  |

|------|---------------------------------------------------------------------------|-----|

| 4.1. | Declaration of variables in Listing 1                                     | 43  |

| 4.2. | Utilized SVM model parameters                                             | 45  |

| 4.3. | HLS directives [2]                                                        | 47  |

|      | Evaluated metrics for automatic vs manual unrolling                       | 53  |

| 4.5. | Applied directives and their parameters                                   | 57  |

| 4.6. | Impact of Loop Perforation on SVM Accuracy                                | 65  |

| 4.7. | Fixed point Data types Initial Configuration in Bits                      | 66  |

| 5.1. | Input, Output and Intermediate data in the Dataflow Engines               | 91  |

| 5.2. | Formulas for Modeling Time Analysis                                       | 96  |

|      | Resource Utilization and Clock Frequency for Multiple-Instances Architec- |     |

|      | ture                                                                      | 102 |

| 5.4. | Accuracy comparison Bowtie2 vs Proposed                                   |     |

| 6.1. | Hardware Accelerators Configurations for throughput comparison            | 129 |

| 6.2. | Multi-Dataflow Configurations customized to the edit profiles of input    |     |

|      | datasets                                                                  | 130 |

### Chapter 1.

### Introduction

### 1.1. Big Data Overview and Challenges

Technological advancements and novelties have led to an exponential growth of data availability and have signaled the start of the Information or Digital age<sup>1</sup>. As technology evolved, the aggregated data initially originated from newspapers, radio and television and in later years by computers, Internet and mobile phones [3–5]. What has dramatically accelerated the establishment of this new era is the speed of data transmission and ease of accessibility by all humans thanks to new technologies.

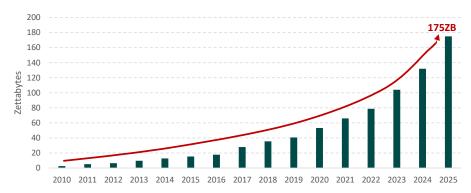

As the capacity of computer systems and devices to generate data continued to grow, the term of Biq Data was gradually adopted. It is not possible to define Big Data by the size of data it refers to, as this is relative to the storage and processing power of computer systems. As the data production and availability grows exponentially, computing systems evolve and adapt to accommodate the data curation and processing requirements. Therefore, what was once considered to be Big data, could not possibly fall into that category nowadays, that we have entered the so-called Zettabyte Era. A zettabyte is a measure of storage capacity, which equals 1000<sup>7</sup> (1,000,000,000,000,000,000,000 bytes), which is equal to a thousand exabytes or a trillion gigabytes. Fig.1.1 illustrates the exponential data growth starting from 2010 and including estimates until 2025. In 1999, the total size of available data was 1.5 exabytes and reached 160 exabytes within seven years. Therefore, between the late 1990s and early 2000s, a dataset of size 1GB would qualify as big data. Total data storage capacity in 2019 reached almost 50 zettabytes and it is estimated to come close to 200 zettabytes by 2025<sup>2</sup>. Interestingly, 90% of the data has been created only since 2016. The size of big data is therefore so fluid and quickly redefined, that a possible definition could be that of information that's so extensive or complex that it's difficult or impossible to process using traditional methods and technology  $^{3}$ .

$<sup>^1</sup>$ Information Age

<sup>&</sup>lt;sup>2</sup>How Big is Big Data

<sup>&</sup>lt;sup>3</sup>What is Big Data

**Figure 1.1.:** Annual Size of the Global Datasphere. Source: Data Age 2025, sponsored by Seagate withdata from IDC Global Datasphere.

Big Data Domains: The onslaught of information and data has been so fierce that it has managed to define modern societies and cause a major shift in the dynamics of global economy, as an increasing number of businesses has to handle big data or has been created with this purpose. Companies with activity in this market typically need some kind of software, i.e. Big Data analytics. Depending on the customer, these analytics could be a prediction model, risk analysis or visualization components. Apart from software, users also need to acquire special hardware and equipment to efficiently participate in the Big Data analysis chain such as connected devices, network equipment, mobile devices. Such matters demonstrate such complexity that led to the establishment of consultation companies that assist others in managing big data, building a big data infrastructure e.t.c.. These activities add up to a very prosperous market that was worth 206.95 USD billion in 2020. As the big data growth trend does not show any signs of slowing down, there are projections that estimate the market growth to reach 549.73 billion USD by 2028<sup>4</sup>.

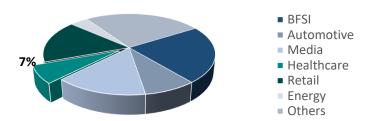

Big Data are generated from various aspects of human activities. Fields like education, banking, retail, agriculture, healthcare, IT and telecommunications have been generating data exponentially and therefore require big data solutions for efficient processing. For example in agriculture, data from sensors, GPS-equipped tractors, satellites, soil sensors can be leveraged to perform risk assessments, crops optimization and prediction e.t.c.. In the social sciences, there is an enormous volume of data to evaluate coming from social media platforms (Facebook, Instagram), chat applications (WhatsApp), and services such as Youtube. The BFSI (Banking, Financial Services and Insurance) domain has leveraged big data analytics to improve the quality of customer service<sup>5</sup> (e.g. tracking their activity to provide for resources when required) as well as the decision-making system, risk management processes, retention strategies<sup>6</sup> in order to maximise gains. In the telecommunication and media domain, big data analytics are leveraged to optimize the network,

<sup>&</sup>lt;sup>4</sup>Big Data Analytics Market Report, 2021-2028, Fortune Business Insight.

$<sup>^5\</sup>mathrm{Big}$  data as a tool to improve customer experience.

$<sup>^6</sup>$ Your Go-to Guide to Big Data Analytics in Banking.

#### Market Size Breakdown

**Figure 1.2.:** Global Big data analytics market share distribution, 2020. Source: Fortune Business Insights.

perform preventive diagnostics, prevent fraud<sup>7</sup> e.t.c..

Big Data in Healthcare: Fig.1.2 represents a distribution percentage for the fields that hold the larger shares in the market, as those were estimated in 2020. Healthcare holds a considerable portion of the market share as big data analytics are required to cope with the recent fast data growth. Until recently, all form of medical data (such as patient history, clinical data, results of exams) were stored in a paper file system. The digitization of all clinical exams and medical records and the advent of new technologies has led to a data abundance and has also created great potential for improved healthcare services and flourishing of research activities.

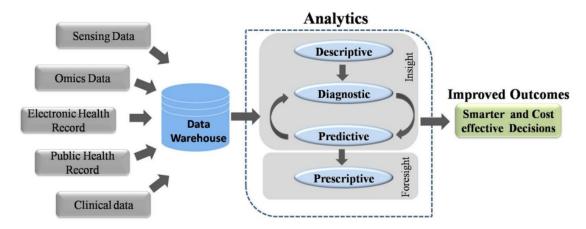

Fig.1.3 depicts the major types of data in the healthcare big-data repository as well as the main type of analyses that rely on these data. The Public Health Records and Electronic Health Records (EHRs) are an electronic version of the medical history of a patient and is available to public health providers in order to optimize the procedure of diagnosis and therapy of a patient. It includes demographic data, past diagnoses, medicines, allergies, immunizations and treatment plans [6]. Clinical data refer to both administrative data as well as data created during clinical practice. Data generated during clinical practice are mainly signal-based signals, i.e. time series, that are essential for monitoring e.g. ECG,EEG,ventilator signals, ICU data etc. A large part of these data also come from IoT devices, i.e. mainly health-tracking wearable devices, biosensors, clinical devices for monitoring vital signs, and others types of devices or clinical instruments. Clinical data also include images such as X-ray and CT scans, MRI, fMRI. Both signal-based and imaging data can assist in monitoring, warning of critical situations, diagnosis, drug development e.t.c. They are utilized both for diagnosis as well as health surveys and clinical trials.

Apart from data generated and utilized in the clinical practice, there is a huge part of health data also come from the study of diseases and human on a biological level. Genes, transcripts, proteins, metabolites, and other macro/ micro molecules systematically col-

<sup>&</sup>lt;sup>7</sup>how telecom companies use big data analytics-Top 10 use cases.

**Figure 1.3.:** Storage of massive amount of data from various sources and Big data Analytics in the Healthcare domain [1].

laborate to perform complex cellular processes. The advent of whole-genome sequencing and other high-throughput experimental technologies have created the data rich disciplines of genomics, transcriptomics, epigenomics, proteomics, metabolomics, phenomics e.t.c. These immense data sets make up the *omics* data [7]. Multi-omics data generated for the same samples can be combined to provide useful insights into the flow of biological information at multiple levels and thus can help in unraveling the mechanisms underlying the biological condition of interest. Therefore the study of omics straightforwardly affects biological research on a cellular level. However, the insights have had a impact on clinical applications too and have paved the way to drug-development applications and, ultimately, into personalized genomic medicine [8–11].

Healthcare big data analytics are developed to extract value out of this immense and diverse amount of data [12]. These analytics require experts that come from interdisciplinary fields such as biology, information technology, statistics and mathematics and work in synergy to provide meaningful analytics and improve healthcare services and treatments. There is a wide range of analytics developed with the intent to assist in the clinical practice as well as in the diagnosis and formation of the therapeutic schema. For example, **descriptive** analytics are leveraged to present data in an understandable manner and make it easy to detect patterns. Applications such as medical imaging are an integral part of medical practice and diagnosis. **Predictive** analytics have also been developed to guide the medical staff in making a diagnosis and choosing the most effective treatments based on previous experience and results. This can lead to accurate diagnosis and limit the number of redundant and expensive clinical exams. Therefore, the integration of big data in the healthcare shows promise for improving health outcomes while preserving a low cost per medical case.

Computational Challenges and Solutions: Handling and storing such an enormous size of big data poses a challenge in healthcare analytics, as does in the case of big data

analytics in general. In terms of computational performance, the enormous datasets and the computational intensity of these analytics stress the limits of modern computing power. As data continue to grow exponentially, systems and algorithms should be constantly updated and improved to provide the computational power to solve big data problems.

An initial approach to big data challenges was to create Big data infrastructures that are essential for meeting the storage and computational requirements. Until recently, big data processing challenges were solved by ecosystems such as Hadoop [13–16] and Spark [17, 18]. Applications were also altered to run within MapReduce [19–22], which is a parallel programming model was developed to run applications with high scalability and fault tolerance on top of HDFS systems. To mitigate however learning curve and tedious problem-solving related with these technologies, most enterprises have migrated big data to the cloud. Cloud computing offers virtualized storage technologies and provides services with high reliability, scalability and autonomy. Several cloud environments have been set up to support the execution of big data analytics in healthcare e.t.c [23–25]. AWS, Microsoft Azure, and Google Cloud Platform offer pay-as-you-go services and allow companies to run data-intensive operations without the installation overhead and with unlimited scalability. A striking example is the deployment of powerful DRAGEN-IT platform on AWS and Azure to analyze next-generation sequencing data [26]. This trend is expected to continue and further develop into hybrid environments (i.e. both local premises and cloud access) and multi-cloud environments <sup>8</sup>.

A more recent approach involves adoption of techniques from the High Performance Computing world. HPC systems have been dealing with complex data and compute intensive applications. The size of the data that HPC applications handle though follow the trend of the Big Data era. This leads to a convergence between the HPC and Big Data ecosystems, creating High Performance Data Analytics (HPDA) and platforms suitable for their execution [27–30]. In this convergence HPC brings approaches such as Message Passing Interface (MPI) [31] and OpenMP [32], possibly combined with accelerators, such as Graphics Processing Units (GPUs) or Field Programmable Gate Arrays (FPGAs). For example, several works have leveraged such programming models [33,34] and co-processors [35–37] to deliver accelerated tools in the genomics domain.

Big data analytics in healthcare face the additional challenge of handling heterogeneous and unstructured data as well as operating in a clinical setting that calls for quick and efficient decisions. In this context, machine learning has been extensively leveraged to cope with the unstructured raw data utilized and assist in finding patterns within them. Many decision making analyses rely on ML and AI to detect complex relationships and assist in the diagnosis procedure. The most common use of ML in medicine is in predictive analytics to detect potential abnormalities and assist physicians in making better clinical decisions. The extensive use of ML and AI in the medical domain is reviewed and

<sup>&</sup>lt;sup>8</sup>The future of big data: 5 predictions from experts for 2020-2025

motivated in several works [38–41].

In the next paragraphs, we focus on two important categories of healthcare analytics that cope with an enormous set of data and face performance bottlenecks, i.e. ML-based predictive analytics and genomics. We first elaborate on the importance and impact of Machine Learning and Genomics in healthcare and motivate the need for employing optimization techniques from the HPC world to alleviate the introduced challenges in two separate use cases.

### 1.2. Machine Learning and Bioinformatics in Healthcare

#### Machine Learning in HealthCare: Challenges and Trends

The inherent purpose and characteristic of machine learning is the ability to process data in order to discover underlying patterns, relationships between different entities as well as insights within human activities and behavior. As such, machine learning has an essential role in the big data processing chain and analytics [42]. In fact, the data deluge of the last decades as well as the variety and complexity of big data has spurred on an impressive growth in the machine learning domain. Since healthcare has proved to be one of the most flourishing big data domains, machine learning has been established as an essential tool in health data manipulation and analysis. Machine learning solutions fit both the big data nature of healthcare data as well as the need of healthcare to find patterns and correlations within unstructured raw medical data.

The size of the datasets in combination with the computational complexity of uncovering relations within such volume has truly challenged the capabilities of machine learning techniques and has led to the development of new approaches and algorithms [43] in order to meet the requirements and successfully extract patterns and build predictive models. Databases, data mining, information retrieval, machine learning, deep learning, AI are only a few of the fields that created opportunity for ML to flourish<sup>9</sup>. The use of AI and ML in healthcare however also encounters challenges specific to the field and use cases [38]. From a technical perspective, it is challenging to integrate data from different sources (i.e. healthcare units) and account for the heterogeneity and potential bias/noise in each one. Similarly, it is not feasible to require a golden standard as it should be acquired from the general population and reviewed by medical practitioners. Problems also arise when integrating machine learning models in a medical environment, as the results cannot be translated effectively in a way understandable by health staff. Developing a big data infrastructure or cloud services for sharing data among different healthcare centers is still challenging as they need to adhere to a universal standard

<sup>&</sup>lt;sup>9</sup>When Machine Learning meets Big Data

representation of data and privacy regulations. Lastly, the adoption of proposed ML solutions requires validation and improvement through clinical trials and studies to lead to successful adoption in the medical world.

Despite the difficulties, there are on-going and promising works that leverage ML for solving healthcare problems. One of the primary areas of applying machine learning in healthcare is information extraction. AI programs and tools such as NLP [44] or character recognition were leveraged from the start to extract information from free text or speech and assist in digitization of medical data. Machine learning has been extensively leveraged for prediction tasks in application where real-time processing of signals and decisionmaking are critical. A representative example is the framework described in [45], which trains an ML model with time-series signals (e.g. heart rate, systolic BP, respiratory rate etc) to provide a real-time early warning for septic shock. Similarly, the authors in [46] develop a real-time system for timely detection of heart disease based on streaming signals originating from IoT and wearable devices. ML has also been established for detection or prediction tasks where real-time processing is not essential. For example, it is leveraged in image analytics to detect abnormalities in high resolution medical images (e.g. CT, MRI, fMRI, EEG) [47]. Therefore, it can prove very useful to the diagnosis process even at a consultation level or as a measure of precaution to avoid misdiagnosis [1].

Overall, the importance of incorporating ML analytics in healthcare is highlighted by the magnitude and critical nature of diagnostic and prognostic applications. Epileptic seizure prediction [48], breast cancer diagnosis [49,50], heart disease diagnosis [51], research for brain diseases [52] are only a few of the prominent use cases that leverage ML and AI to improve the quality of healthcare services. However, due to the big data nature of medical records and signals, the need to identify complex patterns within the data and often the real-time requirements, ML-healthcare analytics have intense memory and computational requirements. As a result, there is rich literature that studies machine learning techniques applied in healthcare from the scope of optimization and performance enhancement.

In general, machine learning methods used in healthcare analytics share the same optimization techniques with ML solutions for big data analytics. A common practice to achieve scalability and data parallelism [43], is to employ big data frameworks such as Hadoop [53] and Spark [54]. Another approach requires implementation of ML models to run through the MapReduce programming model [55–60]. Cloud computing is also extensively used to deliver efficient healthcare services [61, 62]. Apart from specialized big data techniques and cloud computing, optimization solutions also leverage the parallelism and scalability of High Performance Computing and specifically of powerful hardware resources. Hardware optimizations are examined on architecture level, mixed-signal circuits and advanced technologies such as efficient memories e.t.c. [63]. As far as platforms are concerned, GPUs, FPGAs and ASICs devices are targeted by several works [64]. Increased interest has been also attracted by hybrid solutions that

incorporate GPU or FPGA accelerators for ML models in data centers and at the edge [65,66].

#### **Bioinformatics: Challenges and Trends**

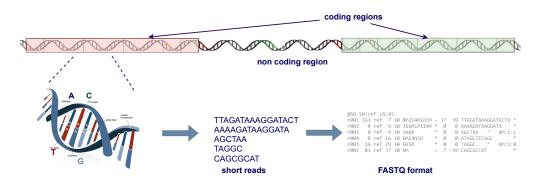

Bioinformatics is an interdisciplinary field focusing on the application of statistical and computational methodologies to manage and interpret biological data [67]. An essential part of bioinformatics is the study of DNA sequences for research or therapeutical purposes. Recent technological advances in high throughput technologies has led to an unprecedented wealth of genomic sequence data. The low cost of data generation has created an enormous amount of data, signaling the establishment of genomic data as a new unique type of big data [68].

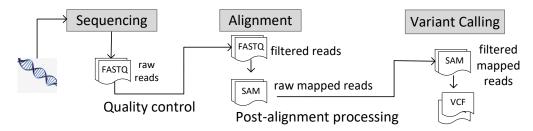

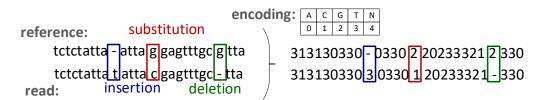

This new era of genomic data deluge commenced with the completion of the Human Genome project, which for the first time generated an accurate sequence of 3 billion DNA bases covering 99% of the gene-containing regions 10. Since then, many projects have been conducted to further understand areas of interest within the human genome e.g. the Cancer Genome Atlas and the Encyclopedia of DNA Elements which identify somatic mutations, mRNA expressions, histology slides for approximately 7000 human tumors<sup>11</sup> [68]. The enormous size of genomic and transcriptomic data is obvious, if we take into account that sequencing a single whole genome generates more than 100 gigabytes of data. Specifically, depending on the read length and coverage (i.e. the average number of times each base is read), when sampling a human individual the original file of reads in FASTQ is approximately 250 GB, the BAM file can be approximately 100 GB, the VCF file can be about 1 GB, and the annotated files can be approximately 1 GB as well [69]. The size escalates when millions of individuals are sequenced. The advent of mass spectrometry and nuclear magnetic resonance (NMR) spectroscopy has come to add another source of big data, by generating proteomic and metabolomic data, and establishing the term of omics data.

Omics studies have since established a significant role in the healthcare domain in the field of understanding, prevention as well as treatment of diseases. In fact, the integration and correlation among genomics, proteomics, metabolomics e.t.c., i.e. multi-omics analysis, paves the way for personalized medicine [70]. Genomic workflows are at the heart of omics analysis and involve a wide range of applications. Whole-genome sequencing (WGS) [71] is the basis of all genomic analysis and allows detection of common as well as rare genetic variants across the genome. Joint variant detection and genotyping [72] are developed to study genetic variants across a large population or even a wider society. Functional interpretation [73] of the molecular effects of genetic variants is also necessary in order to infer if a variant is expressed in the phenotype and responsible for a specific disease [74].

<sup>&</sup>lt;sup>10</sup>Human Genome Project Results

<sup>&</sup>lt;sup>11</sup>National Cancer Institute

An outstanding example of how genomics has impacted healthcare, is the integration of genomic data in cancer studies in order to understand the biological dynamics of cancers and identify risk factors, as well as predict therapeutic outcomes and prognosis [75].

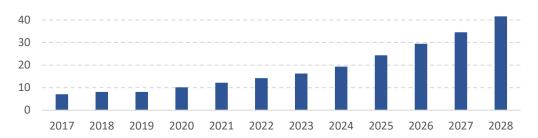

The impact of shift towards personalized medicines and treatments has naturally led to a wider adoption of genomics technology. The capabilities of genomics have been further underlined by the COVID-19 outburst as the genome sequence of the virus is critical for developing effective vaccines and treatments<sup>12</sup>. This has strengthened the lead players in the market of genomics such as Illumina Inc., Thermo Fisher Scientific Inc., Agilent Technologies<sup>13</sup> e.t.c. but it has also increased government funded projects and the establishment of many start-up businesses. This is reflected in Fig.1.4 in the trend for the genomics market in North America, which is expected to hold the highest market share. A similar trend is expected in the global market, whose size will grow from 23.11 billion USD in 2020 to 94.65 billion USD in 2028. A more modest estimate reports an expected market size of 84.57 billion USD by 2031<sup>14</sup>.

# North America Genomics Market Size 2017-2029 (USD billion)

Figure 1.4.: Estimation for Genomics Market Size in upcoming years.

Challenges: This economic growth and need for new services requires the development of novel and efficient analytics to extract useful information from genomic data both for the research and industry domains. However, attributes of genomic data and workflows introduce several challenges that need to be overcome to efficiently process and analyse large genomic data sets [76, 77]. Firstly, the dramatic data growth calls for enormous databases to store data and share them across the research community. The challenge however does not solely lie on the data volume but also on the heterogeneity of data and lack of structure. An inherent trait of most genomic analyses is the need to discover patterns and an underlying structure within the raw data. This leads to sparse data structures, lack of data locality, irregular memory accesses and asynchronous updates to shared structures [78].

<sup>&</sup>lt;sup>12</sup>Genomics Market Research Report 2021-2028, Fortune Business Insights.

$<sup>^{13}\</sup>mathrm{Grand}$  View Research Genomics Market Size.

$<sup>^{14} \</sup>mbox{Bloomberg Global Genomics Industry Update.}$

Trends: These challenges have yet to intensify as the sequencing cost further decreases and more complex analyses are required. The challenges can only be surpassed by leveraging high-end computing solutions and large-scale computational platforms to meet the memory and computational requirements of most genomic analyses. Several approaches have been pursued and different technologies leveraged to achieve quick and accurate results from genomic analytics. Mitigating bioinformatics analytics to Big Data infrastructures can greatly benefit the analysis of genomic data. Firstly, it is a very convenient solution as it can aggregate data from various different sources and store the data in virtualized storage technologies. A cloud computing system is also convenient and flexible as it can support different software libraries, development environments and visualization tools available as pre-installed software tools or containerized services. Cloud computing systems are also suitable candidates for genome analysis thanks to their distribution and scalability capabilities. A typical example of a distributed framework utilized in genomics analytics in the cloud is Hadoop [79] (HDFS - Hadoop Distributed Filesystem) , which separates the data into small fragments, distributes them across many cluster nodes, performs the computation on each node so that they are processed in parallel, and aggregates the results. The parallel processing of many small pieces of data is secured by MapReduce [80] programming model. A typical example of genomic analysis that leverages Hadoop is drug development using genomic and proteomic data [1]. Several other works deploy genomic frameworks on cloud infrastructures as reviewed in the literature [81–85]. A recent example is Genesis framework, that provides an interface for performing SQL-like queries for data manipulation and an integrated hardware library of various genomic analysis stages [86]. Last but not least, cloud computing is also a cost efficient solution. In fact, cloud providers offer a pay-as-you-go policy that allows users to benefit from distributed computing and parallel programming without bearing the cost of building their own infrastructure. However, even these platforms have some adverse impacts, i.e. multi-core solutions increase the energy consumption whereas cloud solutions raise data privacy and ethics issues [87].

Despite the lack of regular accesses and data locality across the span of genomic analyses, each stage of a genomic pipeline usually leverages certain types of algorithms and therefore optimization HPC techniques for efficient execution. For the indexing stage, typical approaches are optimizing the data structure for storing the genome index as well as the search algorithm for locating seeds through this index, e.g. FM-index [88,89]. Hash-tables are also utilized to accelerate search operations in genome assembly and k-mer counting as well as graph theory techniques for efficient graph traversal within genome assembly [78]. The pre-alignment filtering stage is usually accelerated by proposing efficient algorithms that come from the HPC world and can deliver a quick and accurate prediction for redundant alignments. Such examples are the pigeonhole principle [90], q-gram filtering [91] and sparse dynamic programming [92].

The alignment stage holds the primary focus of most accelerating efforts targeting genomic pipelines as it usually forms a major bottleck. Extensive studies review the trends in proposed optimized systems such as specialized architectures, hardware accelerators

and heuristic approaches [93]. Hardware-accelerated solutions specifically is one of the most popular HPC optimization for genomics. A plethora of works exist targeting different architectures from heterogeneous devices, e.g. FPGAs, to many-core accelerators such as GPUs and the Intel Xeon Phi. These devices are usually leveraged as a co-processor to off-load bottlenecks, but can also be utilized for end-to-end accelerated solutions that perform the same functionality as software genomic tools. Lately, in-memory computing has also been proposed for optimizing all genomic stages including the alignment [94–96].

#### 1.3. Thesis Scope and Organization

The thesis scope is fully aligned with the trends described in Section 1.2 and aims to enrich the state of the art works that develop powerful co-processors. The goal is to examine offloading the bottlenecks to reprogrammable devices, i.e. FPGAs, through the meticulous design of efficient accelerators that exploit the existing parallelism and optimize communication with the overall system. The resulting accelerators can then be leveraged on local environments or can be deployed on large-scale cloud infrastructures to explore the results of the synergy of hardware acceleration and cloud computing technologies.

In this thesis, we focus on the hardware acceleration of two representative applications of modern healthcare: a ML-based prediction analysis using ECG signals and Read Alignment of genomic data. The basic HPC tool we utilize to deliver efficient solutions is High Level Synthesis programming targeting FPGA devices. With the proposed implementations, we aim to build upon existing solutions and suggest potential improvements.

We explore different aspects of optimization techniques regarding a single accelerator and leverage the inherent tools' capabilities to increase both instruction level and data level parallelism. In this context, we look for an efficient exploration of built-in optimization directives and strategy for applying them on the accelerator. However we do not limit our search by the tools straightforward solutions but rather find its inefficiencies and guide it in exploiting parallelism through manual source modifications. For complex applications, we do not restrict our efforts on a single module microarchitecture while ignoring the interaction with its environment. On the contrary, we adopt an holistic approach and view the design as part of a greater system. We prove that being mindful of integration implications is necessary for efficient architectural decisions as part of software-hardware co-design process. We propose techniques that are in tune with these objectives and apply them selectively to two major use cases, one from each domain. We also leverage more than one HLS frameworks and programming models in order to fully evaluate the capabilities of the available tools and demonstrate that the architectural decisions,

#### Introduction

instruction level parallelism and memory configuration schemas we apply can be agnostic of the selected vendor and software by a large part.

Based on these principles, we develop three accelerators using High Level Synthesis for the Machine Learning and Genomics domains. The thesis unfolds in two major directions:

An Exploration Framework for Efficient High-Level Synthesis of Support Vector Machines: Case Study on ECG Arrhythmia Detection for Xilinx Zynq SoC. A methodology for accelerating an SVM classifier has been implemented as a framework on top of the state-of-art Vivado High-Level Synthesis (HLS) tool. Our proposed SVM accelerator and methodology is validated for a healthcare usecase that performs classification for arrhythmia detection in ECG signals. We propose a systematic two-level approach that first optimizes the global structure of the original SVM's behavioral description to exploit the data- and instruction-level parallelism and then further refine it through a targeted design exploration of the tool's automatic optimization technique.

Acceleration of Short Read Alignment. The thesis presents two different approaches on accelerating the short read alignment problem. First, we present GANDAFL, a novel genome alignment dataflow architecture for Smith-Waterman Matrix-fill and Traceback stages to perform high throughput short-read alignment on NGS data. The implementation of Traceback on hardware is combined with a radical software restructuring of Bowtie2 aligner, that implements a batching aggregation strategy, diminishes data transfer and accelerator call overheads and allows for efficient integration of the accelerator within the aligner to deliver an end-to-end speedup. We then introduce a high throughput alignment system that combines Banded SmithWaterman accelerators and pre-filtering for alignment optimization by introducing a profile-driven accelerator methology. The proposed system includes multiple accelerators with edit thresholds indicated by the input edit threshold distribution and leverages pre-filtering to guide candidate alignments to the appropriate accelerator. The adoption of these profile-driven upper limits and resource-efficient Banded SmithWaterman accelerators enables the provision of a highly parallel Banded Smith-Waterman system that accelerates read alignment while preserving the accuracy.

The rest of this thesis is organized as follows:

- Chapter 2 presents prior art of the examined fields and highlights the contributions of the Thesis.

- Chapter 3 provides a theoritical background on the domains discussed throughout the thesis. It presents the fundamental concepts and principles of the applications and introduces the basic capabilities of the utilized tools and frameworks.

- Chapter 4 presents the work conducted to accelerate the SVM for arrythmia detection based on an optimization strategy that leverages both source code optimizations and built-in tuning knobs of Vivado HLS tool.

- Chapter 5 presents a novel genome alignment architecture for Smith Waterman algorithm and the integration with popular Bowtie2 aligner.

- Chapter 6 presents a high throughput alignment system that is based on a profiledriven methodology and leverages multiple Banded SmithWaterman accelerators of different edit thresholds to deliver speedup while preserving alignment accuracy.

- Chapter 7 concludes this thesis by summarizing the presented results and discusses the future extensions of this work.

Introduction

## Chapter 2.

### Thesis Contribution

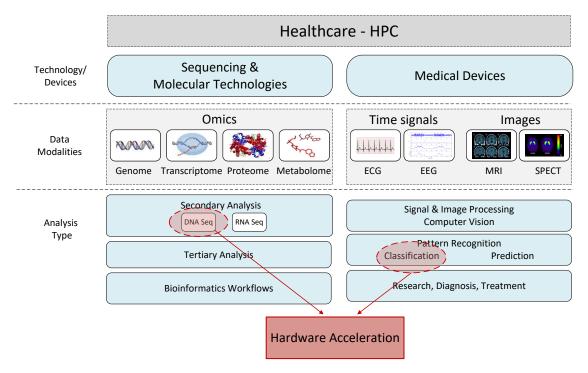

In this thesis, we focus on two different healthcare applications and employ hardware acceleration techniques from the HPC domain for optimization purposes. Fig.2.1 presents a non-comprehensive taxonomy of applications in the convergence of the HPC and healthcare domain from the thesis perspective. We examine two major categories of healthcare data modalities and the respective analyses required to extract biological and clinical insights.

Omics data are generated by raw DNA samples or molecules through technologies such as sequencing and mass spectrometry. Each omics data, i.e. genomics, transcriptomics, proteomics, metabolomics etc, provide necessary and valuable information on mechanisms on multiple molecular levels. A hierarchy of data processing and analyses is required to extract this information from the initial samples. Multi-omics analysis is a popular bioinformatics approach that combines information from cellular up to metabolic level in order to understand the underlying mechanisms and leverage this knowledge for research and clinical purposes. This thesis scopes lies within the secondary analysis of genomic data, which performs alignment of DNA fragments in order to provide the full sequence for a sample and subsequently determine genetic variants.