#### ΕΘΝΙΚΟ ΜΕΤΣΟΒΙΟ ΠΟΛΥΤΕΧΝΕΙΟ ΣΧΟΛΗ ΗΛΕΚΤΡΟΛΟΓΩΝ ΜΗΧΑΝΙΚΩΝ ΚΑΙ ΜΗΧΑΝΙΚΩΝ ΥΠΟΛΟΓΙΣΤΩΝ ΤΟΜΕΑΣ ΤΕΧΝΟΛΟΓΙΑΣ ΠΛΗΡΟΦΟΡΙΚΗΣ ΚΑΙ ΥΠΟΛΟΓΙΣΤΩΝ

#### ΔΙΠΛΩΜΑΤΙΚΗ ΕΡΓΑΣΙΑ

# Optimized FPGA implementation for Random Forests for Anomaly Detection

Εμμανουήλ Αραπίδης Α.Μ.: 03116071

Επιβλέπων : Δημήτριος Ι. Σούντρης Καθηγητής ΕΜΠ

## Αθήνα Οκτώβριος 2023

#### ΔΙΠΛΩΜΑΤΙΚΗ ΕΡΓΑΣΙΑ

# Optimized FPGA implementation for Random Forests for Anomaly Detection

Εμμανουήλ Αραπίδης Α.Μ.: 03116071

Επιβλέπων : Δημήτριος Ι. Σούντρης Καθηγητής ΕΜΠ

Τριμελής Επιτροπή Εξέτασης

(Υπογραφή) (Υπογραφή) (Υπογραφή)

Δημήτριος Σούντρης Παναγιώτης Τσανάκας Σωτήριος Ξύδης

Καθηγητής Καθηγητής Επίκουρος Καθηγητής

ΕΜΠ ΕΜΠ

Ημερομηνία Εξέτασης: 1/11/2023

Copyright © - All rights reserved Εμμανουήλ Αραπίδης, 2023. Με επιφύλαξη παντός δικαιώματος.

Απαγορεύεται η αντιγραφή, αποθήκευση και διανομή της παρούσας εργασίας, εξ΄ ολοκλήρου ή τμήματος αυτής, για εμπορικό σκοπό. Επιτρέπεται η ανατύπωση, αποθήκευση και διανομή για σκοπό μη κερδοσκοπικό, εκπαιδευτικής ή ερευνητικής φύσης, υπό την προϋπόθεση να αναφέρεται η πηγή προέλευσης και να διατηρείται το παρόν μήνυμα. Ερωτήματα που αφορούν τη χρήση της εργασίας για κερδοσκοπικό σκοπό πρέπει να απευθύνονται προς τον συγγραφέα.

Οι απόψεις και τα συμπεράσματα που περιέχονται σε αυτό το έγγραφο εκφράζουν τον συγγραφέα και δεν πρέπει να ερμηνευθεί ότι αντιπροσωπεύουν τις επίσημες θέσεις του Εθνικού Μετσόβιου Πολυτεχνείου.

(Υπογραφή)

Εμμανουήλ Αραπίδης

$\Delta$ ιπλωματούχος Ηλεκτρολόγος Μηχανικός και Μηχανικός Υπολογιστών  $E.M.\Pi.$

©2023 - All rights reserved.

## Contents

| П             | ερίλ: | ባψη                                               | 6  |

|---------------|-------|---------------------------------------------------|----|

| $\mathbf{A}$  | bstra | nct                                               | 8  |

| $\mathbf{E}'$ | υχαρ  | ριστίες                                           | 9  |

| 1             | Ex    | τενής Περίληψη                                    | 10 |

|               | 1.1   | Εισαγωγή-Κίνητρο                                  | 10 |

|               | 1.2   | Σχετική Εργασία                                   | 12 |

|               | 1.3   | Random Forest Αλγόριθμος                          | 13 |

|               | 1.4   | FPGA & HLS Εργαλεία                               | 15 |

|               | 1.5   | Υλοποίηση του Random Forestγια Σύνθεση Υψηλού     |    |

|               |       | Επιπέδου                                          | 17 |

|               | 1.6   | Αρχιτεκτονικές βελτιστοποιήσεις του Random Forest |    |

|               |       | βασισμένες στο HLS                                | 18 |

|               |       | 1.6.1 Παραλληλισμός εσωτερικά του Random Forest   | 18 |

|               |       | 1.6.2 Παραλληλισμός μεταξύ πολλών Random Forest   | 19 |

|               | 1.7   | Εξερεύνηση με εφαρμογή Precision Scaling          | 21 |

|               | 1.8   | Πειραματική Αξιολόγηση                            | 22 |

|               | 1.9   | Συμπεράσματα και Μελλοντική Εργασία               | 25 |

| <b>2</b>      | Inti  | roduction                                         | 27 |

| 3             | The   | eoretical Background                              | 30 |

|               | 3.1   | Related Work                                      | 30 |

|               | 3.2   | Random Forest Algorithm                           | 32 |

|               | 3.3   | FPGA                                              | 36 |

|               |       | 3.3.1 Understanding the FPGA Architecture         | 36 |

|               |       | 3.3.2 FPGA Components                             | 40 |

|               | 3.4   | High Level Synthesis                              | 42 |

|               | 3.5   | Vitis and Host code                               | 45 |

| 4             | Rar   | ndom forest implementation for HLS                | 50 |

|               | 4.1   | Model training and tuning                         | 50 |

|               | 4.2   |                                                   | 55 |

|               |       | 4.2.1 Python to C++ Model Conversion              | 55 |

|               |       | 122 C++ to Vitis HIS Modifications                | 50 |

| <b>5</b>               | Arc            | hitectural optimizations for HLS-based Random                                                                                                                                                                                                                          | ı   |

|------------------------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|                        | fore           | est                                                                                                                                                                                                                                                                    | 61  |

|                        | 5.1            | Estimator parallelism within a Random Forest 5.1.1 Challenge 1:Multi-threaded execution on hard-                                                                                                                                                                       | 61  |

|                        |                | ware                                                                                                                                                                                                                                                                   | 61  |

|                        |                | 5.1.2 Challenge 2: Efficient BlockRAM utilization                                                                                                                                                                                                                      | 65  |

|                        | 5.2            | Parallelism across multiple random forests                                                                                                                                                                                                                             | 72  |

|                        |                | 5.2.1 Coarse Grained Design                                                                                                                                                                                                                                            | 73  |

|                        |                | 5.2.2 Pipeline architecture                                                                                                                                                                                                                                            | 78  |

| 6                      | $\mathbf{Pre}$ | cision Scaling Exploration                                                                                                                                                                                                                                             | 88  |

|                        | 6.1            | Fixed Point representation                                                                                                                                                                                                                                             | 90  |

|                        | 6.2            | Integer representation                                                                                                                                                                                                                                                 | 91  |

| 7                      | Aut            | comated framework for hw design exploration                                                                                                                                                                                                                            | 97  |

| 8                      | Exp            | perimental                                                                                                                                                                                                                                                             | 101 |

|                        | 8.1            |                                                                                                                                                                                                                                                                        | 101 |

|                        | 8.2            | Results - Evaluation                                                                                                                                                                                                                                                   | 103 |

| 9                      | Cor            | nclusions                                                                                                                                                                                                                                                              | 118 |

| •                      | 9.1            | Summary                                                                                                                                                                                                                                                                |     |

|                        | 9.2            | v                                                                                                                                                                                                                                                                      |     |

| $\mathbf{L}^{	ext{i}}$ | ist o          | of Figures                                                                                                                                                                                                                                                             |     |

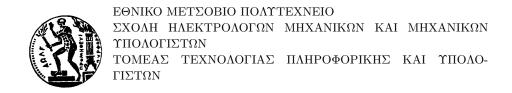

|                        | 1              | (a) Training process: Multiple decision trees constructed on bootstrap samples of the training set(in this fig there are only two classes shown -orange and blue)(b) Classification process: The classification decision is based on the majority voting results among |     |

|                        |                | all the trees.[13]                                                                                                                                                                                                                                                     | 35  |

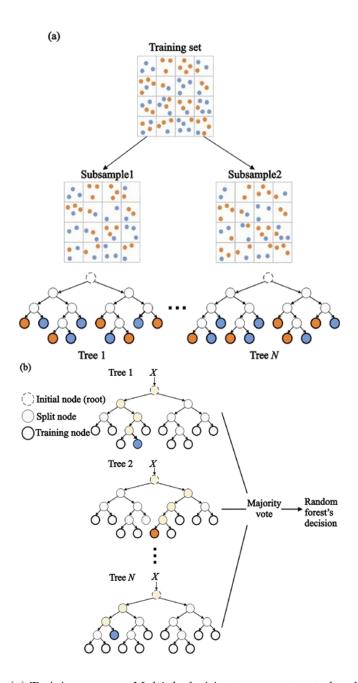

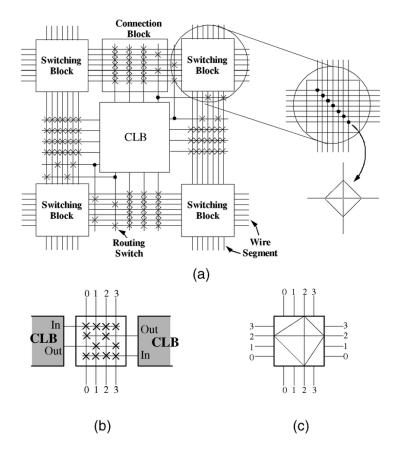

|                        | 2              | FPGA Architecture[14]                                                                                                                                                                                                                                                  | 37  |

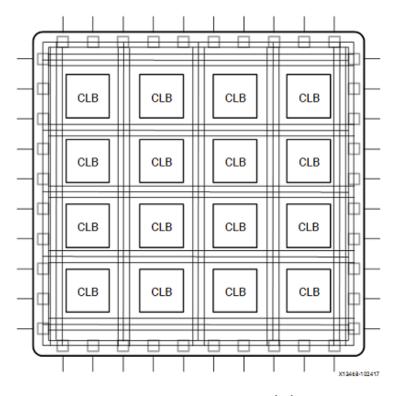

|                        | 3              | Simplified illustration of a logic cell.[16]                                                                                                                                                                                                                           | 38  |

|                        | 4              | FPGA Routing configuration.[17]                                                                                                                                                                                                                                        | 39  |

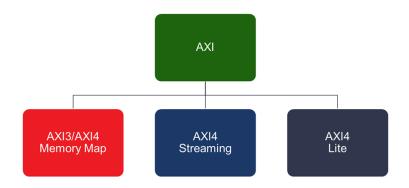

|                        | 5              | Axi protocol. [18]                                                                                                                                                                                                                                                     | 39  |

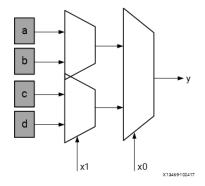

|                        | 6              | Lut Representation.[15]                                                                                                                                                                                                                                                | 40  |

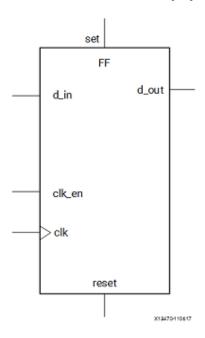

|                        | 7              | Flip Flop Representation.[15]                                                                                                                                                                                                                                          | 41  |

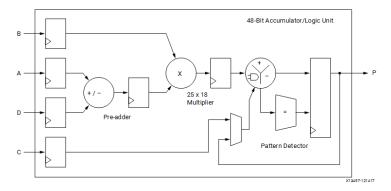

|                        | 8              | DSP Representation.[15]                                                                                                                                                                                                                                                | 42  |

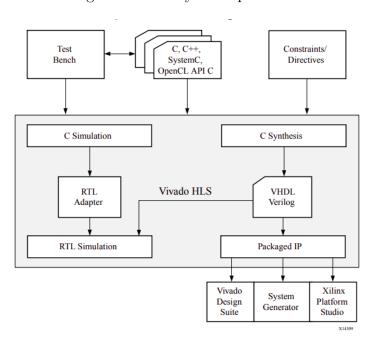

|                        | 9              | Vivado HLS Design Flow.[20]                                                                                                                                                                                                                                            | 44  |

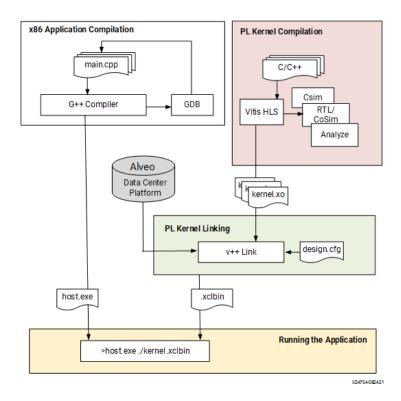

| 10 | Vitis Development Flow[21] 47                             |

|----|-----------------------------------------------------------|

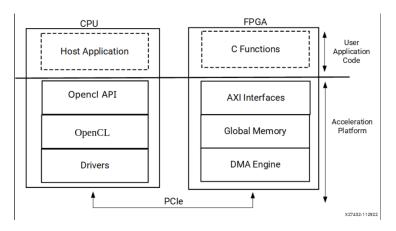

| 11 | CPU/FPGA Interaction[21] 48                               |

| 12 | Confusion Matrix[22]                                      |

| 13 | Fscore metrics[22]                                        |

| 14 | Decision Trees traversal using arrays 57                  |

| 15 | Bram utilization                                          |

| 16 | Latency of an single sample 71                            |

| 17 | Unroll vs Hardcoded resources                             |

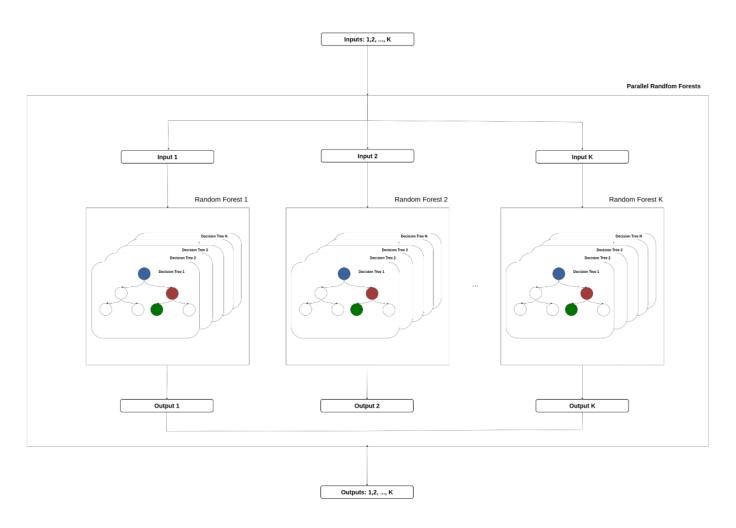

| 18 | K parallel RFs with N parallel estimators for simul-      |

|    | taneous processing of K inputs                            |

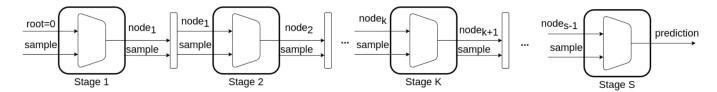

| 19 | Stages of a DT                                            |

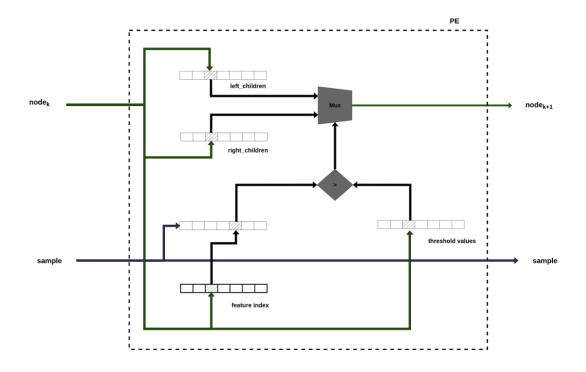

| 20 | Representation of a stage                                 |

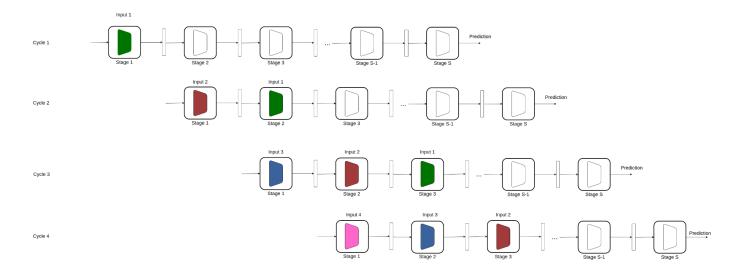

| 21 | Propagation of input data through the pipeline design. 80 |

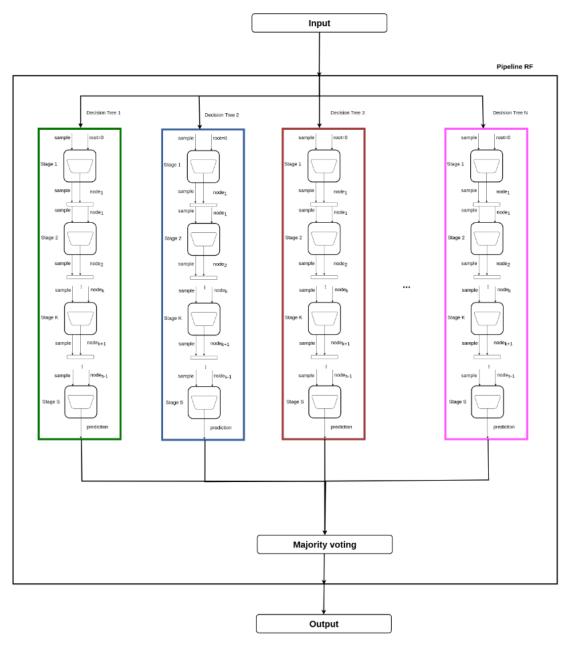

| 22 | Representation of RF pipeline 81                          |

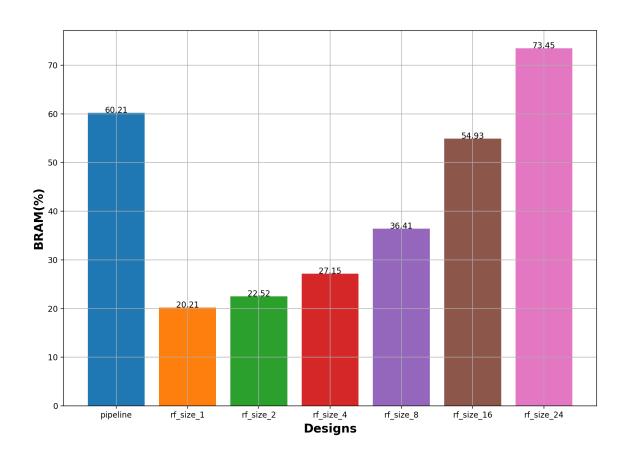

| 23 | Bram Utilization                                          |

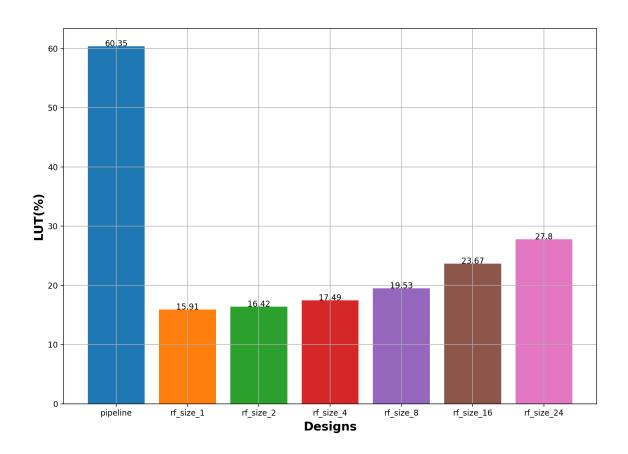

| 24 | LUT Utilization                                           |

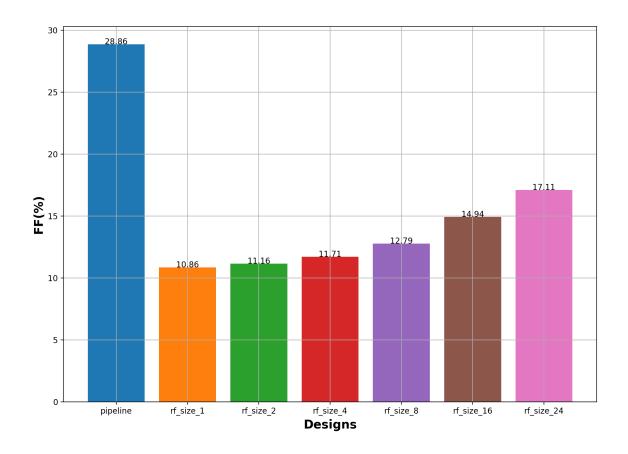

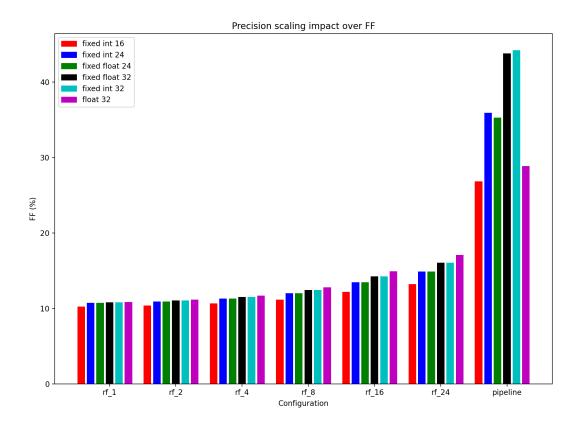

| 25 | FF Utilization                                            |

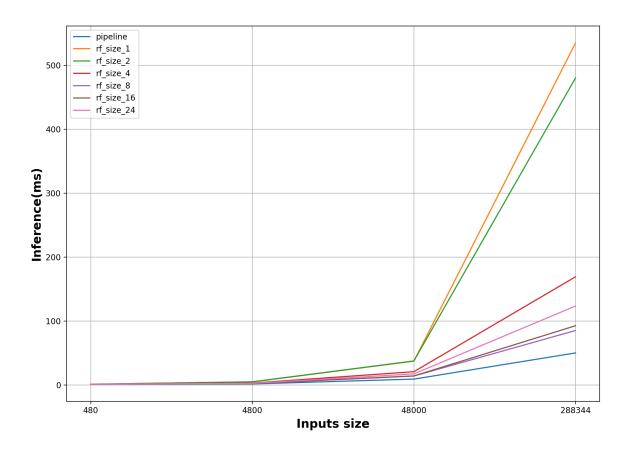

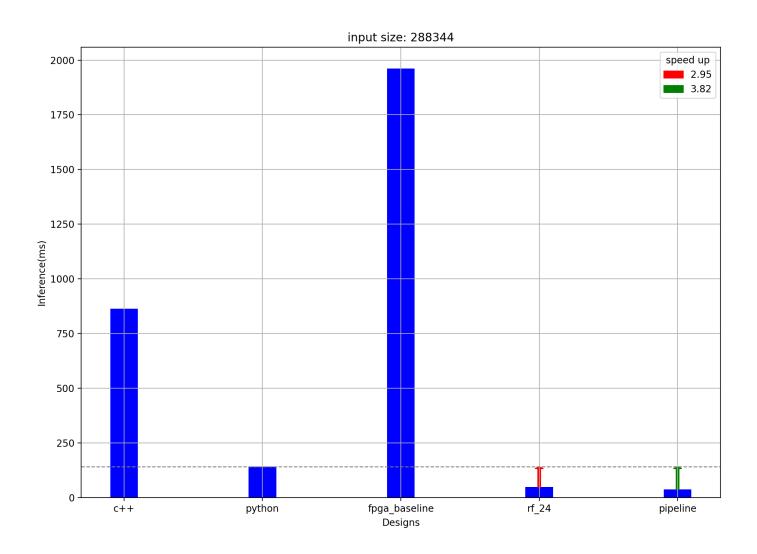

| 26 | Inference times                                           |

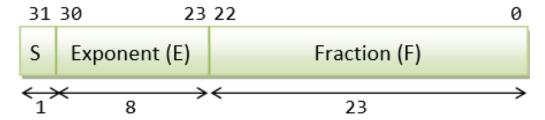

| 27 | Floating Point Representation[23] 90                      |

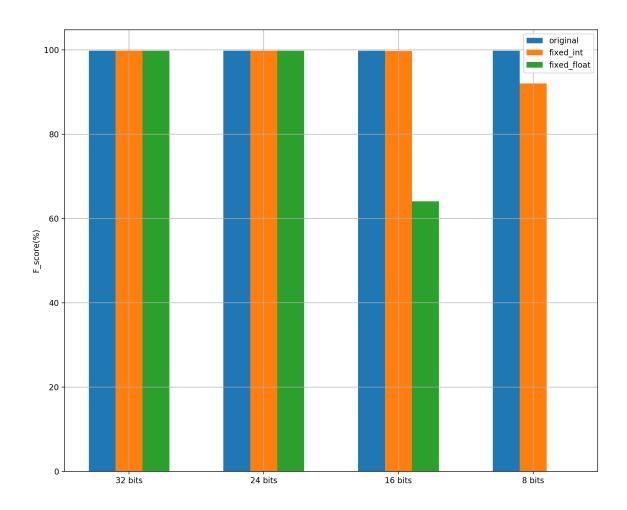

| 28 | Precision scaling fscore[23]96                            |

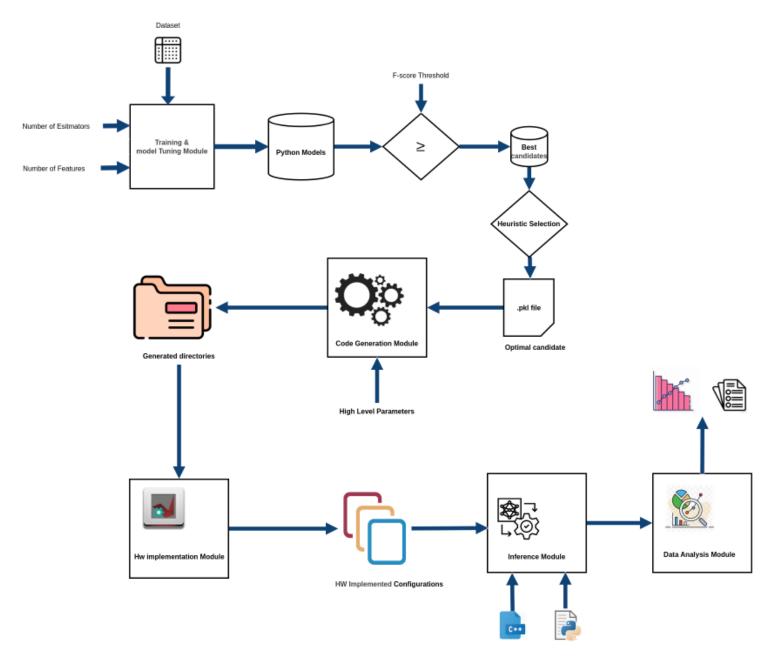

| 29 | Components and workflow of the framework 100              |

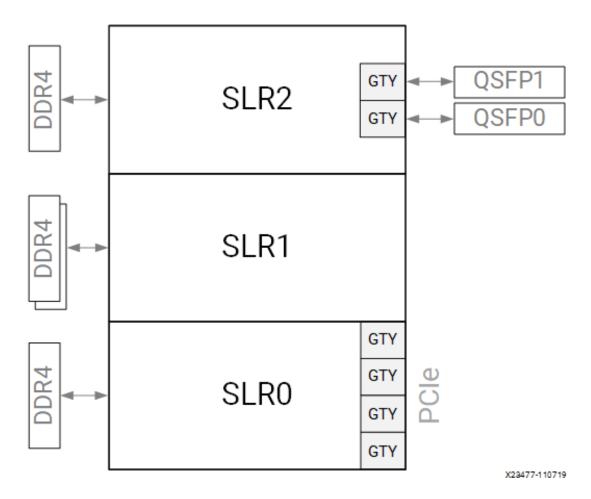

| 30 | Floorplan of the XCU200 Device [26] 102                   |

| 31 | Resources of U200 card                                    |

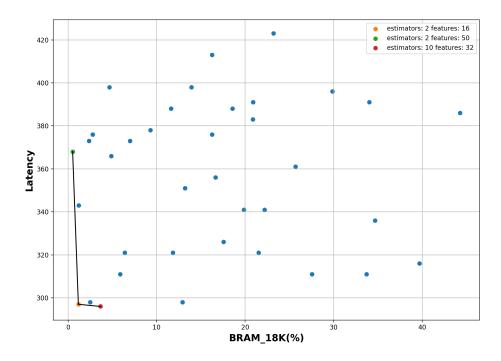

| 32 | Selection of optimal model using hw emulation heuris-     |

|    | tic                                                       |

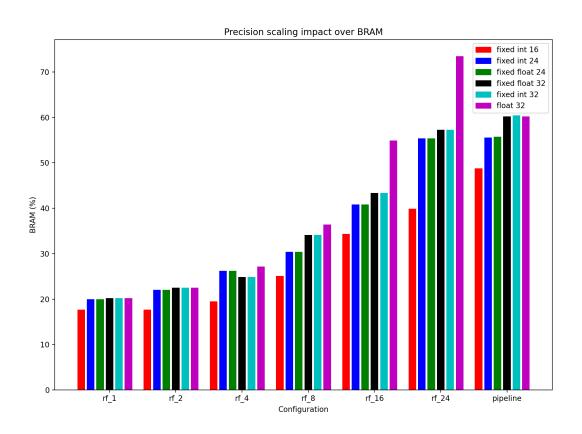

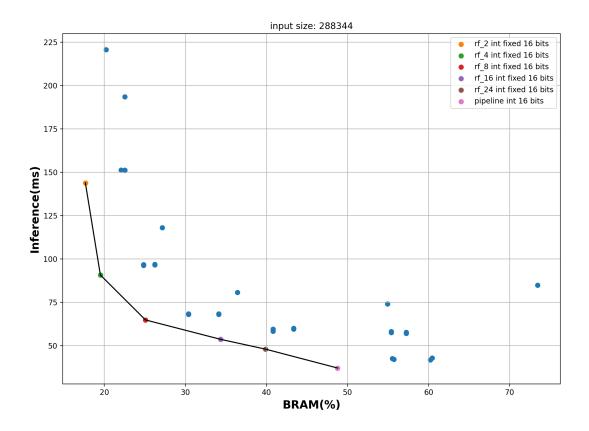

| 33 | Impact of precision scaling over BRAM Utilization(%).105  |

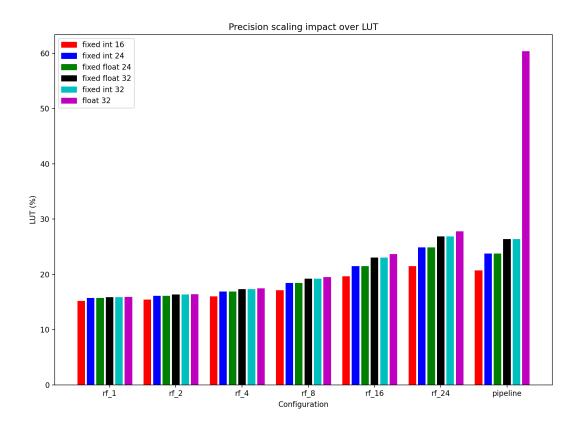

| 34 | Impact of precision scaling over LUT Utilization(%). 106  |

| 35 | Impact of precision scaling over FF Utilization(%) 107    |

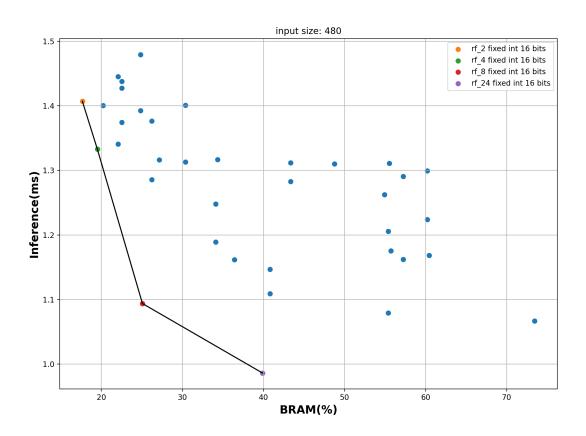

| 36 | Pareto plot for input size 480 samples 108                |

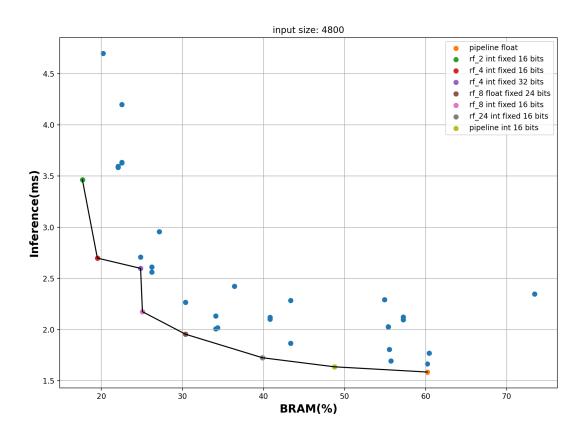

| 37 | Pareto plot for input size 4800 samples 109               |

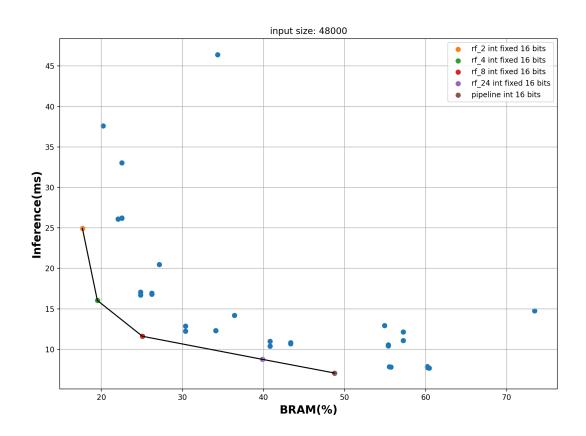

| 38 | Pareto plot for input size 48000 samples 110              |

| 39 | Pareto plot for whole test dataset                        |

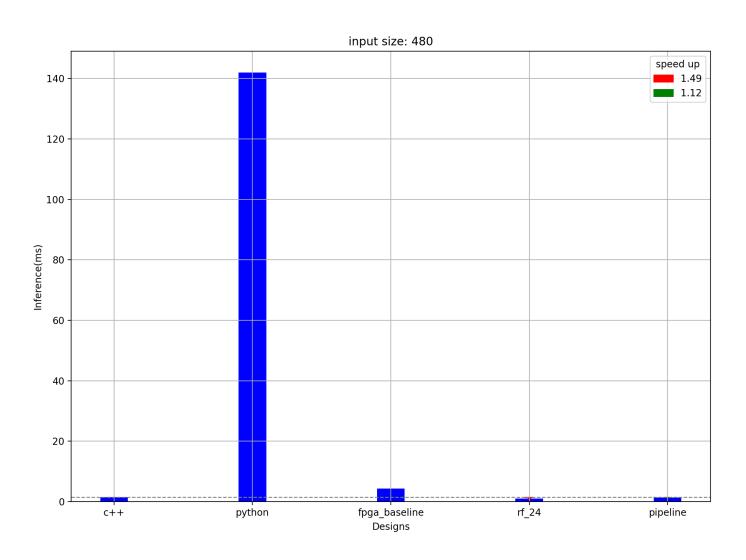

| 40 | Inference comparison for 480 samples                      |

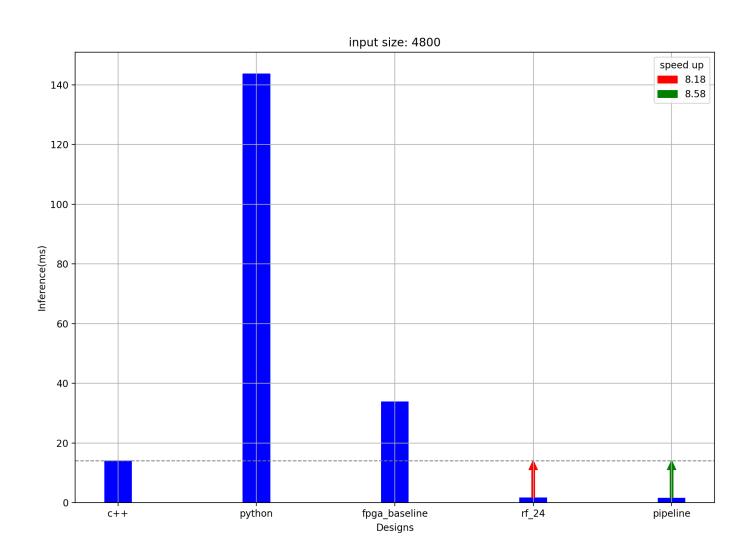

| 41 | Inference comparison for 4800 samples                     |

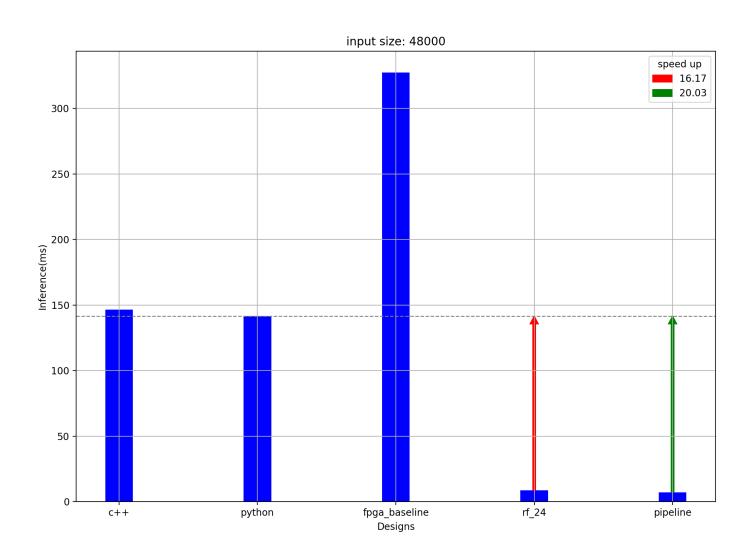

| 42 | Inference comparison for 4800 samples                     |

| 43 | Inference comparison for whole test dataset 115           |

|    |                                                           |

## List of Tables

| 1      | Achieved speed up                                      | 24  |

|--------|--------------------------------------------------------|-----|

| 2      | Features                                               | 51  |

| 3      | Evaluation metrics                                     | 54  |

| 4      | Sequential vs Parallel                                 | 64  |

| 5      | Resources Utilization for HW implementation            | 77  |

| 6      | Required Cycles for Dataset of size D                  | 83  |

| 7      | Pipeline Resources Utilization                         | 86  |

| 8      | <del>-</del>                                           | 116 |

| Listin | $_{ m igs}$                                            |     |

| 1      | Random Forest C++                                      | 58  |

| 2      | Template For FPGA                                      | 59  |

| 3      | Example of Header file                                 | 60  |

| 4      | Updated Code                                           | 61  |

| 5      | Parallel estimators                                    | 64  |

| 6      | Manual Unroll using the generic form of the decisio    |     |

|        | tree function.                                         | 66  |

| 7      | Hardcoded Random Forest                                | 67  |

| 8      | Header file with RF_SIZE                               | 74  |

| 9      | parallel_rf RF_SIZE=8                                  | 75  |

| 10     | Function definitions                                   | 75  |

| 11     | Top kernel function                                    | 76  |

| 12     | Functions definition for pipeline arch                 | 82  |

| 13     | Top kernel fuction for pipeline arch                   | 82  |

| 14     | Header for fix point type                              | 91  |

| 15     | Header for integer type                                | 94  |

| 16     | Fixed point representation of decision tree function . | 94  |

| 17     | Integer representation of decision tree function       | 95  |

## Περίληψη

Οι Βιομηγανικές Εγκαταστάσεις πάντα είναι στόχος επιθέσεων σε διάφορες μορφές όπουν έχουν επιπτώσεις σε κοινωνικό, οικονομικό και αχόμα και πολιτικό επίπεδο. Η ενσωμάτωση προηγμένων πληροφοριαχών τεχνολογιών, όπως το Διαδίχτυο των Πραγμάτων, σε τέτοια περιβάλλοντα τα έχει εκτεθεί σε ζητήματα ασφαλείας του ψηφιακού κόσμου και έχει φέρει στο προσκήνιο κυβερνοεπιθέσεις. Μια δημοφιλής στρατηγική για την προστασία των βιομηχανικών εγκαταστάσεων από τέτοιου είδους επιθέσεις είναι η ανάπτυξη αλγορίθμων και μεθόδων ανίχνευσης βασισμένων σε μηχανική μάθηση, καθώς και σε ανάλυση χρονοσειρών. Η πρόκληση σε αυτές τις περιπτώσεις είναι να αναπτυχθούν γρήγορες, ακόμα και πραγματικού χρόνου λύσεις, που ανιχνεύουν και ακόμα αποτρέπουν κακόβουλες επιθέσεις. Σε αυτήν την διπλωματική εργασία, προτείνουμε την επιτάχυνση FPGA για ένα προγνωστικό μοντέλο που ανιχνεύει κυβερνοφυσικές επιθέσεις σε μια ασφαλή μονάδα επεξεργασίας νερού (SwaT). Η βιβλιογραφία δείχνει ότι τα μοντέλα μηχανικής μάθησης Random Forest εμφανίζουν υψηλή αχρίβεια στην ανίχνευση τέτοιων επιθέσεων. Ο στόχος της διατριβής είναι η επιτάχυνση της εκτίμησης βασισμένης στο Random Forest (RF) μέσω της χρήσης του πλαισίου High Level Synthesis (HLS) Vitis, προσανατολιζόμενο σε μια συσκευή FPGA. Προτείνουμε μια ιεραρχική στρατηγική βελτιστοποίησης που στοχεύει στην ενίσχυση της απόδοσης μέσω της συνεργασίας τεχνικών βελτιστοποίησης του χώδιχα πηγής και τεχνιχών παραλληλισμού που είναι ενσωματωμένες στο HLS. Σε ένα πρώτο επίπεδο, ενεργοποιούμε τον παραλληλισμό εντός της εκτέλεσης μιας μόνο εργασίας Random Forest. Σε ένα δεύτερο επίπεδο, εξερευνούμε τον παραλληλισμό σε πολλαπλούς Random Forests με δύο διαφορετικές αρχιτεκτονικές: (i) ένα coarse grained design που διευχολύνει τον παράλληλο χειρισμό μέσω πολλαπλών instances ενός μόνο σχεδιασμού RF και (ii) έναν σχεδιασμό throughput-optimized που βασίζεται στην παράλληλη εκτέλεση πολλαπλών Random Forests μέσω μιας ακολουθίας ομοιογενών μονάδων επεξεργασίας. Τέλος, σε αυτά τα δύο επίπεδα παραλληλισμού εφαρμόζεται η τεχνική precision scaling που επιτυγχάνει επιπλέον ενίσχυση της απόδοσης μέσω της εκτέλεσης λιγότερο πολύπλοκων λειτουργιών και αποτελεσματικής χρήσης πόρων. Η παραπάνω στρατηγική ενσωματώνεται επιπλέον σε ένα αυτοματοποιημένο πλαίσιο που πραγματοποιεί μια εξερεύνηση πάνω σε ένα σύνολο εξεταζόμενων παραμέτρων

και παρέχει ένα παρέτο με λύσεις που επιτυγχάνουν έναν συμβιβασμό μεταξύ απόδοσης και χρήσης πόρων. Οι παραγόμενοι σχεδιασμοί αξιολογούνται έναντι της εκτέλεσης C++ και Python για διάφορα μεγέθη εισόδου, επιτυγχάνοντας μέγιστη επιτάχυνση  $\times 20.03$ .

Λέξεις κλειδιά: Ανίχνευση ανωμαλιών, Βιομηχανικές Εγκαταστάσεις, Επυτάχυνση σε FPGA, Vitis HLS Tool, Scikit Learn

#### Abstract

Industrial facilities have always been the target of attacks in various forms and impact on a social, economic and even political level. The integration of advanced information technologies such as the Internet of Things in such environments has exposed them to security issues of the digital world and have brought forward cyber attacks. A popular strategy to protect industrial facilities from such attacks, is to develop detection algorithms and methods based on machine learning as well as time series analysis. The challenge in this cases is to develop quick, even real-time solutions, that detect and even deter malicious attacks. In this work, we propose FPGA acceleration for a predictive model that detects cyber-physical attacks at a Secure Water Treatment facility (SwaT). Literature shows that Random Forest machine learning models exhibit high accuracy in the detection of such attacks. The goal of the thesis is to accelerate the Random-Forest(RF)-based inference through the use of High Level Synthesis framework Vitis HLS targeting an FPGA device. We propose a hierarchical optimization strategy that targets performance enhancement through the synergy of source code optimization techniques and HLS-inherent parallelization techniques. On a first level, we enable parallelism within the execution of a single Random Forest inference task. On a second level, we explore parallelism across multiple Random Forests by proposing two different architectures: (i) a coarse-grained design that facilitates parallel execution through multiple instances of a single RF design and (ii) a throughput-optimized design that is based on pipelined execution of multiple Random Forest across an array of homogeneous Processing Units. Lastly, these two levels of parallelism are coupled with a precision scaling exploration that achieves further performance enhancement through the execution of less complex operations and efficient resources utilization. The above strategy is further enclosed in an automated framework that performs an exploration over a set of examined parameters and delivers a pareto front with solutions that achieve a trade-off between performance and resources utilization. The generated designs are evaluated against C++ and python inference for various inputs sizes achieving a speedup of almost  $\times 20.03$ .

**Key words:** Anomaly Detection, Industral Facilities, Acceleration on FPGA, Vitis HLS Tool, Scikit Learn

## Ευχαριστίες

Θα ήθελα, εν πρώτοις, να ευχαριστήσω τον επιβλέποντα καθηγητή κ. Δημήτρη Σούντρη για την εμπιστοσύνη που μου έδειξε για την εκπόνηση της παρούσας διπλωματικής αλλά και την μοναδική εκπαιδευτική εμπειρία που αυτή μου προσέφερε. Επιπλέον θέλω να ευχαριστήσω την υποψήφια διδάκτρορα κα. Κωνσταντίνα Κολιογεώργη, τον Επίκουρο Καθηγητή Γιώργο Λεντάρη και τον υποψήφιο διδάκτρορα Δημήτρη Δανόπουλο για τις συμβουλές τους και την καθοδήγησή τους σε όλα τα στάδια εκπόνησης της παρούσας εργασίας. Κλείνοντας, θα ήθελα να ευχαριστήσω τους φίλους μου χάρη στους οποίους τα φοιτητικά χρόνια θα μου μείνουν αξέχαστα αλλά και τους γονείς μου και τα αδέρφια μου, Φανούρη και Μαριαλένα, για την αμέριστη στήριξη που μου έδειξαν κατά τη διάρκεια των σπουδών μου.

## 1 Εκτενής Περίληψη

#### 1.1 Εισαγωγή-Κίνητρο

Τα τελευταία χρόνια παρατηρείται ότι όλο και περισσότερες Βιομηχανικές Εγκαταστάσεις γίνονται στόχο επίθεσεων. Πολλά από αυτά τα συστήματα δεν είχαν σχεδιαστεί με γνώμονα την ασφάλειά. Μέχρι πρότινος οι τεχνολογίες λειτουργίας ήταν διαχωρισμένες από τις τεχνολογίες πληροφορίας. Επιπλέον απαιτούνταν εξειδικευμένες γνώσεις για τον χειρισμό και την ορθή λειτουργία αυτών. Λόγω αυτών οι Βιομηχανικές εγκαταστάσεις ήταν πιο ασφαλείς σε σχέση με σήμερα. Η συνεχως αυξανομενη ανάπτυξη και ζήτηση της τεχνολογίας Internet of Things(IoT) έχει ενισχύσει το παραπάνω φαινόμενο. Παρά τα ξεκάθαρα οφέλη, σχετικά με την παραγωγικότητα, την αποδοτικότητα και την αυτοματοποίηση, που προσφέρει η ενσωμάτωση του IoT και η διασύνδεση των συστημάτων ελλοχεύει ο κίνδυνος να εκτεθούν περισσότερες αδυναμίες.

Προχειμένου να διασφαλύσουμε τις βιομηχανικές εγκαταστάσεις από τέτοιου είδους επιθέσεων χρειάζεται ο ταχύς εντοπισμός αυτών και η ανάπτυξη αποτρεπτικών μηχανισμών. Σκοπός αυτής της διπλωματικής εργασίας είναι ο σχεδιασμός ενός ισχυρού προβλεπτικού μοντέλου που θα μπορεί να εντοπίσει τέτοιου είδους επιθέσεις και να το επιταχυνουμε κατα το inference. Για να πετύχουμε αυτό κάνουμε Anomaly Detection με χρήση αλγοριθμων μηχανικής μάθησης, όπως ο Random Forest ensembler. Το παραγόμενο αυτό μοντέλο επιλέξαμε να το επιταχύνουμε σε FPGA δειςε με την βοήθεια του εργαλείου Vitis HLS.

Η ανίχνευση ανωμαλιών, γνωστή και ως ανίχνευση ακραίων τιμών, αναφέρεται στο πρόβλημα της εύρεσης μοτίβων σε δεδομένα που δεν συμμορφώνονται με την αναμενόμενη συμπεριφορά. Κυρίως επικεντρωνόμαστε .Χρησιμοποιώντας ιστορικά δεδομένα εκπαιδευουμε το μοντέλο Random Forest για να κάνει τέτοιες προβλεψεις. Random Forest είναι ένας αλγόριθμος supervised learning όπου αποτελείται από μια συλλογή από Decision Trees. Κάθε Decision Tree εκπαιδευεται ανεξαρτητα απο τα υπολοιπα σε ενα υποσύνολο από το αρχικό dataset. Για να προκύψει κάποια πρόβλεψη κάθε δέντρο κάνει ανεξαρτητα την δική του και ύστερα αυτές συλλέγονται. Στην δική μας περίπτωση όπου μας ενδιαφέρει το classification, η τελική προβλεψη εξάγεται με majority voting.

Μια από τις κύριες προκλήσεις που σχετίζονται με την εφαρμογή real-time anomaly detection είναι το γρήγορο και αξιόπιστο infer-

ence. Στην εργασία μας προτείνουμε να χρησιμοποιήσουμε Field Programmable Gate Arrays (FPGA) και το toolchain Vitis-HLS. Οι δυνατότητες παραλληλίας που προσφερουν τα FPGA μας επιτρέπει να μειώσουμε αισθητά το χρόνο inference, κάτι απαραίτητο για real-time και security critical εφαρμογές σαν την δική μας. Επιπλέον, μέσω το Vitis μπορούμε να γράψουμε τον κώδικα μας σε high level γλώσσα όπως η C++ και όχι σε γλώσσα περιγραφής υλικού όπως Verilog ή VHDL. Μας δίνει την ευελιξία και ευκολία να μπορούμε να επικεντρωθούμε στην βελτίωση του design του αλγοριθμου και όχι στην υλοποίηση του σε low-level.

Στα πλαίσια αυτής της διπλωματικής εργασίας, εξετάσαμε τη δυνατότητα παραλληλοποίησης του αλγορίθμου RF για την επίτευξη επιτάχυνσης. Στο εσωτερικό ενός RF, κάθε Decision Tree είναι ανεξάρτητο από τα υπόλοιπα, και αυτό αποτελεί το πρώτο επίπεδο παραλληλίας που εκμεταλλευτήκαμε. Δημιουργήσαμε διάφορα αντίγραφα σε hardware για κάθεDT, επιτρέποντας την παράλληλη εκτέλεσή τους.

Εξερευνήσαμε επίσης υψηλότερα επίπεδα παραλληλίας, όπως αυτό της παράλληλης επεξεργασίας πολλαπλών δειγμάτων εισόδου. Προτείναμε δύο διαφορετικές αρχιτεκτονικές. Η πρώτη, Coarse Grained Multiple RF, περιλαμβάνει πολλαπλές αντίγραφες του ίδιου RF, με παράλληλους decision tree estimators σε κάθε ένα εξ΄ αυτών. Αυτό επιτρέπει την παράλληλη εκτέλεση πολλαπλών ινπυτς ταυτόχρονα. Υπάρχει σαφής συμβιβασμός μεταξύ απόδοσης και χρήσης πόρων, τον οποίο αναλύσαμε λεπτομερώς.

Η δεύτερη προτεινόμενη αρχιτεκτονική ονομάζεται Pipelined RF. Διαπιστώσαμε ότι η διαδικασία διάσχυσης ενός DT μπορεί να κατακερματιστεί σε ανεξάρτητα στάδια. Χρησιμοποιώντας buffers, μετατρέψαμε τη διαδικασία σε pipeline. Συνδυάσαμε παράλληλα και ανεξάρτητα pipelined DTs για να δημιουργήσουμε σε υψηλό επίπεδο ένα pipelined RF. Το pipelined RF μπορεί να δέχεται νέα δείγματα εισόδου σε κάθε κύκλο, επιτρέποντας την παραλληλή διαχείριση τους και την επίτευξη χαμηλού latency. Και στις δύο αρχιτεκτονικές, εφαρμόσαμε την τεχνική precision scaling για βελτίωση της απόδοσης κατά το inference και μείωση της χρήσης πόρων.

Στο υπόλοιπο της διπλωματικής εργασίας, παρουσιάσαμε την μεθοδολογία μας, τα αποτελέσματα της εφαρμογής των διαφορετικών τεχνικών και τις συγκρίσεις με C++ και Python υλοποιήσεις του RF αλγορίθμου. Εκτελέσαμε ανάλυση δεδομένων στα ευρήματα και παρουσιάσαμε συμπεράσματα, κλείνοντας με μια ματιά στο μέλλον και τη δημιουργία

ενός εργαλείου που αυτοματοποιεί τη διαδικασία του design exploration.

#### 1.2 Σχετική Εργασία

Η Ανιχνεύση Ανωμαλιών είναι ένα ευρέως ευρημενό ζήτημα. Πολλές διαφορετικές προσεγγίσεις έχουν δοκιμαστεί στην προσπάθεια ανάπτυξης ενός αξιόπιστου μοντέλου. Μια από αυτές αφορά την σύγκριση Support Vector Classifires(SVM) και Random Forest(RF). Οι συγγραφείς του παπερ χρησιμοποιούν 2 διαφορετικά datasets που αφορουν Intrusion Detection(ID) σε βιομηχανικές εγκαταστάσεις. Σε μια άλλη έρευνα, επιδιωξαν να αναπτύξουν ένα έξυπνο και ασφαλές μοντέλο για να ανιχνεύουν αδυναμίες σε ΙοΤ συστήματα και να προστατεύονται από cyber-attacks. Για να το καταφέρουν αυτό, σύγκριναν πολλούς διαφορετιχούς αλγόρυθμους μηχανιχής μάθησης. Συνολιχά χρησιμοποιήθηκαν 5, οι οποίοι ήταν Logistic Regression(LR), Support Vector Machine, Decision Trees(DT), Random Forest και Artificial Neural Networks (ANN). Συμπέραναν ότι ένα απλό μοντέλο όπως το PΦ μπορεί, σε συνάρτηση πάντα με το δατασετ, να φέρει καλύτερα αποτελέσματα όσον αφορά την αχρίβεια των προβλέψεων σε συγχρίση με πολύ πιο περίπλοκα σαν το ΑΝΝ.

Είναι εμφανές ότι ο RF, χάρις στη καλή ακρίβεια και τους γρήγορους χρόνους εχπαίδευσης και εχτέλεσης, είναι μια δημοφιλής επιλογή στο χώρο του anomaly detection. Πάντα υπάρχει όμως η ανάγκη για πιο ακριβή, ταχύτερές και ενεργεικά συμφέρουσες λύσεις. Λόγω αυτού, έχουν γίνει προσπάθειες για επιτάχυνση του μοντέλου σε πληθώρα hardware πλατφορμών, όπως GPU και FPGA. Μία από αυτές είναι το παπερ όπου χρησιμοποιείσαι μια παραλλαγή του κλασικού αλγόριθμου RF, η οποία είναι Compact Random Forest(CRF). Οι βασικές διαφορές τους είναι στο πλήθος των DT και στο μέγιστο δεπτη που επιτρέπεται να μεγαλώσει κάθε δέντρο. Η ανάγκη για αυτές τις αλλαγές προχύπτει από το γεγονός ότι ο ΡΦ αλγόριθμος είναι memory bound κάτι το οποίο δεν ενδείκνυται για hw acceleration, με περιορισμένους πόρους. Στην υλοποίηση σε FPGA προτείνεται μια pipeline αρχιτεκτονική με N διαφορετικά piplines για N δέντρα. Στην υλοποίηση CP-GPU, εστιάζουν στον μέγιστο εκμεταλλευτικό παραλληλισμό σε πολυπύρηνες μονάδες και την επίτευξη βέλτιστης επαναχρησιμοποίησης δεδομένων στις μνήμες cache. Η μελέτη καταλήγει στο συμπέρασμα ότι τα FPGA παρέχουν υψηλότερη απόδοση ανά watt και μπορούν να χειριστούν μεγαλύτερους ταξινομητές χωρίς να υπονομεύουν τις δυνατότητές τους.

Βασισμένοι στα προηγούμενα, αποφασίσαμε να πραγματοποιήσουμε Ανίχνευση Ανωμαλιών χρησιμοποιώντας Random Forest σε ένα FPGA. Καταρχάς, δεν θα επιβάλουμε κανέναν περιορισμό στο μέγεθος του RF κατά την εκπαίδευση. Επιπλέον, θα συγκρίνουμε δύο διαφορετικές αρχιτεκτονικές στο FPGA. Μια αρχιτεκτονική είναι προσέγγιση pipeline, παρόμοια με αυτή που προτάθηκε στο άρθρο, ενώ η άλλη εμπλέκει μια πιο παράλληλη υλοποίηση.

Χάρη στις αυξημένες δυνατότητες των σύγχρονων FPGAs, θα στοχεύσουμε στο να επιτύχουμε τον μέγιστο δυνατό αριθμό παράλληλων και ανεξάρτητων περιπτώσεων RF που μπορούν να χωρέσουν στον πίνακα. Όλες οι περιπτώσεις θα είναι πανομοιότυπα αντίγραφα μεταξύ τους. Εσωτερικά, τα δέντρα θα επεξεργαστούν κάθε δείγμα παράλληλα σε και τις δύο προτεινόμενες αρχιτεκτονικές. Στόχος μας είναι να συγκρίνουμε ποια από τις δύο προσεγγίσεις, σωληνωτή ή παράλληλη, θα μας παρέχει υψηλότερη απόδοση και να εξετάσουμε την ισορροπία μεταξύ πόρων και απόδοσης.

#### 1.3 Random Forest Αλγόριθμος

Ο αλγόριθμος RF προτάθηκε πρώτη φορά από τον Leo Breiman. Συνδίασε πολλές τεχνικές και πρότεινε καινούργιες. Αποτελεί μια παραλλαγή του CART αλγορίθμου στον οποίο εφαρμόστηκε βαγγινγ και τυχαία επιλογή χαρακτηριστικών . Ο CART αλγόριθμος είναι δύσκολο να μην κάνει overfit τα δεδομένα και συμπεριφερεται μη αποδοτικά σε ουτλιερς. Ο Breiman πρότεινε να χρησιμοποιηθει η τεχνική bagging ή αλλιώς bootstrap aggregating. Στο Bagging πολλοί αδύναμοι [λεαρνερς] εκπαιδεύονται παράλληλα ο καθένας σε διαφορετικό σύνολο δεδομένων, το οποίο προκύπτει με τυχαία ανακατομή του αρχικού. Το σύνολο των δεδομένω όπου εκπαιδεύεται ο κάθενας learner(classifier ή regressor) παράγεται τραβόντας Ν δείγματα με επανατοποθέτηση, όπου Ν είναι το μέγεθος του αρχικού. Ο στόχος μας είναι εκπαιδεύοντας κάθε δέντρο,στη δική μας περίπτωση, με διαφορετικό σύνολο δεδομένω να γινει το μοντέλο πιο ανθεκτικό σε νέα δείγματα. Τα δέντρα που παράγονται από την παραπάνω διαδικασία στη συνέχεια αποφασίζουν συλλογικά για τη πρόβλεψη σε κάθε νέα είσοδο. Στη περίπτωση του classification η απόφαση παίρνεται με ψηφοφορία ενώ του regression με το μέσο όρο απο όλες τις προβλέψεις των δέντρων.

Στα περισσότερα σύνολα δεδομένων, υπάρχουν κάποια χαρακτηριστικά που φαίνεται να υπερτερουν των άλλων στη λήψη των αποφάσεων

κατα την διχοτομήση των κόμβωβ και κατα επακόλουθο στη κατασκευή των δέντρων. Ακόμα και με bootstrap φαίνεται ότι τα παραγόμενο δέντρα δεν καταφερνουν να διαφοροποιηθούν αρκετα μεταξυ τους για να αντιμετωπιστεί το overfitting. Ο Breiman προσπαθησε να εντάξει περισσότερη τυχαιότητα στο μοντέλο με στόχο να μειώσει το συσχέτιση του ενος δέντρου από το άλλο και να αυξήσει ή να διατηρήσει την προβλεπτική ικανότητα του καθενός. Πρότεινε να μην χρησιμοποιείται ολοχληρο το εύρος των χαραχτηριστών σε κάθε κόμβο αλλά ένα τυχαίο υποσύνολο αυτών. Το χαρακτηριστικό και η τιμη του που θα καταλήξουμε να κάνουμε διχοτομηση του κόμβου επιλέγεται από αυτό το τυχαίο υποσύνολο. Το πλήθος αυτών είναι σταθερό για όλους κόμβους όλων των δεντρων και συνήθως αποτελεί μια συνάρτηση του συνολικού μεγέθους των χαρακτηρισικών. Μία από τις πιό σύνηθες και αυτή που καταλήγουμε είναι η τετραγωνική ρίζα, άλλη επίσης ευρέως χρησιμοποιούμενη ο λογάριθμος του.Η προσθήκη των παραπάνω τεχνικών συμβάλλει στην εισαγωγή ποικιλίας μεταξύ των δέντρων και στη βελτίωση της ικανότητας του μοντέλου να γενικεύει. Αυτό αντιμετωπίζει προβλήματα όπως το overfitting και ενισχύει τη συνολική απόδοση.

Η διαδικασία inference ενός Ρανδομ Φορεστ περιλαμβάνει τα εξής βήματα:

- Είσοδος: Για κάθε δείγμα Ξ για το οποίο θέλουμε να κάνουμε μια πρόβλεψη, το  $P\Phi$  παίρνει αυτόν τον διάνυσμα χαρακτηριστικών ως είσοδο.

- Διάσχιση Δέντρου:Η είσοδος περνά σε κάθε δέντρο απόφασης.

Ξεκινώντας από τη ρίζα, το δείγμα διασχίζει τη δομή του δέντρου βασιζόμενο στα κριτήρια διαίρεσης σε κάθε εσωτερικό κόμβο. Σε κάθε εσωτερικό κόμβο, χρησιμοποιείται ένα συγκεκριμένο χαρακτηριστικό και σημείο διαίρεσης για να καθοριστεί η κατεύθυνση που πρέπει να ακολουθήσει το δείγμα. Η τιμή του χαρακτηριστικού στο δείγμα εξετάζεται σε σχέση με το σημείο διαίρεσης, και με βάση το αποτέλεσμα, το δείγμα μετακινείται στον αριστερό ή δεξιό κόμβο-παιδί. Αυτή η διαδικασία συνεχίζεται αναδρομικά μέχρι το δείγμα να φτάσει σε ένα φύλλο κόμβου, που αντιπροσωπεύει μια πρόβλεψη.

- Ψηφοφορία ή Μέσος Όρος:Τα δέντρα κάνουν συλλογικές προβλέψεις για κάθε είσοδο. Σε εργασίες δυαδικής ταξινόμησης, κάθε δέντρο αποφάσισης "ψηφίζει' για μια ετικέτα τάξης βασισμένη

στην πλειοψηφική κλάση στο φύλλο κόμβου όπου καταλήγει το δείγμα εισόδου. Η τελική πρόβλεψη γίνεται μέσω πλειοψηφικής ψηφοφορίας μεταξύ όλων των δέντρων απόφασης. Σε εργασίες παλινδρόμησης, οι προβλεπόμενες τιμές από κάθε δέντρο αποφάσεων λαμβάνονται μέσο όρο για να προκύψει η τελική έξοδος παλινδρόμησης.

Έξοδος:Το RF εξάγει την τελική πρόβλεψη για το δείγμα εισόδου, η οποία μπορεί να είναι μια ετικέτα τάξης (σε κατηγοριοποίηση) ή αριθμητική τιμη (σε παλινδρόμηση)

#### 1.4 FPGA & HLS Εργαλεία

Ένα FPGA είναι ένα ενσωματωμένο κύκλωμα (IC) που μπορεί να προγραμματιστεί για διάφορους αλγόριθμους μετά την κατασκευή. Τα σύγχρονα FPGAs αποτελούνται από έως δύο εκατομμύρια λογικά κελιά που μπορούν να διαμορφωθούν για την υλοποίηση διάφορων λογισμικών αλγορίθμων. Παρόλο που η παραδοσιακή διαδικασία σχεδιασμού σε FPGA είναι περισσότερο παρόμοια με ένα κανονικό ΙΟ παρά με έναν επεξεργαστή, ένα FPGA παρέχει σημαντικά οφέλη σε κόστος και χρόνο συγκριτικά με μια προσπάθεια ανάπτυξης ΙΟ και προσφέρει τον ίδιο βαθμό απόδοσης στις περισσότερες περιπτώσεις. Αυτό οφείλεται στη δυνατότητα του FPGA, σε σύγκριση με το IC, να ανακατασκευάζεται δυναμικά. Αυτή η διαδικασία, που είναι παρόμοια με το να φορτώνετε ένα πρόγραμμα σε έναν επεξεργαστή, κάνει αλλαγές στο πραγματικό υλικό και τους διαθέσιμους πόρους στο υλικό του FPGA.Η γενική αρχιτεκτονική του FPGA είναι ετερογενής πλατφόρμα υπολογισμού που αποτελείται από τρία είδη μονάδων. Αυτές είναι οι μονάδες εισόδου/εξόδου, οι μονάδες διακοπής/διασύνδεσης καλωδίων και οι διαμορφώσιμες λογικές μονάδες (CLB).

Η Σύνθεση Υψηλού Επιπέδου (High-Level Synthesis - HLS) είναι η διαδικασία μετατροπής μιας προδιαγραφής σε γλώσσα C σε ένα επίπεδο μεταφοράς καταχωρητών (Register Transfer Level - RTL) για να μπορεί να συνθετιστεί σε ένα FPGA. Αποτελεί γέφυρα μεταξύ λογισμικού και υλικού, επιτρέποντας στους σχεδιαστές να εκφράσουν τα σχέδιά τους χρησιμοποιώντας γλώσσες προγραμματισμού υψηλού επιπέδου όπως η C ή C++. Η HLS προσφέρει αρκετά πλεονεκτήματα σε σύγκριση με τις παραδοσιακές γλώσσες περιγραφής.

Ορισμένα από αυτά περιλαμβάνουν τα εξής. Αφαιρώντας τις λεπτομέρειες σε χαμηλό επίπεδο, οι σχεδιαστές μπορούν να επικεντρ-

ωθούν στο να εκφράσουν την επιθυμητή λειτουργικότητα των σχεδίων τους, αφήνοντας τις λεπτομέρειες υλοποίησης στο εργαλείο HLS. Επίσης, μπορεί να επικυρώσει τη λειτουργική ορθότητα του σχεδιασμού πιο γρήγορα σε σύγκριση με τις VHDL ή Verilog. Οι πολλές οδηγίες βελτιστοποίησης που είναι διαθέσιμες επιτρέπουν έλεγχο επάνω στη διαδικασία σύνθεσης και δημιουργούν ειδικές υλοποιήσεις υψηλής απόδοσης. Με τη βοήθεια των οδηγιών βελτιστοποίησης, μπορεί να δημιουργήσει πολλαπλές υλοποιήσεις από τον πηγαίο κώδικα C. Τέλος, μπορούμε να δημιουργήσουμε αναγνώσιμον και φορητόν πηγαίον κώδικα C, να επαναστείλουμε τον πηγαίο κώδικα C σε διάφορες συσκευές και να τον συμπεριλάβουμε σε νέα έργα.

Μόλις ολοκληρωθεί η σύνθεση του κώδικα από το HIS παράγεται μια αναφορά σύνθεσης. Πληροφορίες σχετικά με τα μετρήσιμα κριτήρια απόδοσης παρέχονται σε αυτήν την αναφορά. Η κατανόηση των κριτηρίων που χρησιμοποιούνται για να μετρήσουν την απόδοση σε ένα σχεδιασμό που δημιουργήθηκε με τη χρήση της HLS είναι κρίσιμη για να επιτευχθεί αυτό αποτελεσματικά. Τα τρία βασικά από αυτά είναι η έκταση (Area), η καθυστέρηση (Latency) και το διάστημα εκκίνησης (Initiation Interval - II).

Χρησιμοποιήσαμε την Ενοποιημένη Πλατφόρμα Vitis για την επιτάχυνση της εφαρμογής μας. Η εφαρμογή χωρίζεται κυρίως σε δύο μέρη, τον κεντρικό υπολογιστή (host) και το FPGA. Ο κεντρικός υπολογιστής λειτουργεί ως η κύρια μονάδα επεξεργασίας που αλληλεπιδρά με το FPGA για την εκτέλεση συγκεκριμένων εργασιών. Ο σκοπός του κεντρικού υπολογιστή είναι ο έλεγχος, η συντονισμός και η επικοινωνία με το FPGA για την ανάληψη υπολογιστικών εργασιών ή την επιτάχυνση συγκεκριμένων τμημάτων μιας εφαρμογής. Ο επεξεργαστής του κεντρικού υπολογιστή επικοινωνεί με το FPGA για τη μεταφορά δεδομένων, παραμέτρων διαμόρφωσης και οδηγιών. Διαμορφώνει το FPGA για την εκτέλεση, στέλνει δεδομένα για επεξεργασία από πυρήνες FPGA και λαμβάνει πίσω τα αποτελέσματα από το FPGA. Επίσης, είναι υπεύθυνος για τον έλεγχο της εκτέλεσης εργασιών στο FPGA. Βεβαιώνεται για τον σωστό συγχρονισμό μεταξύ των εργασιών που τρέχουν στον κεντρικό υπολογιστή και στο FPGA για τη διατήρηση της σωστής αχολουθίας λειτουργιών. Ένας άλλος χρίσιμος ρόλος του κεντρικού υπολογιστή είναι η Προεπεξεργασία και Μεταεπεξεργασία Δεδομένων.

## 1.5 Υλοποίηση του Random Forestγια Σύνθεση Υψηλού Επιπέδου

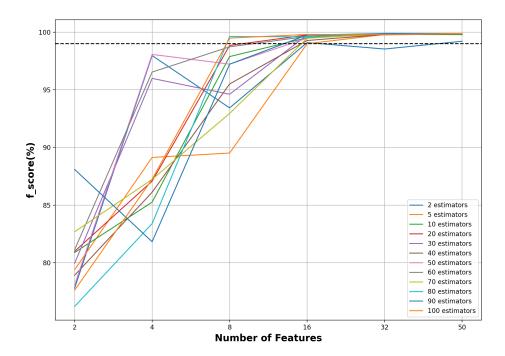

Για το κομμάτι του τραινινγ χρησιμοποιήθηκε η python βιβλιοθήκη Scikit-learn. Η Scikit-learn μας έδωσε την δυνατότητα να παραμετροποιήσουμε το μοντελο στις ανάγχες της εφαρμογής μας. Εξετάσαμε πολλές παραμέτρους για την εκπαίδευση των μοντέλων μας.Οι δύο κρίσιμες παράμετροι που επιλέξαμε να εξερευνήσουμε είναι ο αριθμός των εχτιμητών και ο αριθμός των χαρακτηριστικών. Επικεντρωθήκαμε σε αυτές τις δύο επειδή μπορούσαμε να τις εξερευνήσουμε χωρίς να κάνουμε βαριές υποθέσεις σχετικά με το σύνολο δεδομένων και τη διαδικασία δημιουργίας των δέντρων. Ακόμα και για τον ίδιο αριθμό χαρακτηριστικών, δημιουργούνται διάφορα δέντρα, δεδομένου ότι η επιλογή των χαρακτηριστικών είναι τυχαία. Αυτά τα δέντρα έχουν διαφορετιχούς μεγέθη και δομές, επομένως η οριοθέτηση στην ανάπτυξή τους οδηγεί σε σημαντική μείωση της ακρίβειας. Επίσης, αυτό το όριο θα ήταν ανεπιτυχές επειδή η δημιουργία του δέντρου είναι μη-ντετερμινιστική. Ο λόγος διαίρεσης που επιλέχθηκε, βασισμένος σε γενικές πρακτικές, είναι 70/30. Το 70% του συνόλου δεδομένων χρησιμοποιήθηκε για την εκπαίδευση και το άλλο 30% για τον έλεγχο.Οι μετρικές που αξιολογήσαμε ήταν η Ακρίβεια (Accuracy), η Ανάκληση (Recall), η Ακρίβεια (Precision) και το F-σκορ.

Εκπαιδεύσαμε τα μοντέλα χρησιμοποιώντας τη γλώσσα προγραμματισμού Πψτηον, όπως αναφέρθηκε προηγουμένως, με διάφορους συνδυασμούς των εκτιμητών και των χαρακτηριστικών. Για κάθε ένα από αυτά τα μοντέλα, καταγράψαμε τις μετρήσεις F-σκορ κατά τη διάρκεια του συμπερασμού στο σύνολο δεδομένων ελέγχου. Αποκλείουμε τα μοντέλα με F-σκορ ° 99% από τη συνεχόμενη ανάλυσή μας για να διατηρήσουμε αυτά με την καλύτερη προβλεπτική ικανότητα.

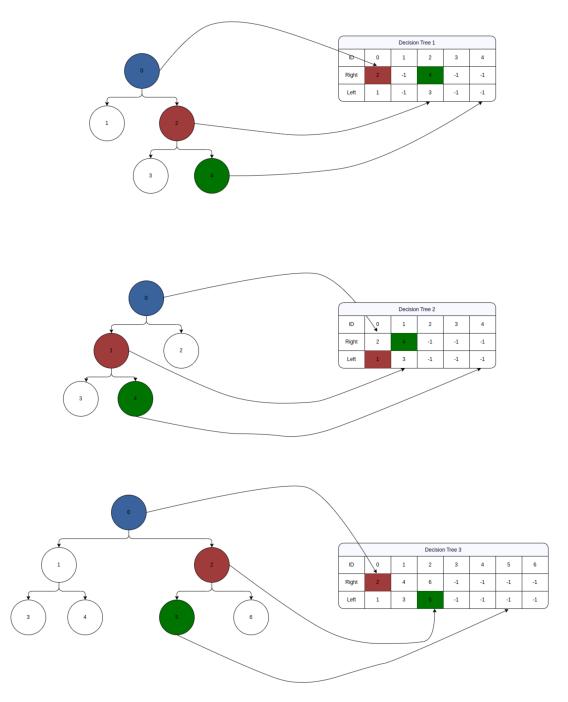

Μεταφέραμε την Python υλοποίηση σε C++ κωδικά κατάλληλο για να μπορεί να εκτελείται μέσω του Vitis. Αποθηκεύουμε την δομή των Δέντρων Απόφασης σε πίνακες. Για την ανακατασκευή σε C++, θα χρειαστούμε πέντε συγκεκριμένους πίνακες: children left, children right, feature, threshold, και value.Περεταίρω αλλαγές πρέπει να γίνουν ώστε να εκτελείται ο κώδικας χρησιμοποιώντας το HLS. Δεδομένου ότι η εντολή while δεν υποστηρίζεται από το εργαλείο, πρέπει να δημιουργηθεί ένας βρόγχος φορ αντί αυτού. Το αναμενόμενο όριο του βρόγχου for είναι το μήκος της διαδρομής μέχρι να φτάσουμε σε ένα φύλλο. Το μήκος της μακρύτερης διαδρομής θεωρείται ως ένα άνω όριο, διότι είναι δύσκολο να προβλέψουμε ποια από

όλες τις πιθανές διαδρομές θα αχολουθηθεί. Το μήχος της μαχρύτερης διαδρομής υπολογίζεται χρησιμοποιώντας τον αλγόριθμο DFS. Στον χώδιχα, χρησιμοποιήσαμε διανύσματα (vectors) επειδή χατά την εξερεύνηση του χώρου σχεδίασης, ένα από τα παράμετρα που ρυθμίζουμε είναι ο αριθμός των χαραχτηριστιχών. Ωστόσο, η δυναμιχή εχχώρηση μνήμης δεν υποστηρίζεται στο Vitis, επομένως αντιχαταστήσαμε τα διανύσματα με στατιχά διαμορφωμένους πίναχες.

## 1.6 Αρχιτεκτονικές βελτιστοποιήσεις του Random Forest βασισμένες στο HLS

#### 1.6.1 Παραλληλισμός εσωτερικά του Random Forest

Στόχος της διπλωματικής εργασίας είναι η επιτάχυνση κατά το inference. Προκειμένου να το πετύχουμε το παραπανω αντιμετωπίσαμε αρχικά 2 κύριες προκλήσεις. Η πρώτη πρόκληση είχε να κάνει με το να βρούμε ποία κομμάτια του αλγορίθμου να επιταχύνουμε και πώς αυτό μπορούμε να το υλοποιήσουμε σε αποτελεσμάτικο κώδικα για το εργαλέιο Vitis . Η δεύτερη πρόκληση αφορούσαι στην παραμετροποιήση του παραπάνω κώδικα ώστε να έχουμε το βέλτιστο αξιοποιήση πόρων.

Η πρώτη πρόχληση είναι να μπορέσουμε να μετατρέψουμε την αχουλιαχή εκτέλεση του RF αλγορίθμού σε παράλληλη. Αρχικά έπρεπε να εντοπίσουμε ποιά τμήματα του αλγορίθμου μπορουμε να παρηλλοποιήσουμε. Στη συνέχεια έχοντας βρει ποιά είναι αυτά τα χομμάτια προτείνουμε αλλαγές στο δομή του χώδικα χαθώς και εισάγουμε βοηθιτικές εντολές υπό την μορφή pragmas για να μπορέσουμε όντως να πετύχουμε την επιθυμητή παραλληλια. Οι αποφάσεις παίρνονται με ψηφοφορία απο τους διαφορετιχούς και ανεξάρτητους μεταξύ τους εχτιμητές. Δεν υπάρχει χάποια εξάρτηση στη πρόβλεψη που χάνει χάθε DT, όποτε δεν υπάρχει ανάγχη για σειριαχή εχτέλεση των DT. Αντίθετα προτείνουμε, το inference των DT να γίνεται παράλληλα

Προκειμένου να καταλάβει το Vitis εργάλειο ότι θέλουμε παράλληλη εκτέλεση των εκτιμητών, χρειάστηκε να εφαρμόσουμε pragmas. Πιο συγκεκριμένα προσθέσαμε το pragmas dataflow. Η δήλωση pragma DATAFLOW ενεργοποιεί τον παραλληλισμό σε επίπεδο εργασιών, επιτρέποντας σε συναρτήσεις και βρόγχους να επικαλύπτονται στη λειτουργία τους, αυξάνοντας τον βαθμό συγχρονισμού της υλοποίησης RTL και αυξάνοντας τον συνολικό ρυθμό επεξεργασίας του σχεδιασμού. Η βελτιστοποίηση DATAFLOW επιτρέπει στις λειτουργίες ενός βρόγχου ή μιας συνάρτησης να ξεκινήσουν τη λειτουργία τους

πριν ολοχληρωθούν όλες οι λειτουργίες του προηγούμενου βρόγχου ή συνάρτησης, υπό τον όρο ότι δεν υπάρχουν εξαρτήσεις δεδομένων.

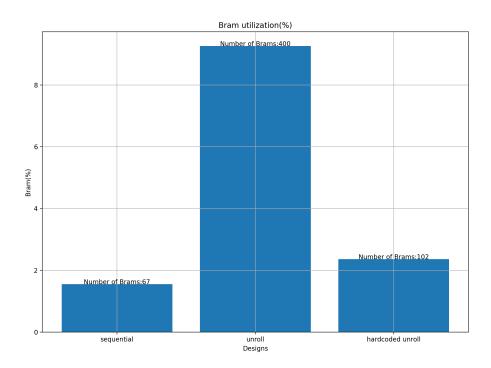

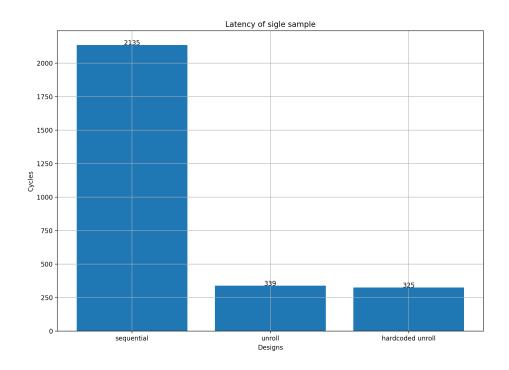

Πετυχαίνουμε παράλληλη εκτέλεση των decision trees εντός ενός rf δηλώνοντας πολλές φορές την ίδια συνάρτηση και εφαρμοζοντας τα απαραίτητα pragmas όπως το dataflow. Η δεύτερη πρόκληση που κλήθηκαμε να αντιμέτωπίσουμε είχε να κάνει με το να διατηρήσουμε την παραπάνω παραλληλία αλλα να μειώσουμε σημαντικά του πόρους που απαιτούνται για την πετύχουμε. Το κύριο πρόβλημα πηγάζει από τον τρόπο που αποθηκεύουμε τους πίνακες των decision trees και επακόλουθα με τον τρόπο που τους διαβαζουμε. Για να το αντιμετωπίσουμε χρειάστηκε να μετακινήθουμε από το την γενικευμένη μορφή κώδικα που επιτρέπει iterative access/execution και να εστίσσουμε σε λύσεις με hardcoded συναρτήσεις για κάθε decision tree που επιφέρουν σημαντική μείωση στην αξιοποιήση πόρων.

#### 1.6.2 Παραλληλισμός μεταξύ πολλών Random Forest

Προηγουμένως αναλύσαμε την μετατροπή από σειριαχή εχτέλεση των εχτιμητών σε παράλληλη. Ωστόσο μπορούμε να πετύχουμε παραλληλία και σε άλλα χομμάτια του αλγορίθμου RF. Κάθε δείγμα εισόδου είναι ανεξάρτητο από τα υπόλληλα. Με δεδομένο αυτο εξερευνήσαμε δυο διαφορετιχές προσεγγίσεις στην αρχιτεχτονιχή του kernel. Η πρωτη αφορά την παράλληλη εχτέλεση διαφορετιχών αντιγράφων του instance του random forest, όπου το χαθενα θα χάνει inference διαφορετιχό δείγμα. Η δεύτερη πρόταση είναι μια pipeline προσέγγιση με στόχο να πετύχουμε Iteration Interval (II) ίσο με 1. Δηλαδή σε χάθε χύχλο ρολογιού να επεξεργάζεται μια χαινουργια είσοδο, ή αντίστοιχα να παράγει μια πρόβλεψη ανά ένα χύχλο.

Η πρώτη αρχιτεκτονική είναι η Coarse Grained Design Parallel RFs. Δημιουργώντας πολλαπλά και ανεξάρτητα αντίγραφα της συνάρτησης ρανδομ φορεστ δίνεται η δυνατότητα για ταυτόχρονη και παράλληλη επεξεργασία εισόδων. Συγκεκριμένα για Κ σε πλήθος παράλληλα RFs εσωτερικά το καθένα έχει Ν παράλληλα. Η αρχιτεκτονική εισάγει ένα έξτρα επίπεδο παραλληλίας, πέρα αυτού των παράλληλων εκτιμητών καθώς έχει την δυνατότητα να επεξεργάζεται ταυτόχρονα Κ εισόδους. Ακουλήθησαμε την ίδια μεθοδολογία όπως και με τους εστιματορς για να πετυχουμε παραλληλία μεταξύ των rfs. Οπως και προηγουμένως χρησιμοποιουμε τα pragma dataflow και array\_parition, για να διασφαλίσουμε την παράλληλη επικαλυπτομενη εκτέλεση.

Προχειμένου να έχουμε αξιόπιστες μετρήσεις τόσο για το χρόνο

inference αλλά και για την αξιοποιήση πόρων κανάμε hw implementation. Όπως είναι αναμενόμενο δημιουργώντας αντίγραφα από RFs πετυχαίνουμε παραλληλία αλλά χρησιμοποιούμε περισσότερους πόρους. Οι πόροι ανά FPGA, σε BRAM, FF και LUT, είναι καθορισμένοι για αυτό πρέπει να βρούμε πόσα αντίγραφα μπορούμε να χωρέσουμε. Ορίσαμε ενα άνω όριο για την χρήση πόρων που θεωρούμε ικανοποιητικό και δε θα θελαμε να υπερβούμε για να διασφαλίσουμε την ορθή λειτουργία του FPGA. Το όριο αυτό είναι 80% των προαναφερθέν πόρων. Κάναμε δυαδική αναζήτηση μέχρι να βρούμε το μέγιστο πλήθος RFs που η χρήση τους δεν θα ξεπερνά 80%. Κατά την εξερεύνηση δοκιμασαμε 1, 2, 4, 8, 16, και 24 παράλληλα RFs.

Παρατηρούμε ότι ο πόρος που μεταβάλλεται περισσότερο είναι η BRAM. Συμπεραίνουμε ότι για κάθε νέο αντίγραφο του RF, δεσμευονται εκ νέου πόροι για τους πίνακες των decision trees. Ένα πιθανός λόγος για αυτή την συμπεριφορά του εργαλείου είναι οι περιορισμένες ports (σε σύνολο 2) για κάθε bram. Είναι δύσκολο να γίνει ο συντονισμός για πρόσβασγ στους ίδιους πίνακες από πολλαπλά RFs. Εντείνει την παραπάνω δυσκολία το γεγονός ότι δεν υπάρχει κάποιο μοτίβο για το ποιά θέση του πίνακα επιδιώκουμε να διαβάσουμε, καθώς έχουμε τυχαία δίασχυση που εξαρτάται από την είσοδο. Όποτε δεν επιτυγχανεται κάποιος διαμοιρασμός των πινάκων με μόνη λύση του εργαλείου την αντιγραφή τους. Δεδομένου αυτό περιμένουμε να υπάρχει γραμμική αύξηση των πόρων σε σχέση με το πλήθος των RFs, όπως και γίνεται

Η δεύτερη προτεινόμενη αρχιτεκτονική είναι η Pipelined Random Forest. Κάθε εκτιμητής μπορει να μπορεί να αναπαρασταθεί ως μια σειρά από S στάδια, με το S να είναι ίσο με μακρύτερο μονοπάτι κάθε δέντρου. Στόχος είναι να μετατραπεί η σειριακή εκτέλεση των S σταδίων σε πιπελινε. Αυτό μπορεί να γίνει τοποθετώντας καταχωρητές μεταξύ των σταδίων. Σε κάθε κύκλο τροφοδοτείται με νέο δείγμα καί ύστερα από την αρχική καθυστέρηση και επιτυγχάνεται II=1.

Δείξαμε ότι ένα decision tree μπορεί να αναπαρασταθεί ως ένα pipeline. Μεταφέρουμε το παραπάνω στο rf, όπου αποτελεί μια συλλογή από ανεξαρτητα dt. Όποτε η προτεινόμενη αρχιτεκτονική απαρτίζεται από ανεξάρτητα εσωτερικά pipelines, τα οποία συνδυάζονται και επιτυγχανεται σε υψηλό επίπεδο η rf να είναι και αυτή pipeline. Για να το πετύχουμε αύτο χρησιμοποιήσαμε το pragma pipeline του Vitis

#### 1.7 Εξερεύνηση με εφαρμογή Precision Scaling

Ο χυρίαρχος πόρος, δηλαδή εχείνος που αλλάζει περισσότερο και καθορίζει σε μεγαλύτερο βαθμό αν μπορεί να υλοποιήθει το σχέδιο, είναι το BRAM. Στόχος λοιπόν είναι διατηρώντας σταθερή την αχριβεια του μοντέλου να μειώσουμε το ποσοστό χρήσης των BRAM. Το καταφέραμε μέσω της τεχνιχής Precision Scaling. Πιο συγχεχριμένα, μειώσαμε το πλήθος από bits που απαιτείται για την αναπαράσταση των στοιχείων των πινάχων των dt. Αθροιστιχά η παραπάνω μείωση μπορεί να έχει μεγάλη επίδραση ιδίως για μεγάλα σχέδια, όπως τα 24 παράλληλα RFs, πετυχένοντας πτώση απο τα 70,69 σε 39,88 BRAM(%).

Το εργαλείο κάνει αυτόματα την μετατροπή από 32-int σε μικρότερου τύπου int. Δεν αναφέρεται κάπου τον τύπο που εντέλει καταλήγει (στα πλάσια που καταφέραμε να ελεγξουμε) αλλά έχει την ίδια απόδοση με τους τύπους αρμιint που ορίσαμε για να ελέγξουμε την παραπάνω υπόθεση. Δεν συμβαίνει και το ίδιο για πίνακα threshold όπου έχει τύπο float. Λόγω της δομής με την οποία αποθηκεύεται ένας float αριθμός δεν είναι δυνατόν να γίνουν αυτόματα βελτιστοποιήσεις σαν την παραπάνω. Δοκίμασαμε δύο διαφορετικές αναπαραστάσεις για τον threshold πίνακα τις : fixed point και integer. Το εργαλείο ἵτις δίνει την δυνατότητα να χρησιμοποιούνται arbitrary precision data types για fixed float και integer.

Κατά την εκπαίδευση των μοντέλων μας το σύνολο των δεδομένων ήταν κανονικοποιημένα μεταξύ (0,1). Όποτε δεν υπάρχει ακέραιο τμήμα και μπορούμε να εστίασουμε καθαρά στο δεκάδικο. Δεδομένου αυτού ο fixed point τύπος θα διαθέσει όλα τα bits, όσα αποφασίσουμε εμείς, μόνο για το δεκαδικό κομμάτι. Η εξερεύνηση που θα κάνουμε αφορά το πλήθος αυτών των bits. Συγκεκρίμενα θα εξετάσουμε 8, 16, 24 και 32 βιτς.

Η fixed point αναπαράσταση μας ώθησε να πειραματήστουμε και με άλλες πίθανες αναπαραστάσεις για τους threshold πίνακες. Αρχικά σκεφτήκαμε την integer αναπαράσταση ορμώμενη από το γεγονός ότι οι πράξεις και συγκρίσεις με integer είναι πιο γρήγορες σε σύγκριση με τους float χάριν της απλούστερης αναπαράστασης. Επιπλέον διαπίστωσαμε στην συνέχεια ότι πέρα της επιπλέον επιτάχυνσης, με integer αναπαράσταση σε ιδιως για χαμηλό precision όπως 16 και 8 bits, το μοντέλο έχει σημαντικά καλύτερή ακρίβεια εν συγκρίση με τους fixed point.

Η μετατροπή ενός float σε integer διατήρωντας τα χαρακτηριστικά την κατανομή τους γίνεται με την τεχνική του κβαντοποιήσης.Η

κβαντοποίηση είναι μια τεχνική για τη μείωση των υπολογιστικών και μνήμης δαπανών κατά την εκτέλεση της πρόβλεψης, αναπαριστώντας τα βάρη και τις ενεργοποιήσεις με χαμηλής ακρίβειας τύπου δεδομένων, όπως το 8-bit integer (int8) αντί του συνηθισμένου 32-bit floating point (float32). Το πλάνο κβαντοποίησης που εφαρμόσαμε είναι βασισμένο στη συνάρτηση εύρους . Η γραμμική κβαντοποίηση μετατρέπει τις κινητές υποδιαστολές σε ακέραιους χρησιμοποιώντας έναν παράγοντα κλίμακας. Η κβαντοποίηση βασισμένη στο εύρος υπολογίζει αυτόν τον παράγοντα βάσει των πραγματικών τιμών του αντικειμένου, πιθανώς αποκλείοντας τις ακραίες τιμές, ενώ άλλες μέθοδοι χρησιμοποιούν σταθερά ή εκμάθησης κατώφλια για το κλείσιμο των τιμών. Εμείς εφαρμόσαμε τον συνδυασμό των δύο και συγκεκριμένα συμμετρική κβαντοποιήση.

Με το precision scaling συμφωνούμε σε ένα trade off αξιοποιήσης πόρων και απόδοσης με την ακρίβεια του μοντέλου. Συγκρίνουμε το F-σκορ για inference σε όλο το dataset του αρχικού (float) μοντελου με τα αντίστοιχα fixed\_point και fixed\_int για 8,16,24 και βιτς. Για πλήθος 32 και 24 bits η ακρίβεια παραμένει σταθερή και για τι δύο αναπαραστάσεις. Όμως για 8 και 16 bits το fixed\_point μοντέλο χανεί σημαντικά την προβλεπτικη ικανότητα. Καλύτερη συμπεριφορά υποδεικνύει το κβαντισμένο μοντέλο. Για 16 bits πρακτικά μένει σταθερό το F-σκορ και για 8 bits μειώνεται ελάχιστα. Προχωρόντας παρακάτω εφαρμόσαμε precision scaling μόνο για 24 και 32 στους float\_fixed και 16,24 και 32 στους fixed\_int.

## 1.8 Πειραματική Αξιολόγηση

Πριν προχωρήσουμε στη πειραματική αξιολόγηση ωφείλούμε να εξηγήσουμε πως επιλέξαμε το μοντελο δηλαδη τον συνδιασμό εκτιμητών και αριθμό χαρακτηριστικών, για το οποίο κάναμε το hw εξερεύνυση όπως το περιγράψαμε στα κεφάλαια. Χρησιμοποιήσαμε μια ευριστική ευριστική για να καταλήξουμε σε ενα μοντέλο. Συγκεκριμένα για τα μοντέλα που εξετάσαμε κατά την εκπαίδευση και έιχαν F-σκορ '99 κάναμε hw emulation με παραμέτρους αρχητεκτονικής coarse grained parallel rf με RF\_SIZE=1 και χώρις precision caling. Από τις 37 παραγώμενες υλοποιήσεθς και βρήκαμε ποιά ήταν πάνω στο pareto front. Η ευριστική που χρησιμοποιήσαμε για καταλήξουμε στο βέλτιστο μοντέλο ήταν απο αυτά που βρίσκονται στο pareto front να διαλέξουμε εκείνο με υψηλότερο F-σκορ, όπου και ήταν το μοντέλο με 10 εκτιμητές εκπαιδευμένο με 32 χαρακτηριστικά.

Εξετάσαμε την επίδραση του precision scaling στην για την pipeline και parallel αρχιτεκτονική. Δηλαδή 10 εκτιμητές εκπαιδευμένους με 32 χαρακτηριστικά, με τα παραγόμενο μοντέλα να έχουν pipeline αρχιτεκτονική και parallel αρχιτεκτονική με 1,2,4,8,16 και 24 παράλληλα RFs . Επιπλέον εφαρμόσα μετατροπή από float 32 σε fixed\_float για 32 και 24 bits και σε fixed\_int για 32,24 και 16 bits.

Στο βοξ πλοτ συμπεριλάβαμε τις μετρήσεις για φλοατ και τους παραπάνω τύπους για πρεςισιον σςελινγ. Για μπορέσουμε να συμπτίξουμε σε μια μετρική την επίδραση του πρεςισιον σςαλινγ συλογικά στα ρεσουρςες του ΦΠΓΑ παραμετροπιήσαμε τον τύπο απο το εξής παπερ σύμφωνα με τον ακόλουθο τύπο. Αφαιρέσαμε το  $\Delta \Sigma \Pi$  υτιλιζατιον μιας και το μοντέλο μας δεν χρησιμοποιήσε καθόλου  $\Delta \Sigma \Pi$ ς.

Για να μπορέσουμε να συμπεράνουμε τα καλύτερα configurations λαμβάνοντας υπόψη το inference time και το resource utilization σχεδίασαμε pareto plots. Το y-axis παρέχει το inference time κάθε configuration και το x-axis το resource utilization. Επιλεξαμε να σχεδίασουμε μόνο για το BRAM μίας και είναι το πιο δομιναντ και εξαντλειται γρηγοροτερα. Σχεδίασαμε διαφορετικά διαγράμματα για κάθε μέγεθος εισόδου, ώστε να μπορούμε να βρούμε τα καλύτερα configurations για μικρά και μεγάλα test datasets. Όπως τα inputs sizes είναι 480,4800,48000,28334 (όλοκληρο το δατασετ). Επίσης συμπερίλαβαμε το unptomized RF design.

Στα pareto διαγραμματα σχεδιάσαμε και τα configurations που βρίσκονται στο pareto front. Από αυτό του pareto fronts σχετικά με το performance για όλες τις περιπτώσεις εκτός για μικρό input size 480 samples το πιο γρήγορο μοντέλο εχει pipeline αρχιτεκτονική. Σε δεύτερη θέση είναι το parallel μοντέλο με 24 παράλληλα RF. Κοινό χαρακτηριστικό σχεδόν όλων των configurations στα pareto fronts είναι ότι εκείνα που είναι πιο γρήγορα και έχουν χαμηλότερο BRAM utilization έχει εφαρμοστεί precision scaling με integer 16 bits. Συμπεραίνουμε ότι η εφαρμογή του precision scaling έχει σημαντική επίδραση στην μείωση των πόρων αλλά βελτιώνει το performance. Για την σύγκριση με c++ και python επιλέγουμε τα γρηγορότερα configurations από τις δύο αρχιτεκτονικές δηλαδή pipeline fixed integer 16 bits και parallel 24 rf integer 16 bits.

Από τα πειράματα μας μπορούμε να εξάγουμε χρήσιμα συμπεράσματα για την χρησιμότητα της hw επιτάχυνσης. Για όλα τα μεγεθή εισόδων καταφέρνουμε να πετύχουμε επιτάχυνσης. Την μικρότερη επιτάχυνσης 1.5 την έχουμε για το μικρό μέγεθος dataset (480 δείγ-

ματα) σε σύγχριση με το inferece σε c++. Η ειχόνα αυτή αλλάζει όσο μεγαλώνει το μέγεθος εισόδου. Για όλες τις υπόλοιπες περιπτωσεις 4800,48000 δείγματα και όλοκληρο το dataset καταφέρνουμε να πετύχουμε πολύ καλύτερή επιτάχυνση. Το καλύτερο ςονφιγυρατιον για αυτά μεγέθη είναι η pipeline αρχιτεκτονική με precision scale integer σε 16 bits, με μόνη εξαίρεση τα 480 δείγματα όπου η parallel υλοποιήση 24 RF πετυχαίνει καλύτερο χρόνοο.Πίο είδικα το speed up που πετύχαμε φαίνεται στον πίνακα. Ενδιαφέρον έχει ότι για inference σε python ο χρόνος μένει πρακτικά σταθερός γύρω στα 140 ms. Λόγω αυτού όσο μεγαλώνει το μέγεθος του test για evaluation το inference time της python προσεγγίζει αυτό της c++, με την περίπτωση για περισσότερα από 48000 να έχει καλύτερη απόδοση. Οι υλοποιήσεις μας κάθε φορά συγκρίνονται με το γρήγορο από τα δύο (c++,python) και αντίστοιχα προκύπτει το ανάλογο speed up. Το καλύτερο speed up 20,03 το πετυχαμε για 48000 δείγματα.

| input size | compare to | native time(ms) | best fpga time(ms) | speed up |

|------------|------------|-----------------|--------------------|----------|

| 480        | c++        | 1.47            | 0.99               | 1.5      |

| 4800       | c++        | 14.07           | 1.64               | 8.6      |

| 48000      | python     | 141.61          | 7.07               | 20       |

| 288344     | python     | 141.8           | 37.15              | 3.8      |

Table 1: Achieved speed up.

Όλα τα παραπάνω μας οδηγούν στα εξής συμπεράσματα ότι για μικρά input sizes γύρω στα 500 samples δεν έχουμε σημαντικά οφέλη από το hw acceleration. Το μέγεθος είναι αρχετα μιχρό ώστε το transfer time overhead από το host στο fpga να υπερτερεί οποιουδήποτε acceleration που πετυχαίνουμε χάρις στην παραλληλία των υλοποιήσεων μας. Θα μπορούσε σε αυτή την περίπτωση το inference να γίνει natively σε c++ χωρίς κάποια σημαντική διαφορά. Όσο μεγαλώνει το input size είναι ξεκάθαρο ότι το παραπάνω overhead σκίαζεται από τα acceleration που πετυχαινουμε. Το ιδανικό input size έιναι γύρω στα 50000 samples όπου και τα μοντέλα μας επιδυκνύουν και το καλύτερο performance. Τέλος για input sizes πολλαπλάσια όλοχληρου του dataset είναι πιθανόν η python υλοποιήση να πετυχαίνει καλύτερα αποτελέσματα λόγω του batch processing . Όμως λίγες μπορούμε να φανταστούμε είναι οι περιπτώσεις όπου θα χρειαστεί να γίνει inference σε τόσο μεγάλο dataset για security critical introduction detection εφαρμογές όπως αυτή που εξετάσαμε σε αυτη την διπλωματική ερ-

#### 1.9 Συμπεράσματα και Μελλοντική Εργασία

Στα πλαίσια αυτής της διπλωματικής εργασίας εξέτασαμε τον αλγόριθμο μηχανικής μάθησης Random Forest για να κάνουμε Anomaly detection σε Βιομηχανικές Εγκαταστάσεις. Ερευνήσαμε τρόπους με τους οποίους μπορούμε να πετυχουμε hardware acceleration σε FPGA του RF κατα το inference. Εντοπίσαμε τα κομμάτια του αλγορίθμου που μπορούμε να επιταχύνουμε και να παραλληλοποιήσουμε εκμεταλλευόμενοι τις δυνατότητες τις δυνατότητες του FPGA. Τα decision trees που απαρτίζουν το RF ειναι ανεξαρτητα μεταξυ τους και μπορούν να παραλληλοποιηθούν. Στηριζόμενοι σε αυτή την ιδιότητα προτείναμε δύο διαφορετικές αρχιτεκτονικές τις Coarse grained Parallel RFs και Pipeline RF, στο εσωτερικό και των δύο οι estimators εκτελούνται παράλληλα. Στην πρώτη έχουμε πολλαπλά αντίγραφα του ίδου RF, εισάγοντας ένα δεύτερο παραλληλίας αυτό την παράλληλης ταυτόχρονης επεξεργασίας πολλαπλών δειγμάτων εισόδου, ίσο σε αριθμο με αυτών των αντιγράφων. Στη δεύτερη αρχιτεκτονική ακολουθήθηκε pipeline προσέγγιση όπου ύστερα από ένα αρχικό latency επιτυγχανεται iteration interval II=1, δηλαδή παραγωγή ενός νέου classification σε κάθε νέο κύκλο. Επιπλεον εισάγαμε την τεχνική βελτιστοποίησης precision scaling με σχόπο να μειώσουμε το resource utilization και καθώς και το inference time. Συγκρινόμενοι κάθε φορά με την πίο γρήγορη υλοποίηση του RF που έτρεχε natively σε C++ και Python καταφέραμε να πετύχουμε acceleration για όλα τα samples sizes που δοχιμάσαμε. Το χαλύτερο speed up που μετρήσαμε ήταν 20 για 48000 samples. Παράγων της διπλωματικής εργασίας ήταν η δημιουργία ενός εργαλείου για την αυτοματοποίση της διαδικασίας design exploration σε FPGA, απαιτώντας ελάχιστη αλλεπίδραση με τον χρήστη.

Σε μελλοντική εργασία, επιθυμούμε να ευρήνουμε περισσότερες τεχνικές για acceleration σε ΦΠΓΑς ή ακόμη διαφορετικές hardware πλατοφορμες όπως τα embedded fpgas. Η έρευνα της διπλωματικής εύκολα μπορεί να μεταφερθεί και σε eFPGA, τα οποία αποκτούν δημοφιλία σε πληθώρα εφαρμογών στενα συσχετιζόμενη με την δική μας όπως είναι το edge computing. Μια άλλη ενδιαφέρουσα μελέτη θα μπορούσε να αποτελεί το acceleration ενός άλλου tree structure machile learning αλγορίθμου κατάλληλο για anomaly detection τα Isolation Forests. Τα IF θυμιζουν αρκετα το RF με την βασικότερη διαφορά τους ότι

μπορούν να κάνουν και unsupervised anomaly detection. Ενδιαφέρον θα ήταν η σύγκριση των δύο αλγοριθμων σε hw acceleration performance αλλα και προβλεπτική ικανότητα. Συμπέρασμα αυτής της διπλωματιής εργασίας είναι ότι τα πεδία του HW accelartion και Anomaly detection διαρκώς αναπτύσσονται και θα μας απασχολούν σίγουρα και στο μέλλον.

#### 2 Introduction

In recent years, it has been observed that more and more Industrial Facilities are becoming the target of attacks. Many of these systems were not designed with security in mind. Until recently, operation technologies were separated from information technologies. In addition, specialized knowledge was required to handle and properly operate them[7]. Because of this, industrial plants were safer than they are today. The ever-increasing growth and demand for Internet of Things(IoT) technology has reinforced the above phenomenon. Despite the clear benefits, in terms of productivity, efficiency and automation, offered by IoT integration and interconnection of systems, there is a risk of exposing more vulnerabilities.

In order to protect industrial facilities from attacks, we need to quickly detect them and develop deterrents. The aim of this thesis is to accelerate the inference stage of a predictive model that detects cyber-physical attacks to a Secure Water Treatment Facility. To achieve this we apply Anomaly Detection utilizing machine learning algorithms such as Random Forest ensemble. We chose to accelerate the generated model on a FPGA device with the help of Vitis HLS tool.

Anomaly detection, also known as outlier detection, refers to the problem of finding patterns in data that do not conform to expected behavior [1]. We focus mainly at intrusion detection, the process of identifying hostile activity (break-ins, penetrations, and other types of computer abuse) in a system [1]. Using historical data we train the Random Forest model to make such predictions. Random Forest is a supervised learning algorithm which consists of a collection of Decision Trees. Each Decision Tree is trained independently of the others on a subset of the original dataset. To obtain a prediction, each tree independently makes its own prediction and then these are aggregated. In our case we are interested in classification, the final prediction is extracted by majority voting.

One of the main challenges related to anomaly detection implementation is fast and reliable inference. In our thesis we propose to use Field Programmable Gate Arrays (FPGA) and the Vitis-HLS tool-chain. The parallelism capabilities offered by FPGAs allows us to significantly reduce the inference time, which is essential for security critical applications like ours. Furthermore, through Vitis

we can write our code in a high-level language like C++ rather than a hardware description language such as Verilog or VHDL. It provides us with the flexibility and convenience to be able to focus on improving the design and the structure of the algorithm rather than on low-level implementation.

In the context of this thesis, we explored the possibility of parallelizing the RF algorithm to achieve acceleration. Inside an RF, each Decision Tree operates independently from the others, constituting the first level of parallelism we leveraged. To achieve this, we created different instances for each Decision Tree in the hardware, enabling their parallel execution. We also investigated higher levels of parallelism, specifically parallel processing of multiple input samples. We proposed two different architectures. The first one, named Coarse-Grained Multiple RF, involves instantiating multiple copies of the same RF, with each containing parallel decision tree estimators. This allows us to implement, for example, K parallel RFs, each with N parallel Decision Trees, internally evaluating K inputs simultaneously. It's clear that there is a trade-off between performance and resource utilization, for which we conducted an analysis.

The second proposed architecture is called Pipelined RF. We observed that the process of traversing a Decision Tree can be fragmented into individual sequential stages. While there's a dependency between the stages, by inserting buffers between them, we managed to transform the process into a pipeline. We combined parallel and independent pipelined Decision Trees to achieve a highlevel Pipelined RF. The Pipelined RF can accept new input samples in each cycle, which are then propagated through the pipelined stages of each Decision Tree, achieving an initial Iteration Latency and then reaching an Iteration Interval of II=1.

In both architectures, we applied precision scaling techniques to achieve better performance during inference and lower resource utilization. Precision scaling is the technique of representing model elements in a different and lower precision format. We experimented with different numbers of bits lengths and data types beyond floating-point, such as fixed floats and integers. In the case of integers, we needed to apply quantization.

Having the two architectures and the aforementioned microarchitectural optimization techniques, we conducted hardware design exploration to find the best configurations for comparison with C++ and Python implementations of the RF algorithm. We analyzed the findings from these comparisons and presented our conclusions in detail. A byproduct of this thesis is the creation of a framework tool capable of automating the design exploration process. The contribution of this thesis lies in the study of novel techniques for accelerating the RF algorithm on FPGA and providing the aforementioned tool.

The rest of the thesis has the following structure. In chapter 3 we report on related work on Anomaly Detection and acceleration in FPGA. We make an extensive analysis of the Random Forest algorithm and compare it with other state of the art classifiers. We also analyze the structure and the capabilities of the FPGA in relation to other platforms and the operation of the Vitis HLS. In chapter 4, we present the dataset we used and the methodology we followed to produce the first executable on FPGA. In chapter 5, we present the two architectures parallel and pipeline we implemented and the HLS directives we used to achieve the best predictive accuracy with maximum acceleration and lowest resource usage. In chapter 6, we present micro architectural optimizations, such as precision scaling, we applied to improve further the aforementioned architectures regarding the performance and resource utilization. In chapter 7 we present a framework that was produced through the thesis in order to automate the design exploration process in FPGA for the random forest algorithm. In chapter 8 we analyse the results from the design exploration of the previous chapters and we select the best ones implementations to compare with the equivalents C++ and Python that run natively. Finally, in chapter 9 we summarize with our conclusions and discuss further ideas for future optimizations.

### 3 Theoretical Background

#### 3.1 Related Work

Anomaly detection is a widely found issue. Many different approaches have been tried in an attempt to develop a reliable model. One of them involves the comparison of Support Vector Classifires(SVM) and Random Forest(RF)[8]. Simon D. Duque Anton used 2 different datasets involving intrusion detection in industrial facilities. They also did feature selection in order to keep the most important features, with the aim of reducing training time while maintaining a relatively high accuracy rate. There is no straight forward solution in finding those features that are able to distinguish between malicious and no malicious instances. One suggested heuristic is the feature importance metric of RF, which shows us the importance of a feature according to its ability to increase the pureness of the leaves. The authors of the paper concluded that RF achieved significantly better performance and accuracy than SVM and had more linear behavior with respect to run-time.

A similar study [9] comparing SVM and RF for ID on the KDD99 dataset had different conclusions. Specifically, RF achieves better prediction for specific type of attacks such as probing and U2R and has higher precision than SVM. However, SVM has overall slightly better accuracy and lower False Negative Rate(FNR). Both of papers agree that RF is faster at training and running.

In another study [10], they sought to develop an intelligent and secure model to detect vulnerabilities in IoT systems and protect against cyber-attacks. To achieve this, they compared several different machine learning algorithms. In total 5 were used, which were Logistic Regression(LR), Support Vector Machine, Decision Trees(DT), Random Forest and Artificial Neural Networks (ANN). They concluded that a simple model like RF can, always depending on the dataset, bring better results in terms of prediction accuracy compared to much more complex ones like ANN.

It is evident that RF, thanks to its good accuracy and fast training and running times, is a popular choice in the field of anomaly detection. However, there is always a need for more precise, faster, and energy-efficient solutions. Therefore, efforts have been made to accelerate the model on a variety of hardware platforms such as GPUs and FPGAs. One such approach is presented in a paper

[11]that utilizes a variant of the classic RF algorithm called Compact Random Forest (CRF). The main differences lie in the number of decision trees (DT) and the maximum depth allowed for each tree to grow. These changes are motivated by the fact that the RF algorithm is memory-bound, which is not ideal for hardware acceleration with limited resources.

Regarding FPGA implementation, a pipeline architecture is suggested with n different pipelines for n trees. Each pipeline consists of s stages, where each stage represents the node that the sample traverses in the corresponding tree. In the s-1 stage, the classification of the sample by the tree takes place. The last stage of the design is the majority voting from all the pipelines. This particular implementation achieves processing of each sample in every clock cycle, meaning an Iteration Interval (II) of 1.

In the CP-GPU implementation, the focus is on maximizing the utilization of parallelism in multicores and achieving optimal data reuse in the caches. To achieve this, each streaming multiprocessor selectively traverses a subset of trees from the forest for each sample. The study concludes that FPGA provides higher performance/performance per watt and can handle larger classifiers without compromising its capabilities, with the necessary hardware resources. On the other hand, CP-GPU offers better cost-effectiveness in terms of efficiency per dollar, although it experiences a significant reduction in its performance when dealing with the maximum size of the Compact Random Forest (CRF). However, the CP-GPU implementation allows for easier scalability.

Based on the previous work, we have decided to perform Anomaly Detection (AD) using Random Forest (RF) on an FPGA. However, we have made some differences compared to [11]. Firstly, we will not impose any restriction on the size of the RF during training. Additionally, we will compare two different architectures on the FPGA. One architecture is a pipeline approach, similar to the one proposed in the paper, while the other involves a more parallel implementation.

Thanks to the increased capabilities of modern FPGAs, we will aim to achieve the maximum possible number of parallel and independent RF instances that can fit on the board. All instances will be identical copies of each other. Internally, the trees will process each sample in parallel in both proposed architectures. Our goal is to compare which of the two approaches, pipeline or parallel, will provide us with higher performance and to examine the trade-off between resources and performance.

#### 3.2 Random Forest Algorithm

The RF algorithm was first proposed by Leo Breiman. It combines multiple techniques and introduces new ones. It is a variation of the CART algorithm, in which bagging and random feature selection are applied.

First, let's analyze the Classification And Regression Tree (CART) algorithm [12], which consists of 4 basic steps. In the first step, we start from the root and construct the tree by recursively creating nodes and splitting the data. Each node acquires a class based on the distribution of classes in the learning data at that node, as well as the decision cost matrix, regardless of whether the node will be further split or not. The importance of the label of all node will evident at the analysis of stage 3. One of the most common criteria used to find the optimal splitting variable in a node is the Gini index. The Gini index measures the degree or probability of a particular variable being wrongly classified when randomly chosen. It takes values from 0 to 1. If all elements belong to a single class, the index has a value of 0 and is considered pure. Conversely, if the elements are randomly distributed across classes, the index has a value of 1 and is considered impure. As expected, in each node, the feature and value that give us the lowest Gini index are selected. The formula for calculating the Gini index is as follows.

$$Gini = 1 - \sum_{i=1}^{n} (pi)^2$$

(1)

'pi' is the probability of an object being classified to a particular class.

The second stage is the stopping of tree building. This occurs under 3 conditions:

- there is only one instance in a child node

- there many instances at a child node but all of them have the same classification

- the maximum number of nodes has been reached

In the third stage, we proceed with pruning the tree. The maximal tree always has better accuracy on the learning data, which is why there is a risk of overfitting. The purpose of pruning is to obtain simpler trees that can distinguish the correlations between the data and the noise. The technique used is called 'cost-complexity' pruning. Starting from the leaves, we remove nodes and compare the drop in accuracy relative to the complexity of the tree. In the fourth and final stage, we select the optimal tree that resulted from the pool of trees in the third stage. This is usually done by using a different dataset from the training dataset.

The CART algorithm, however, is prone to overfitting the data and performs poorly with outliers. Breiman proposed using the technique called bagging, also known as bootstrap aggregating. In bagging, multiple weak learners are trained in parallel, each on a different dataset generated by random redistribution of the original dataset. The training dataset for each learner (classifier or regressor) is created by randomly selecting N samples with replacement, where N is the size of the original dataset. The goal is to train each tree with a different dataset, to make the model more robust to new samples.

In most datasets, there are certain features that appear to be more influential than others in making decisions regarding node splitting and, consequently, in constructing decision trees. Even with the use of bootstrap sampling, it seems that the generated trees do not differentiate themselves enough to effectively address overfitting. Breiman attempted to introduce more randomness into the model with the goal of reducing the correlation between trees and either increasing or maintaining their predictive ability. He proposed that instead of using the entire range of features at each node, a random subset of features should be utilized. The feature and its corresponding value for splitting the node are selected from this random subset. The number of features considered in this process remains constant for all nodes and all trees, and it is typically a function of the total number of features. One commonly used approach is to select the square root of the total number of features, while another widely employed method is to take the logarithm.

This inclusion of bagging and random feature selection helps to introduce diversity among the trees and enhance the model's ability to generalize, thus addressing the issues of overfitting and improving overall performance.

The inference process of a RF is the following:

- Input: For each given X sample which we want to make a prediction, the RF takes this feature vector as input.